JAJS261B July 2007 – January 2018 DAC8881

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

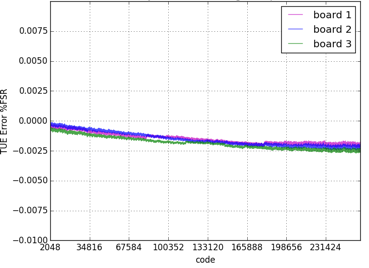

8.2.1.3 Application Curves

Glitch reduction and total unadjusted error (TUE) plots of the solution presented in Sample & Hold Glitch Reduction for Precision Outputs Design Guide (TIDU022) is shown in the following plots. The glitch area is reduced from 35.11 nVs to 2.01 nVs.

| CH = 8.2 nF | RS = 14.7 Ω |

(20000h-1FFFFh 18-bit Data)

(Top) Digital Signal One-Shot Pulse; (Middle) DAC Output Glitch; (Bottom) S&H Output Glitch