JAJSPX6A August 2017 – February 2023 DLP650NE

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Storage Conditions

- 6.3 ESD Ratings

- 6.4 Recommended Operating Conditions

- 6.5 Thermal Information

- 6.6 Electrical Characteristics

- 6.7 Timing Requirements

- 6.8 Window Characteristics

- 6.9 System Mounting Interface Loads

- 6.10 Micromirror Array Physical Characteristics

- 6.11 Micromirror Array Optical Characteristics

- 6.12 Chipset Component Usage Specification

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Optical Interface and System Image Quality Considerations

- 7.6 Micromirror Array Temperature Calculation

- 7.7 Micromirror Landed-On or Landed-Off Duty Cycle

- 8 Power Supply Requirements

- 9 Device Documentation Support

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- FYE|350

サーマルパッド・メカニカル・データ

発注情報

3 概要

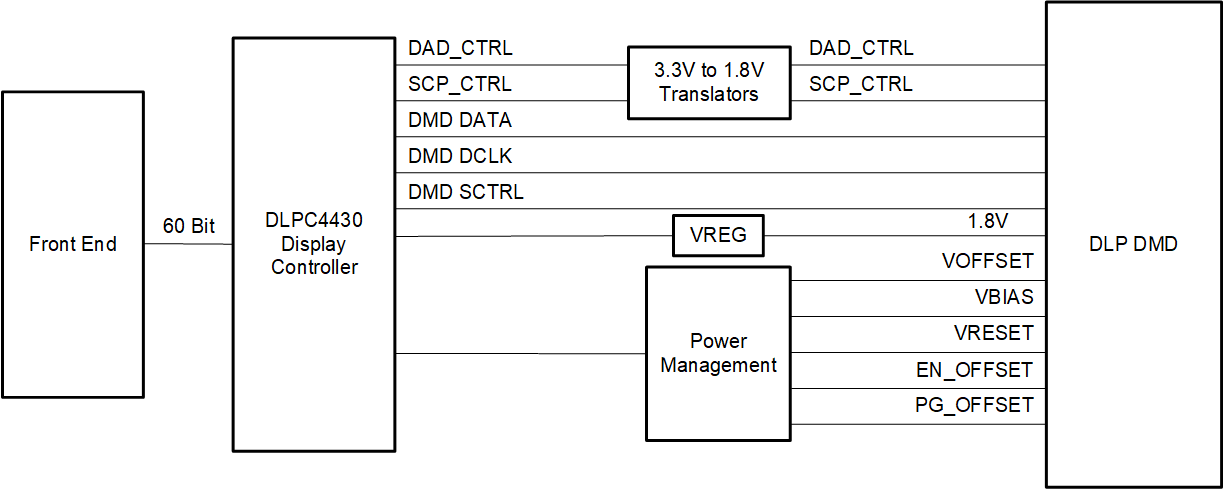

テキサス・インスツルメンツの DLP650NE デジタル・マイクロミラー・デバイス (DMD) は、デジタル制御型の MEMS (micro-electromechanical system) 空間光変調器 (SLM) で、色鮮やかなDLP® 0.65 1080p ディスプレイ・ソリューションを低コストで実現します。DLP650NE DMD—は、DLPC4430 ディスプレイ・コントローラおよび DLPA100 パワー・マネージャおよびモーター・ドライバ—と組み合わせて使用することで、高性能システムを実現できます。また、高解像度と 16:9 のアスペクト比、高輝度、およびシステムの簡素化を必要とするディスプレイ・アプリケーションに最適です。

製品情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| DLP650NE | FYE (350) | 35.0mm × 32.2mm × 5.1mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

DLP650NE のアプリケーション概略図

DLP650NE のアプリケーション概略図