DLPS082 February 2017 DLPA100

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DLP|48

サーマルパッド・メカニカル・データ

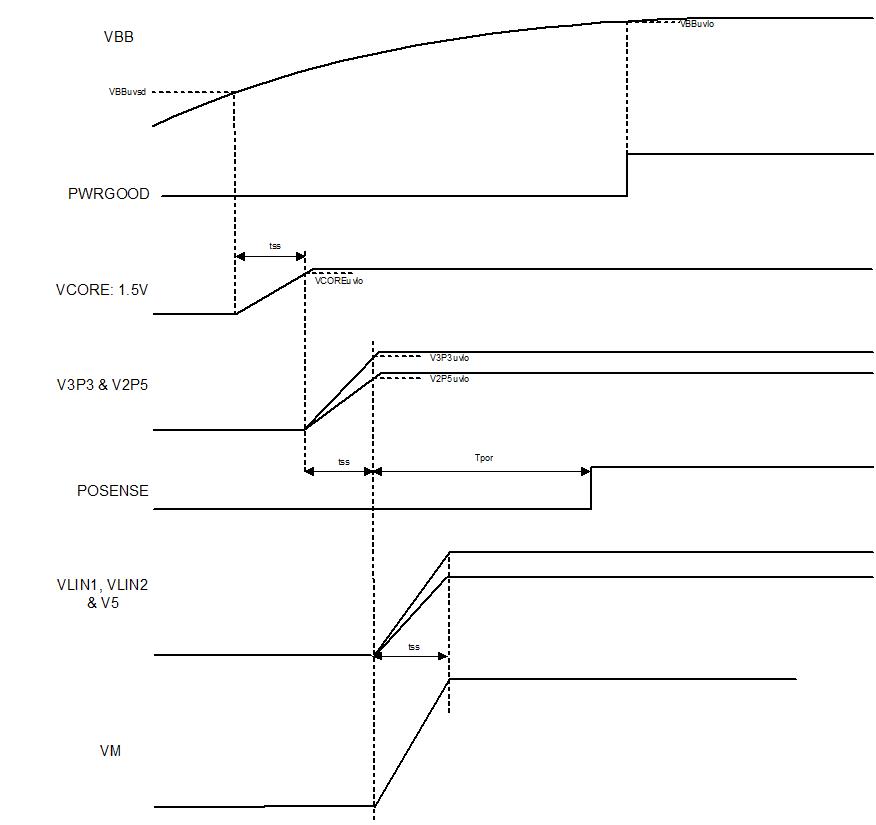

7.3.1 Power Up Sequencing

Once the VBB voltage reaches the VBBuvsd threshold (specification defined in Shutdown), the VCORE channel soft-starts within a period of 5 ms typical (tss). Once this period is completed and the VCOREuvlo has been reached, the V3P3 and V2P5 rails soft-start, ramping up ratiometrically. Once each of the three rails are above their respective undervoltage lockout levels (VCOREuvlo, V3P3uvlo, V2P5uvlo), the POSENSE flag will go high after a period of 150 ms typical (Tpor) and also, the VLIN1, VLIN2, V5 and VM rails soft-start, ramping up ratiometrically. Note that VLIN1, VLIN2, V5 and VM can be individually disabled via the serial port, although VLIN1 and VLIN2 require V5 to be present.

The PWRGOOD flag will go high once the POSENSE is high and the VBB voltage is above the undervoltage lockout threshold VBBuvlo.

Figure 1. Power Up Sequencing Timing Diagram

Figure 1. Power Up Sequencing Timing Diagram