JAJSLO8C December 2020 – November 2022 DP83TG720R-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 デバイス比較表

- 6 ピン構成および機能

- 7 仕様

-

8 詳細説明

- 8.1 概要

- 8.2 機能ブロック図

- 8.3 機能説明

- 8.4

デバイスの機能モード

- 8.4.1 パワーダウン

- 8.4.2 リセット

- 8.4.3 スタンバイ

- 8.4.4 通常

- 8.4.5 スリープ

- 8.4.6 状態遷移

- 8.4.7 MDI (Media Dependent Interface)

- 8.4.8 MAC インターフェイス

- 8.4.9 シリアル・マネージメント・インターフェイス

- 8.4.10 ダイレクト・レジスタ・アクセス

- 8.4.11 拡張レジスタ・スペース・アクセス

- 8.4.12 書き込みアドレス動作

- 8.4.13 読み出しアドレス動作

- 8.4.14 書き込み動作 (ポスト・インクリメントなし)

- 8.4.15 読み出し動作 (ポスト・インクリメントなし)

- 8.4.16 書き込み動作 (ポスト・インクリメントあり)

- 8.4.17 読み出し動作 (ポスト・インクリメントあり)

- 8.5 プログラミング

- 8.6 レジスタ・マップ

- 9 アプリケーションと実装

- 10電源に関する推奨事項

- 11テキサス・インスツルメンツの 100BT1 PHY との互換性

- 12レイアウト

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

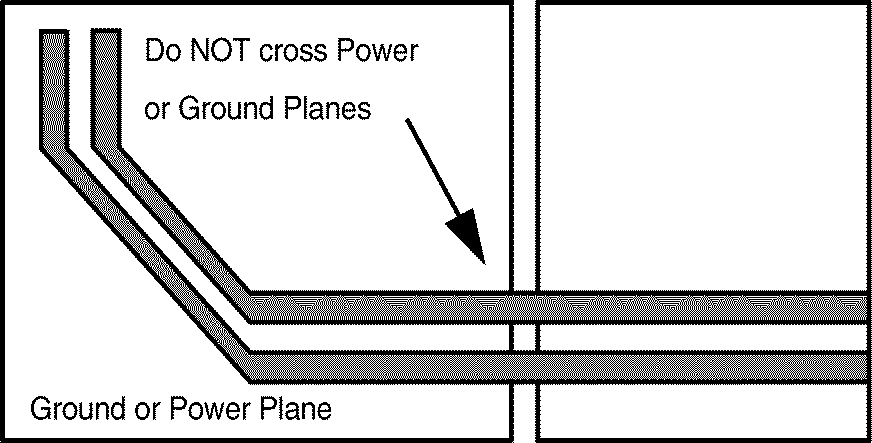

12.1.2 復帰パス

一般に最も良い方法は、すべての信号トレースの下にベタの復帰パスを設けることです。この復帰パスは、連続的なグランドまたは DC 電源プレーンであってもかまいません。復帰パスの幅を狭くすると、信号トレースのインピーダンスに影響を及ぼす可能性があります。この影響は、復帰パスの幅が信号トレースの幅と同等である場合、より顕著になります。信号トレースの間の復帰パスの断線は、絶対に避ける必要があります。分割されたプレーンをまたぐ信号は、予測不可能な復帰パス電流を引き起こす可能性があり、信号の品質に影響を及ぼし、放射の問題を引き起こすこともあります。

図 12-2 電源およびグランド・プレーンの割れ目

図 12-2 電源およびグランド・プレーンの割れ目