JAJS617C July 1999 – July 2016 DS90LV048A

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

1 特長

- 400Mpbs (200MHz)を超えるスイッチング速度

- フロースルーのピン配置によりPCBレイアウトを簡素化

- チャネル間スキュー: 150ps (標準値)

- 差動スキュー: 100ps (標準値)

- 最大伝搬遅延: 2.7ns

- 3.3V電源の設計

- 電源オフ時にLVDS入力が高インピーダンス

- 低消費電力の設計(3.3V静的で40mW)

- 既存の5V LVDSドライバと相互運用可能

- 小振幅(標準値350mV)の差動信号レベルを許容

- 入力フェイルセーフのサポート

- オープン、短絡、および終端

- 0V~−100mVのスレッショルド領域

- ANSI/TIA/EIA-644規格に準拠

- 動作温度範囲: -40℃~85℃

- SOICおよびTSSOPパッケージで利用可能

2 アプリケーション

- マルチファンクションのプリンタ

- LVDS - LVCMOS変換

3 概要

DS90LV048Aデバイスは、クワッドCMOSフロースルー差動ライン・レシーバで、非常に低い消費電力と高いデータ速度を必要とするアプリケーション用に設計されています。このデバイスは、低電圧差動信号(LVDS)テクノロジを活用し、400Mbps (200MHz)を超えるデータ転送速度をサポートするよう設計されています。

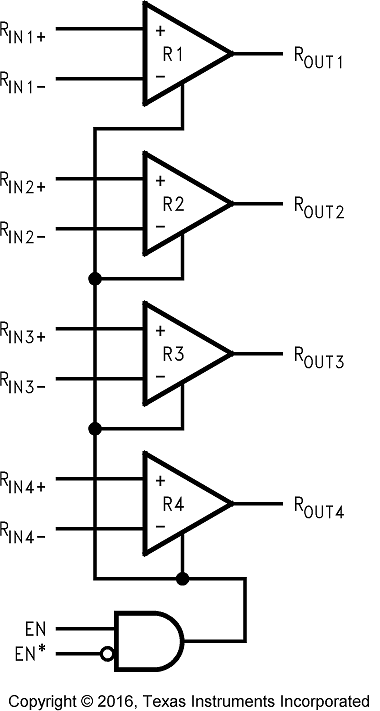

DS90LV048Aは低電圧(標準値350mV)の差動入力信号を受け付け、3V CMOS出力レベルへ変換します。レシーバはTRI-STATE機能をサポートしており、出力の多重化に使用できます。また、レシーバはオープン、短絡、終端(100Ω)の入力フェイルセーフもサポートします。すべてのフェイルセーフ条件において、レシーバの出力はHIGHになります。DS90LV048Aはフロースルーのピン配置を採用しているため、PCBレイアウトが簡単になります。

ENおよびEN*入力は互いにAND接続され、TRI-STATE出力を制御します。イネーブルは4つのレシーバすべてに共通です。DS90LV048AおよびコンパニオンLVDSライン・ドライバ(例: DS90LV047A)は、大電力のPECL/ECLデバイスの新しい代替品として、高速のポイント・ツー・ポイント・インターフェイス・アプリケーションに使用できます。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| DS90LV048A | SOIC (16) | 9.90mm×3.91mm |

| TSSOP (16) | 5.00mm×4.40mm |

- 提供されているすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

機能図