JAJSFF3B November 2020 – April 2021 INA849

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 デバイス比較表

- 6 ピン構成および機能

- 7 仕様

- 8 詳細説明

- 9 アプリケーションと実装

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

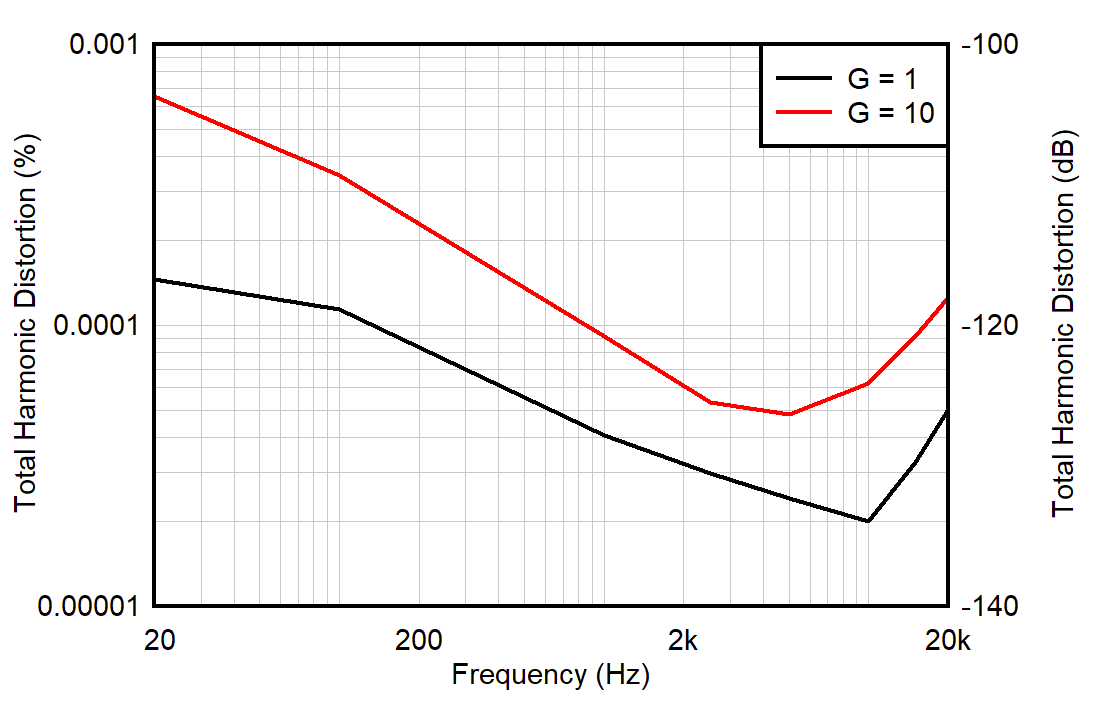

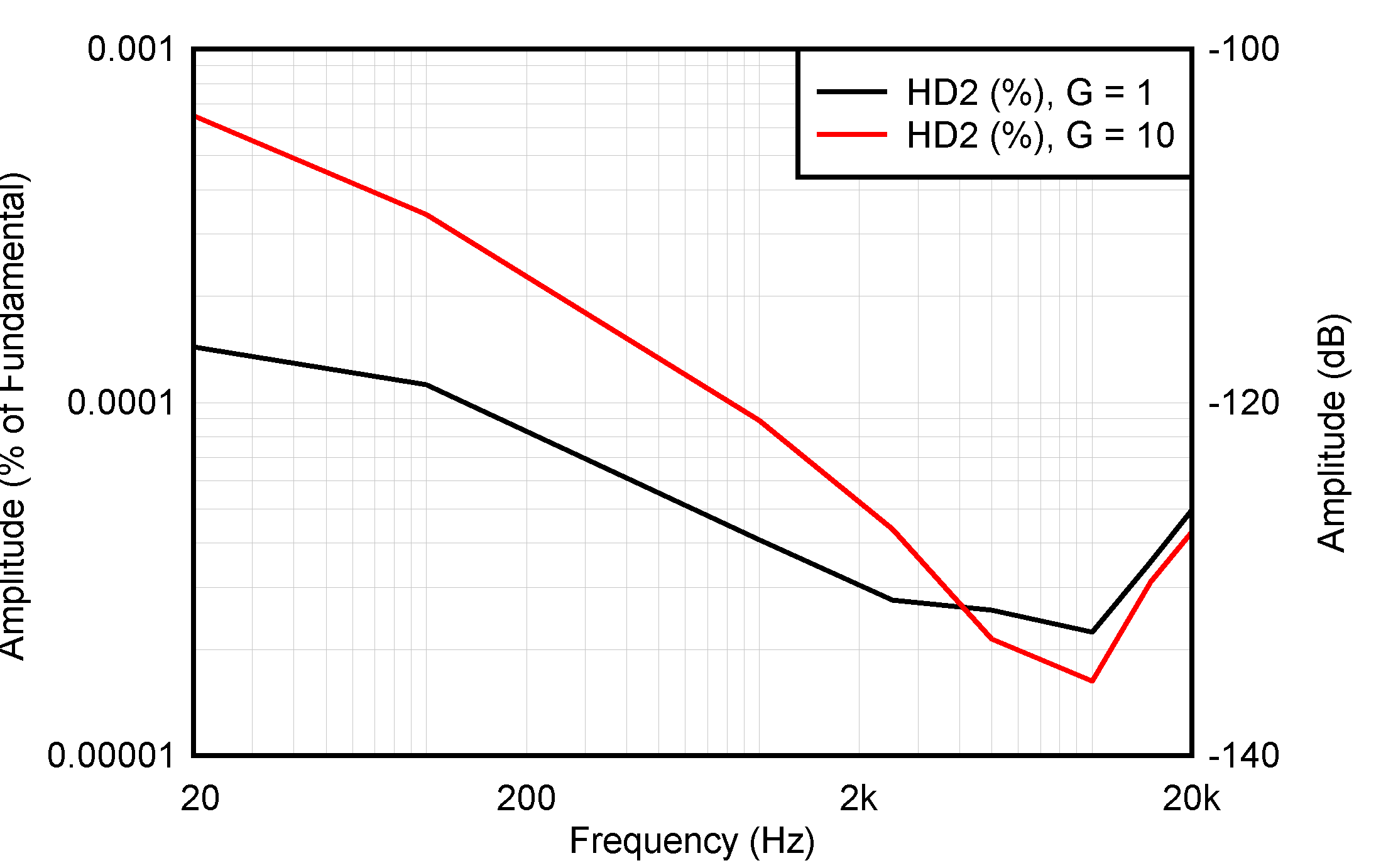

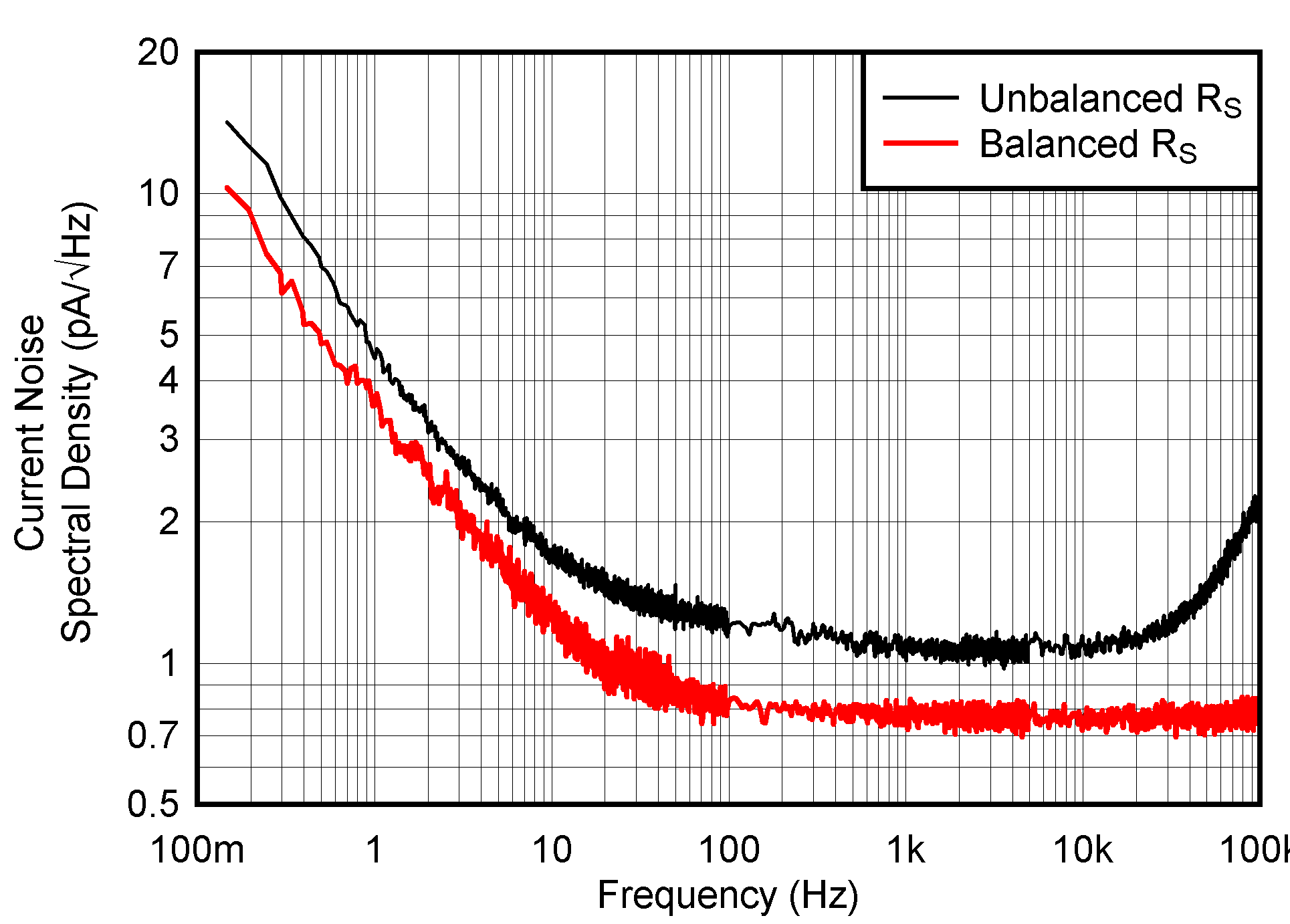

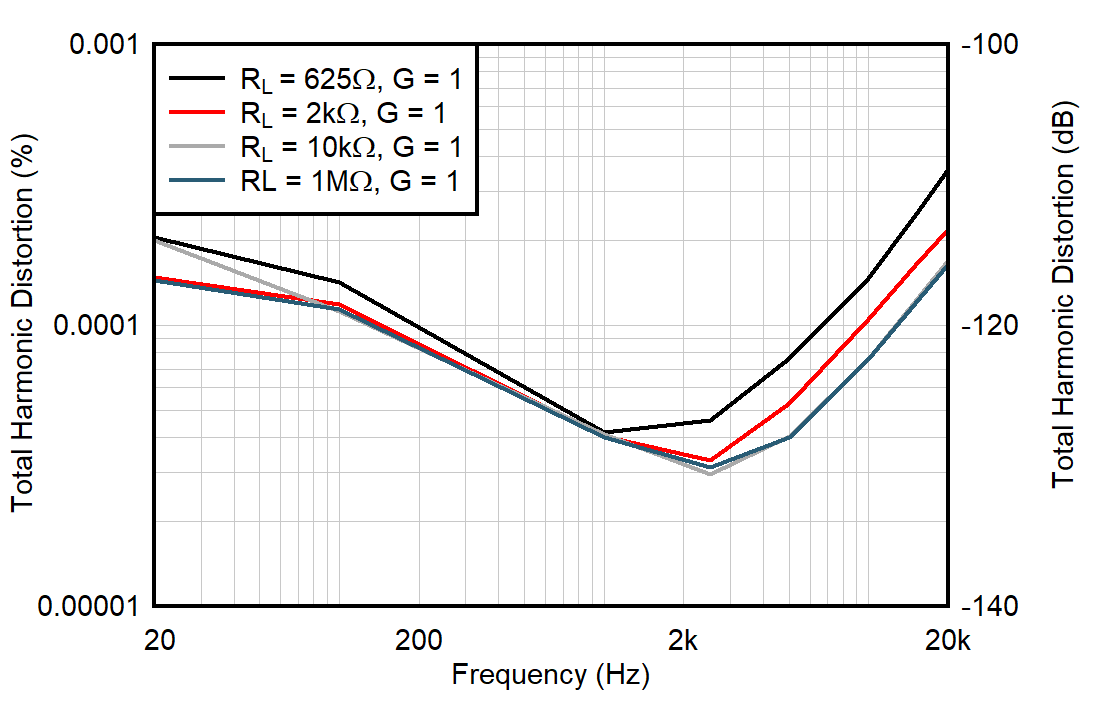

7.6 代表的特性

TA = 25℃、VS = ±15V、中電圧での VCM、VRL = 10kΩ、グランドに接続、VREF = 0V、および G = 1 (特に記述のない限り)

| N = 1695、平均 = 0.26µV、標準偏差 = 5.85µV |

| N = 1695、平均 = -43.83µV、標準偏差 = 111.74µV |

| N = 120、平均 = 7.58nA、標準偏差 = 1.84nA |

| N = 120、平均 = -0.11nA、標準偏差 = 1.01nA |

| N = 120、平均 = -0.375µV/V、標準偏差 = 0.043µV/V |

| N = 120 |

| G = 1000 |

| G = 1 |

| G = 1、CL = 100pF |

| G = 100、CL = 100pF |

| G = 1 | VSTEP = 10V |

| G = 1000 | VSTEP = 10V |

| N = 30、平均 = 0.10µV/℃、標準偏差 = 0.08µV/℃ |

| N = 120、平均 = -4.14µV/℃、標準偏差 = 2.00µV/℃ |

| N = 120、平均 = 7.24nA、標準偏差 = 1.80nA |

| N = 120、平均 = 3.08µV/V、標準偏差 = 5.57µV/V |

| N = 120 |

| VREF = 0V |

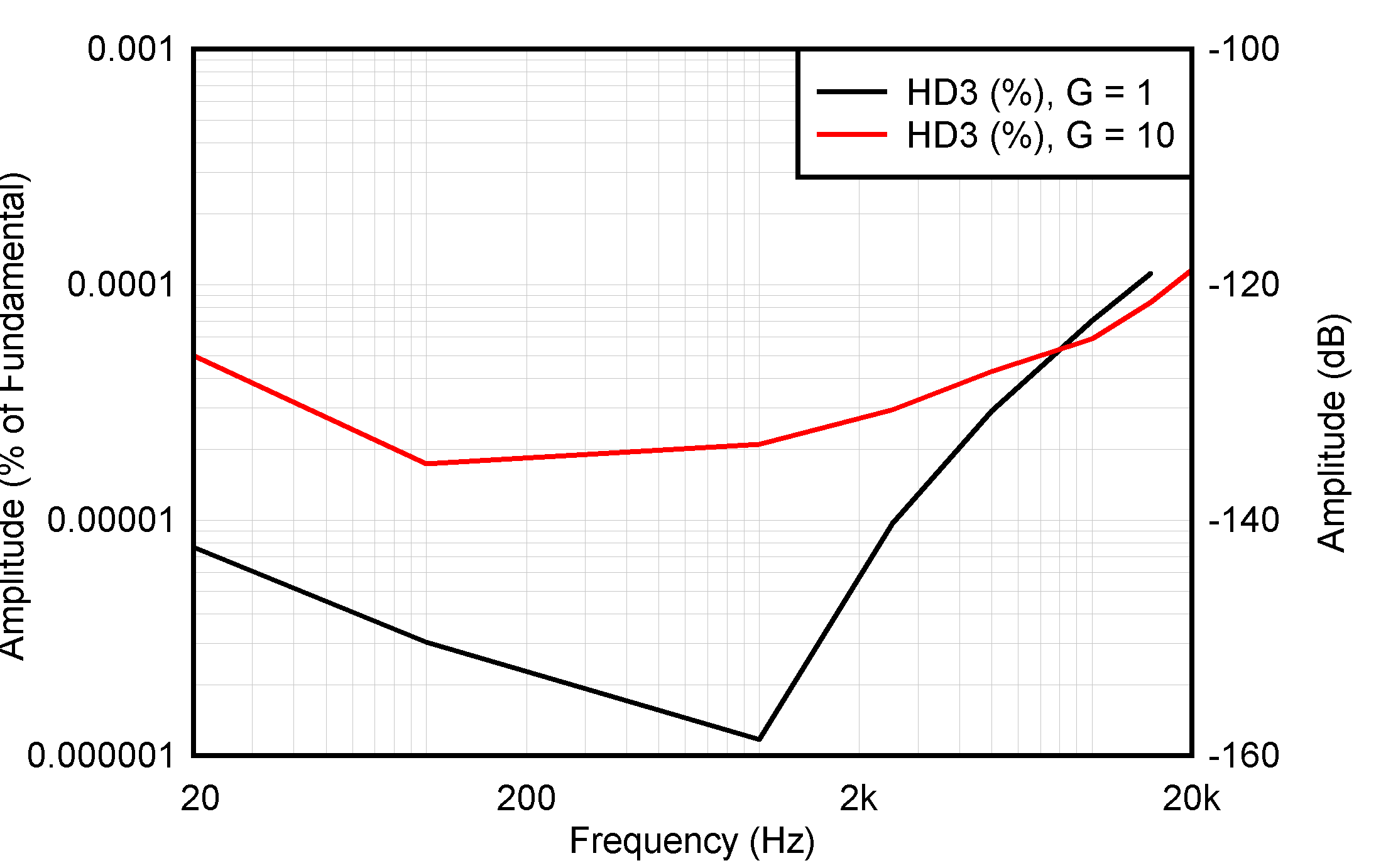

| G = 1 |

| G = 10 |

| G = 10、CL = 100pF |

| G = 1000、CL = 100pF |

| G = 100 | VSTEP = 10V |