JAJSVN0E July 2009 – November 2024 ISO7220A-Q1 , ISO7221A-Q1 , ISO7221C-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions

- 5.3 Safety-Related Certifications

- 5.4 Thermal Information

- 5.5 Safety Limiting Values

- 5.6 Insulation Specifications

- 5.7 Electrical Characterstics

- 5.8 Electrical Characteristics

- 5.9 Electrical Characteristics

- 5.10 Electrical Charcteristics

- 5.11 Switching Characteristics

- 5.12 Switching Characteristics

- 5.13 Switching Characteristics

- 5.14 Switching Characteristics

- 5.15 Typical Characteristics

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

3 概要

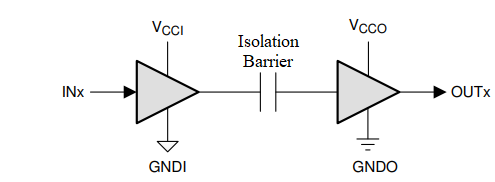

ISO7220x-Q1 および ISO7221x-Q1 ファミリのデバイスは、デュアル チャネルのデジタル アイソレータです。PCB レイアウトを容易にするために、チャネルは ISO7220x-Q1 では同じ方向、ISO7221x-Q1 では反対方向に配置されています。これらのデバイスはテキサス・インスツルメンツのシリコン酸化膜 (SiO2) 絶縁バリアによって分離されたロジック入出力バッファを搭載しており、VDE に準拠した最大 4000VPK のガルバニック絶縁を提供します。これらのデバイスを絶縁型電源と組み合わせて使用すると、高電圧がブロックされ、グランドが絶縁されます。また、データ バスや他の回路で発生したノイズ電流がローカル グランドに入り込み、ノイズに敏感な回路に干渉または損傷を与えることを防止できます。

バイナリ入力信号がコンディショニングされ、バランスされた信号に変換されてから、容量性絶縁バリアによって差動化されます。絶縁バリアを通過して、差動コンパレータがロジック変換情報を受け取り、それに応じてフリップフロップおよび出力回路を設定またはリセットします。バリアを通して周期的に更新パルスが送信され、出力の DC レベルが適切であることを検証します。この DC 更新パルスが 4μs ごとに受信されない場合、入力に電力が供給されていない、またはアクティブに駆動されていないと見なされ、フェイルセーフ回路により出力が論理 HIGH 状態に駆動されます。

容量が小さく、その結果として時定数も小さいため、高速な動作が可能で、0Mbps (DC) から 25Mbps までの信号速度に対応できます (ラインの信号速度は、1 秒あたりの電圧遷移回数であり、bps 単位で表されます)。A オプションおよび C オプションのデバイスは、入力に TTL 入力しきい値とノイズ フィルタを備えており、過渡的パルスがデバイスの出力に渡されることを防止します。M オプションのデバイスには CMOS VCC/2 入力しきい値が存在しますが、入力ノイズ フィルタはなく、追加の伝搬遅延が発生しません。

ISO7220x-Q1 および ISO7221x-Q1 ファミリのデバイスは、2.8V (C グレード)、3.3V、5V、またはいずれかの組み合わせの 2 つの電源電圧を必要とします。2.8V または 3.3V 電源で動作するとき、すべての入力は 5V 許容で、すべての出力は 4mA CMOS です。

ISO7220x-Q1 および ISO7221x-Q1 ファミリのデバイスは、-40℃~+125℃の周囲温度範囲で動作が規定されています。

| 部品番号 | パッケージ (1) | 本体サイズ (公称) | パッケージ サイズ(2) |

|---|---|---|---|

| ISO7220x-Q1 | D (SOIC、8) | 4.90mm × 3.91mm | 4.9mm × 6mm |

| ISO7221x-Q1 |