JAJSVM9B September 2010 – November 2024 ISO7240CF-Q1 , ISO7241C-Q1 , ISO7242C-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configurations and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Characteristics

- 5.5 Power Ratings

- 5.6 Safety-Related Certifications

- 5.7 Safety Limiting Values

- 5.8 Insulation Specifications

- 5.9 Electrical Characteristics: VCC1 and VCC2 at 5-V Operation

- 5.10 Electrical Characteristics: VCC1 and VCC2 at 3.3 V Operation

- 5.11 Electrical Characteristics: VCC1 at 3.3-V, VCC2 at 5-V Operation

- 5.12 Electrical Characteristics: VCC1 at 5-V, VCC2 at 3.3-V Operation

- 5.13 Switching Characteristics: VCC1 and VCC2 at 3.3-V Operation

- 5.14 Switching Characterstics: VCC1 and VCC2 at 5-V Operation

- 5.15 Switching Characteristics: VCC1 at 3.3-V and VCC2 at 5-V Operation

- 5.16 Switching Characteristics: VCC1 at 5-V, VCC2 at 3.3-V Operation

- 5.17 Insulation Characteristics Curves

- 5.18 Typical Characteristic

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DW|16

サーマルパッド・メカニカル・データ

- DW|16

発注情報

3 概要

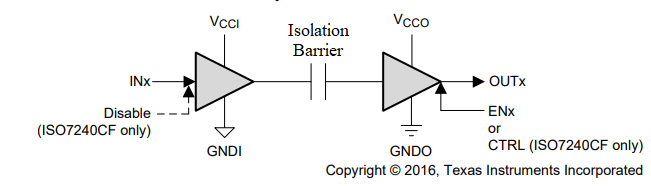

ISO7240CF-Q1、ISO7241C-Q1、ISO7242C-Q1 の各デバイスは、複数のチャネル構成と出力イネーブル機能を備えたクワッド チャネル デジタル アイソレータです。これらのデバイスは、テキサス インスツルメンツ独自の二酸化ケイ素 (SiO2) 絶縁バリアで分離されたロジック入出力バッファを備えています。これらのデバイスは、絶縁型電源と組み合わせて使用することで、高電圧を遮断し、グランドを絶縁し、ノイズ電流がローカル グランドに入り込んでノイズに敏感な回路に干渉したり損傷を与えたりすることを防止します。

ISO7240C-Q1 ファミリのデバイスは、同じ方向に 4 チャネルを備えています。ISO7241C-Q1 ファミリのデバイスは、同じ方向に 3 チャネル、反対方向に 1 チャネルを備えています。ISO7242C-Q1 ファミリのデバイスは、各方向に 2 チャネルを備えています。

接尾辞 C (C オプション) のデバイスには、TTL 入力スレッショルドと、遷移パルスがデバイスの出力に渡されるのを防ぐノイズ フィルタが入力に備わっています。接尾辞 M (M オプション) のデバイスには、CMOS VCC/2 入力スレッショルドが備わっていますが、入力ノイズ フィルタはなく、追加の伝搬遅延も発生しません。

ISO7240CF デバイスは、ピン 7 に入力ディセーブル機能を備え、CTRL ピン (ピン 10) に High または Low が選択可能なフェイルセーフ出力機能を備えています。フェイルセーフ出力は、CTRL ピンにロジック High が印加された場合、またはピンが未接続のままである場合、ロジック High になります。CTRL ピンにロジック Low 信号が印加されると、フェイルセーフ出力はロジック Low 出力状態になります。ISO7240CF デバイスの入力ディセーブル機能により、絶縁バリアを通過してデータが出力に渡されるのを防ぎます。入力がディセーブルされるか、VCC1 がパワーダウンすると、出力は CTRL ピンによって設定されます。

これらのデバイスは、どちらの側でも 3.3V または 5V 電源から電力を供給でき、任意の組み合わせが可能です。信号入力ピンは、使用される電源電圧レベルに関係なく 5V 許容です。

これらのデバイスは、-40℃~+125℃の周囲温度範囲で動作するように特性評価されています。

| 部品番号 | パッケージ (1) | 本体サイズ (公称) | パッケージ サイズ(2) |

|---|---|---|---|

| ISO7240CF-Q1 | DW (SOIC、16) | 10.30mm × 7.50mm | 10.30mm × 10.30mm |

| ISO7241C-Q1 | |||

| ISO7242C-Q1 |