JAJSUF7 November 2023 – April 2024 IWRL6432AOP

ADVANCE INFORMATION

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 機能ブロック図

- 5 デバイスの比較

- 6 端子構成および機能

-

7 仕様

- 7.1 絶対最大定格

- 7.2 ESD 定格

- 7.3 電源投入時間 (POH)

- 7.4 推奨動作条件

- 7.5 ワンタイム プログラマブル (OTP) eFuse の VPP 仕様

- 7.6 電源仕様

- 7.7 パワー セーブ モード

- 7.8 電圧レールごとのピーク電流要件

- 7.9 サポート対象 DFE 機能

- 7.10 RF 仕様

- 7.11 CPU の仕様

- 7.12 熱抵抗特性

- 7.13 アンテナ放射パターン

- 7.14 アンテナ位置

- 7.15

タイミングおよびスイッチング特性

- 7.15.1 電源シーケンスおよびリセット タイミング

- 7.15.2 同期フレーム トリガ

- 7.15.3 入力クロックおよび発振器

- 7.15.4 マルチチャネル バッファ付き / 標準シリアル ペリフェラル インターフェイス (McSPI)

- 7.15.5 RDIF インターフェイスの構成

- 7.15.6 汎用入出力 (General-Purpose Input/Output)

- 7.15.7 CAN-FD (Controller Area Network - Flexible Data-rate)

- 7.15.8 シリアル通信インターフェイス (SCI)

- 7.15.9 I2C (Inter-Integrated Circuit Interface)

- 7.15.10 クワッド シリアル ペリフェラル インターフェイス (QSPI)

- 7.15.11 JTAG インターフェイス

- 8 詳細説明

- 9 監視と診断

- 10アプリケーション、実装、およびレイアウト

- 11デバイスおよびドキュメントのサポート

- 12改訂履歴

- 13メカニカル、パッケージ、および注文情報

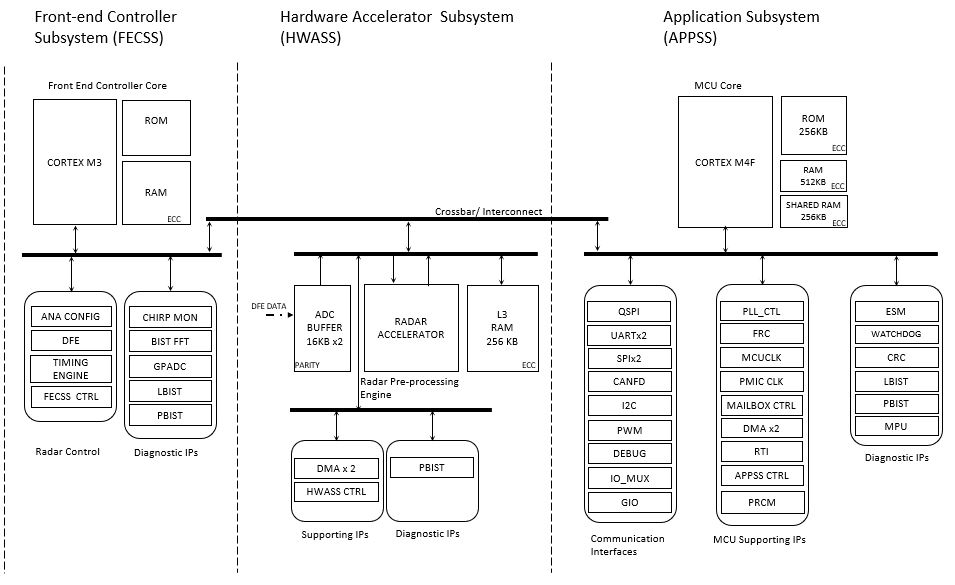

8.3.5 プロセッサ サブシステム

図 8-4 プロセッサ サブシステム

図 8-4 プロセッサ サブシステム図 8-4 に、IWRL6432AOP デバイスのカスタマー プログラマブル プロセッサ サブシステムのブロック図を示します。概念的には、2 つのカスタマー プログラマブル プロセッサ サブシステムが存在し、図に示すように点線で区切られています。左側に、HWA、高性能高帯域幅 (64 ビット、80MHz) インターコネクト、関連ペリフェラルのデータ転送を示します。測定データ出力用の RDIF インターフェイス、L3 レーダー データ キューブ メモリ、ADC バッファ、CRC エンジン、データ ハンドシェイク メモリ (インターコネクト上に搭載された追加メモリ)。

この図の右側に、メイン サブシステムを示します。メイン サブシステムは、本デバイスの頭脳であり、本デバイスのすべてのペリフェラルとハウスキーピング動作を制御します。メイン サブシステムには、Cortex-M4F プロセッサと関連ペリフェラルおよびハウスキーピング コンポーネント (例:DMA、CRC、PCR (ペリフェラル セントラル リソース) インターコネクトを介してメイン インターコネクトに接続されたペリフェラル (I2C、UART、SPI、CAN、PMIC クロック モジュール、PWM など)) が含まれます。