JAJSVZ6 December 2024 IWRL6432W

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 機能ブロック図

- 5 デバイスの比較

- 6 端子構成および機能

-

7 仕様

- 7.1 絶対最大定格

- 7.2 ESD 定格

- 7.3 電源投入時間 (POH)

- 7.4 推奨動作条件

- 7.5 ワンタイム プログラマブル (OTP) eFuse の VPP 仕様

- 7.6 電源仕様

- 7.7 パワー セーブ モード

- 7.8 電圧レールごとのピーク電流要件

- 7.9 RF 仕様

- 7.10 サポート対象 DFE 機能

- 7.11 CPU の仕様

- 7.12 熱抵抗特性

- 7.13

タイミングおよびスイッチング特性

- 7.13.1 電源シーケンスおよびリセット タイミング

- 7.13.2 同期フレーム トリガ

- 7.13.3 入力クロックおよび発振器

- 7.13.4 マルチチャネル バッファ付き / 標準シリアル ペリフェラル インターフェイス (McSPI)

- 7.13.5 RDIF インターフェイスの構成

- 7.13.6 汎用入出力 (General-Purpose Input/Output)

- 7.13.7 CAN-FD (Controller Area Network - Flexible Data-rate)

- 7.13.8 シリアル通信インターフェイス (SCI)

- 7.13.9 I2C (Inter-Integrated Circuit Interface)

- 7.13.10 クワッド シリアル ペリフェラル インターフェイス (QSPI)

- 7.13.11 JTAG インターフェイス

- 8 詳細説明

- 9 アプリケーション、実装、およびレイアウト

- 10デバイスおよびドキュメントのサポート

- 11改訂履歴

- 12メカニカル、パッケージ、および注文情報

8.4.1 ユーザー アプリケーション向け GPADC チャネル (サービス)

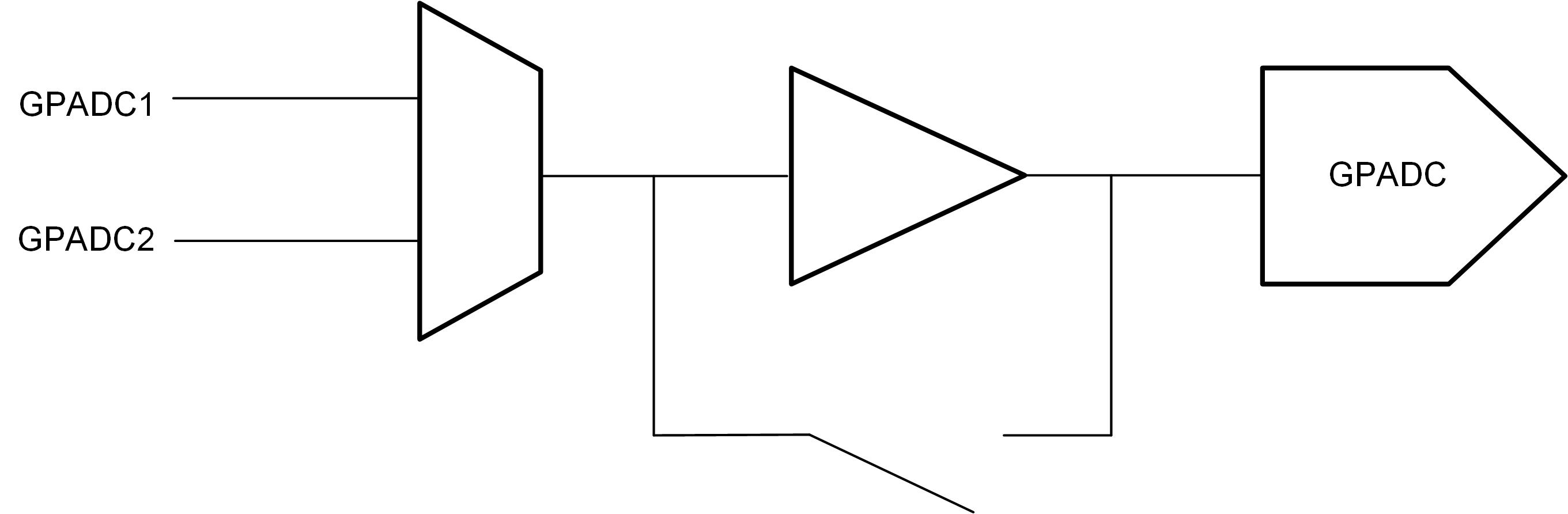

IWRL6432W デバイスは、ユーザー アプリケーションのための ADC サービス機能を備えており、本デバイスが内蔵する GPADC エンジンを使って最大 2 つの外部電圧を測定できます。GPADC1 および GPADC2 ピンは、このために使われます。

- GPADC 自体は、FEC サブシステム内で動作するテキサス・インスツルメンツ製ファームウェアによって制御され、ユーザーが外部電圧を監視するための GPADC アクセスは、FEC サブシステムに転送される「APPSS」コールによって行われます。この API は、APPSS Cortex M4F® で動作しているユーザー アプリケーションとリンクさせることができます。

- デバイス ファームウェア パッケージ (DFP) には、これらの信号を構成および測定するための API が含まれています。この API を使用すると、セトリング時間 (スキップする ADC サンプル数) と取得する連続サンプル数を設定できます。フレームの最後に、監視対象の各電圧について、測定値の最小値、最大値、平均値が報告されます。

図 8-7 GPADC パス

図 8-7 GPADC パスGPADC 構造は、内部温度センサの出力を測定するために使われます。これらの測定の精度は ±7℃です。