JAJSDG8F July 2011 – March 2018 LM25118

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Custom Design With WEBENCH® Tools

- 8.2.2.2 R7 = RT

- 8.2.2.3 Inductor Selection – L1

- 8.2.2.4 R13 = RSENSE

- 8.2.2.5 C15 = CRAMP

- 8.2.2.6 Inductor Current Limit Calculation

- 8.2.2.7 C9 - C12 = Output Capacitors

- 8.2.2.8 D1

- 8.2.2.9 D4

- 8.2.2.10 C1 – C5 = Input Capacitors

- 8.2.2.11 C20

- 8.2.2.12 C8

- 8.2.2.13 C16 = CSS

- 8.2.2.14 R8, R9

- 8.2.2.15 R1, R3, C21

- 8.2.2.16 R2

- 8.2.2.17 Snubber

- 8.2.2.18 Error Amplifier Configuration

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- PWP|20

サーマルパッド・メカニカル・データ

- PWP|20

発注情報

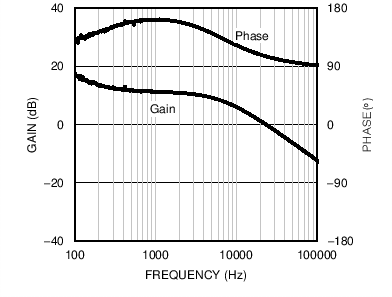

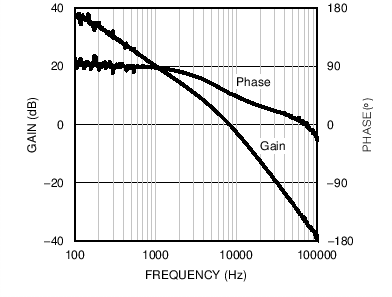

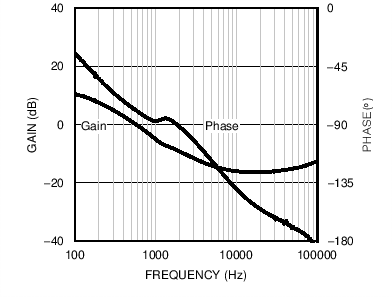

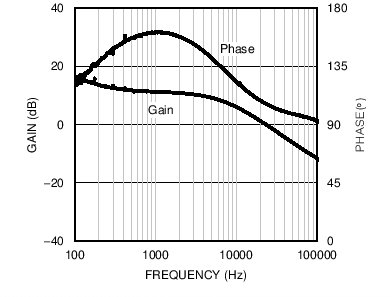

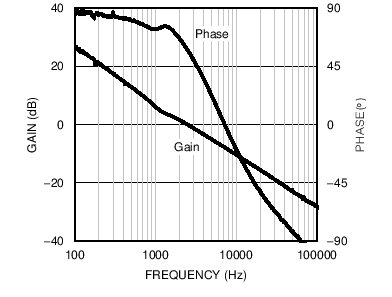

8.2.3 Application Curves

The plots shown in Figure 21 through Figure 26 show the gain and phase diagrams of the design example. The overall bandwidth is lower in a buck-boost application due the compensation challenges associated with the right-half-plane zero. For a pure buck application, the bandwidth could be much higher. The LM5116 data sheet is a good reference for compensation design of a pure buck mode regulator.