JAJS857D March 1998 – May 2016 LM2598

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics - 3.3-V Version

- 7.6 Electrical Characteristics - 5-V Version

- 7.7 Electrical Characteristics - 12-V Version

- 7.8 Electrical Characteristics - Adjustable Voltage Version

- 7.9 Electrical Characteristics - All Output Voltage Versions

- 7.10 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- KTW|7

発注情報

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Maximum supply voltage, VIN | 45 | V | |||

| SD/SS pin input voltage(3) | 6 | V | |||

| Delay pin voltage(3) | 1.5 | V | |||

| Flag pin voltage | –0.3 | 45 | V | ||

| Feedback pin voltage | –0.3 | 25 | V | ||

| Output voltage to ground (steady state) | –1 | V | |||

| Power dissipation | Internally limited | ||||

| Lead temperature | KTW package | Vapor phase (60 s) | 215 | °C | |

| Infrared (10 s) | 245 | ||||

| NDZ package (soldering, 10 s) | 260 | ||||

| Maximum junction temperature | 150 | °C | |||

| Storage temperature, Tstg | –65 | 150 | °C | ||

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

(3) Voltage internally clamped. If clamp voltage is exceeded, limit current to a maximum of 1 mA.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1)(2) | ±2000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) The human body model is a 100-pF capacitor discharged through a 1.5k resistor into each pin.

7.3 Recommended Operating Conditions

| MIN | MAX | UNIT | |

|---|---|---|---|

| Supply voltage | 4.5 | 40 | V |

| Temperature | –25 | 125 | °C |

7.4 Thermal Information

| THERMAL METRIC(1) | LM2598 | UNIT | |||

|---|---|---|---|---|---|

| KTW (TO-263) | NDZ (TO-220) | ||||

| 7 PINS | 7 PINS | ||||

| RθJA | Junction-to-ambient thermal resistance(2)(3) | See(4) | — | 50 | °C/W |

| See(5) | 50 | — | |||

| See(6) | 30 | — | |||

| See(7) | 20 | — | |||

| RθJC(top) | Junction-to-case (top) thermal resistance | 2 | 2 | °C/W | |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) The package thermal impedance is calculated in accordance to JESD 51-7.

(3) Thermal Resistances were simulated on a 4 -layer, JEDEC board.

(4) Junction to ambient thermal resistance (no external heat sink) for the package mounted TO-220 package mounted vertically, with the leads soldered to a printed circuit board with (1 oz.) copper area of approximately 1 in2.

(5) Junction to ambient thermal resistance with the TO-263 package tab soldered to a single sided printed circuit board with 0.5 in2 of (1 oz.) copper area.

(6) Junction to ambient thermal resistance with the TO-263 package tab soldered to a single sided printed circuit board with 2.5 in2 of (1 oz.) copper area.

(7) Junction to ambient thermal resistance with the TO-263 package tab soldered to a double sided printed circuit board with 3 in2 of (1 oz.) copper area on the LM2598S side of the board, and approximately 16 in2 of copper on the other side of the PCB.

7.5 Electrical Characteristics – 3.3-V Version

Specifications are for TJ = 25°C, unless otherwise specified.| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX (1) | UNIT | ||

|---|---|---|---|---|---|---|---|

| SYSTEM PARAMETERS(3) (see Figure 42 and Figure 45 for test circuits) | |||||||

| VOUT | Output voltage | 4.75 V ≤ VIN ≤ 40 V, 0.1 A ≤ ILOAD ≤ 1 A |

TJ = 25°C | 3.168 | 3.3 | 3.432 | V |

| Over full operating temperature range | 3.135 | 3.465 | |||||

| η | Efficiency | VIN = 12 V, ILOAD = 1 A | 78% | ||||

(1) All room temperature limits are 100% production tested. All limits at temperature extremes are specified via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely norm.

7.6 Electrical Characteristics – 5-V Version

Specifications are for TJ = 25°C, unless otherwise specified.| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | ||

|---|---|---|---|---|---|---|---|

| SYSTEM PARAMETERS(3) (see Figure 42 and Figure 45 for test circuits) | |||||||

| VOUT | Output voltage | 7 V ≤ VIN ≤ 40 V, 0.1 A ≤ ILOAD ≤ 1 A |

TJ = 25°C | 4.8 | 5 | 5.2 | V |

| Over full operating temperature range | 4.75 | 5.25 | |||||

| η | Efficiency | VIN = 12 V, ILOAD = 1 A | 82% | ||||

(1) All room temperature limits are 100% production tested. All limits at temperature extremes are specified via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely norm.

7.7 Electrical Characteristics – 12-V Version

Specifications are for TJ = 25°C, unless otherwise specified.| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | ||

|---|---|---|---|---|---|---|---|

| SYSTEM PARAMETERS(3) (see Figure 42 and Figure 45 for test circuits) | |||||||

| VOUT | Output voltage | 15 V ≤ VIN ≤ 40 V, 0.1 A ≤ ILOAD ≤ 1 A |

TJ = 25°C | 11.52 | 12 | 12.48 | V |

| Over full operating temperature range | 11.4 | 12.6 | |||||

| η | Efficiency | VIN = 25 V, ILOAD = 1 A | 90% | ||||

(1) All room temperature limits are 100% production tested. All limits at temperature extremes are specified via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely norm.

7.8 Electrical Characteristics – Adjustable Voltage Version

Specifications are for TJ = 25°C, unless otherwise specified.| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | ||

|---|---|---|---|---|---|---|---|

| SYSTEM PARAMETERS(3) (see Figure 42 and Figure 45 for test circuits) | |||||||

| VFB | Feedback voltage | 4.5 V ≤ VIN ≤ 40 V, 0.1 A ≤ ILOAD ≤ 1 A | 1.23 | V | |||

| VOUT programmed for 3 V, circuit of Figure 42 and Figure 45 | TJ = 25°C | 1.193 | 1.267 | ||||

| Over full operating temperature range | 1.18 | 1.28 | |||||

| η | Efficiency | VIN = 12 V, VOUT = 3 V, ILOAD = 1 A | 78% | ||||

(1) All room temperature limits are 100% production tested. All limits at temperature extremes are specified via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely norm.

7.9 Electrical Characteristics – All Output Voltage Versions

Specifications are for TJ = 25°C unless otherwise noted. Unless otherwise specified, VIN = 12 V for the 3.3-V, 5-V, and Adjustable version and VIN = 24 V for the 12-V version. ILOAD = 500 mA| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(2) | MAX(1) | UNIT | ||

|---|---|---|---|---|---|---|---|

| DEVICE PARAMETERS | |||||||

| Ib | Feedback bias current | Adjustable version only, VFB = 1.3 V |

TJ = 25°C | 10 | 50 | nA | |

| Over full operating temperature range | 100 | ||||||

| fO | Oscillator frequency | See(3) | TJ = 25°C | 127 | 150 | 173 | kHz |

| Over full operating temperature range | 110 | 173 | |||||

| VSAT | Saturation voltage | IOUT = 1 A (4)(5) | TJ = 25°C | 1 | 1.2 | V | |

| Over full operating temperature range | 1.3 | ||||||

| DC | Max duty cycle (ON) | See(5) | 100% | ||||

| Minimum duty cycle (OFF) | See(6) | 0% | |||||

| ICL | Current limit | Peak current(4)(5) | TJ = 25°C | 1.2 | 1.5 | 2.4 | A |

| Over full operating temperature range | 1.15 | 2.6 | |||||

| IL | Output leakage current | Output = 0 V, see(4)(6)(7) | 50 | μA | |||

| Output = –1 V | 2 | 15 | mA | ||||

| IQ | Operating quiescent current | SD/SS pin open(6) | 5 | 10 | mA | ||

| ISTBY | Current standby quiescent | SD/SS pin = 0 V(7) | TJ = 25°C | 85 | 200 | μA | |

| Over full operating temperature range | 250 | ||||||

| SHUTDOWN AND SOFT-START CONTROL (see Figure 42 and Figure 45 for test circuits) | |||||||

| VSD | Shutdown threshold voltage | TJ = 25°C | 1.3 | V | |||

| Low, (Shutdown Mode), over full operating temperature range | 0.6 | ||||||

| High, (Soft-start Mode), over full operating temperature range | 2 | ||||||

| VSS | Soft-start voltage | VOUT = 20% of nominal output voltage | 2 | V | |||

| VOUT = 100% of nominal output voltage | 3 | ||||||

| ISD | Shutdown current | VSHUTDOWN = 0.5 V | 5 | 10 | μA | ||

| ISS | Soft-start current | VSoft-start = 2.5 V | 1.6 | 5 | μA | ||

| FLAG AND DELAY CONTROL (see Figure 42 and Figure 45 for test circuits) | |||||||

| Regulator dropout detector threshold voltage | Low (Flag ON) | 92% | 96% | 98% | |||

| VFSAT | Voltage flag output saturation | ISINK = 3 mA | 0.3 | V | |||

| VDELAY = 0.5 V | TJ = 25°C | 0.7 | V | ||||

| Over full operating temperature range | 1 | ||||||

| IFL | Flag output leakage current | VFLAG = 40 V | 0.3 | μA | |||

| Voltage delay pin threshold | 1.25 | V | |||||

| Low (Flag ON) | 1.21 | V | |||||

| High (Flag OFF) and VOUT Regulated | 1.29 | ||||||

| Delay pin source current | VDELAY = 0.5 V | 3 | 6 | μA | |||

| Delay pin saturation | Low (Flag ON) | TJ = 25°C | 55 | 350 | mV | ||

| Over full operating temperature range | 400 | ||||||

(1) All room temperature limits are 100% production tested. All limits at temperature extremes are specified via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely norm.

(3) The switching frequency is reduced when the second stage current limit is activated. The amount of reduction is determined by the severity of current overload.

(4) No diode, inductor or capacitor connected to output pin.

(5) Feedback pin removed from output and connected to 0 V to force the output transistor switch ON.

(6) Feedback pin removed from output and connected to 12 V for the 3.3-V, 5-V, and the Adjustable version, and 15 V for the 12-V version, to force the output transistor switch OFF.

(7) VIN = 40 V.

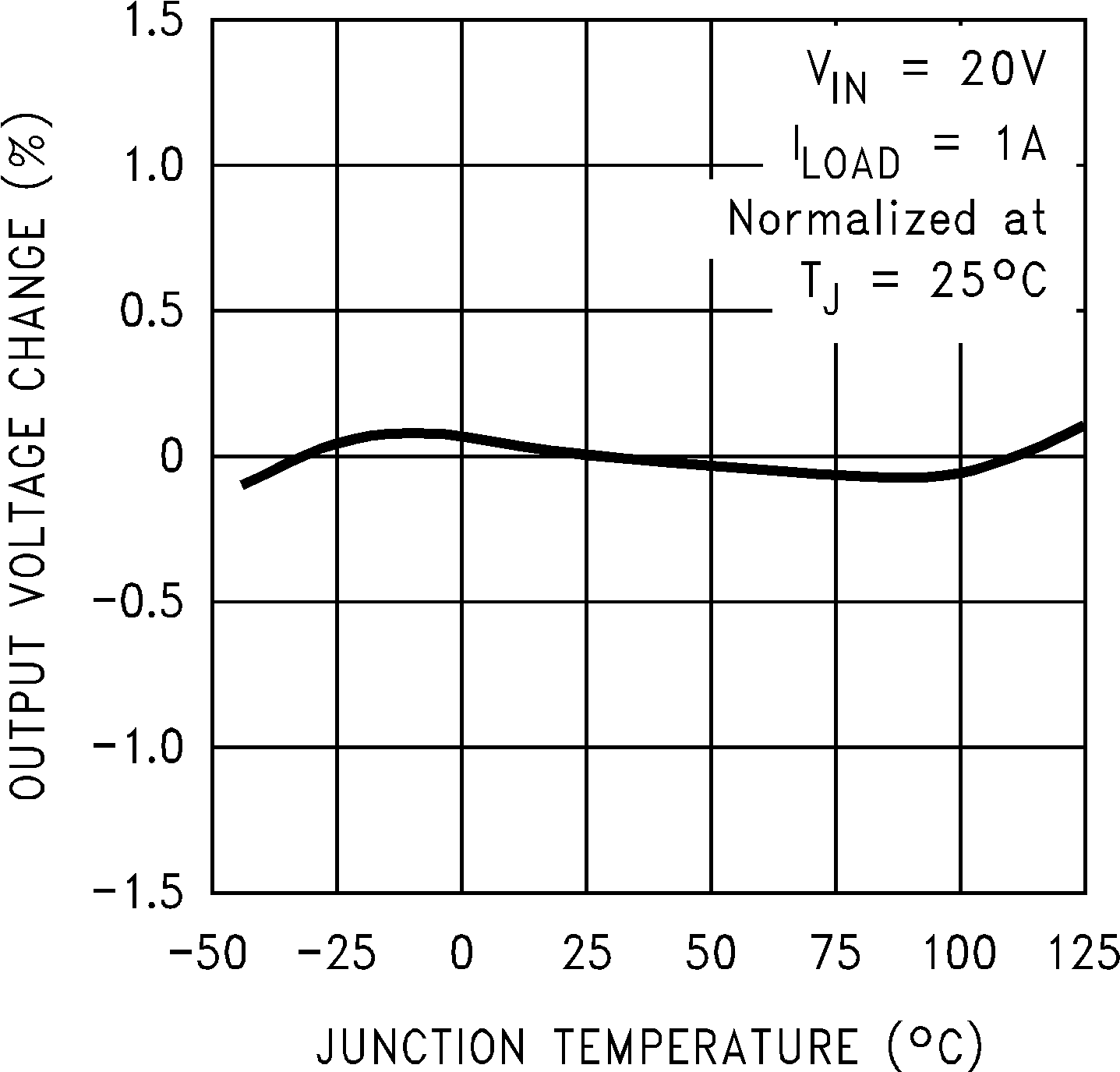

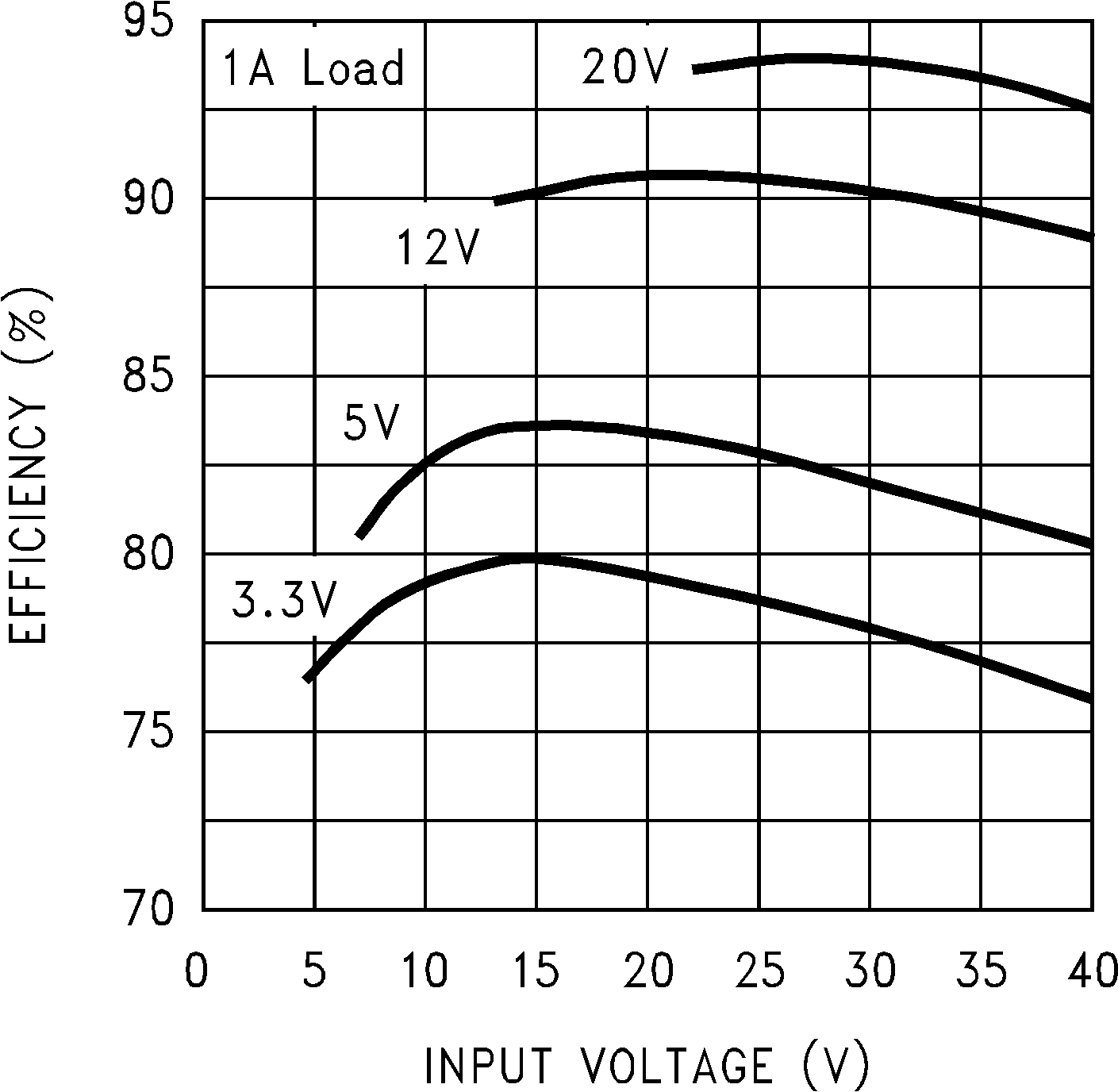

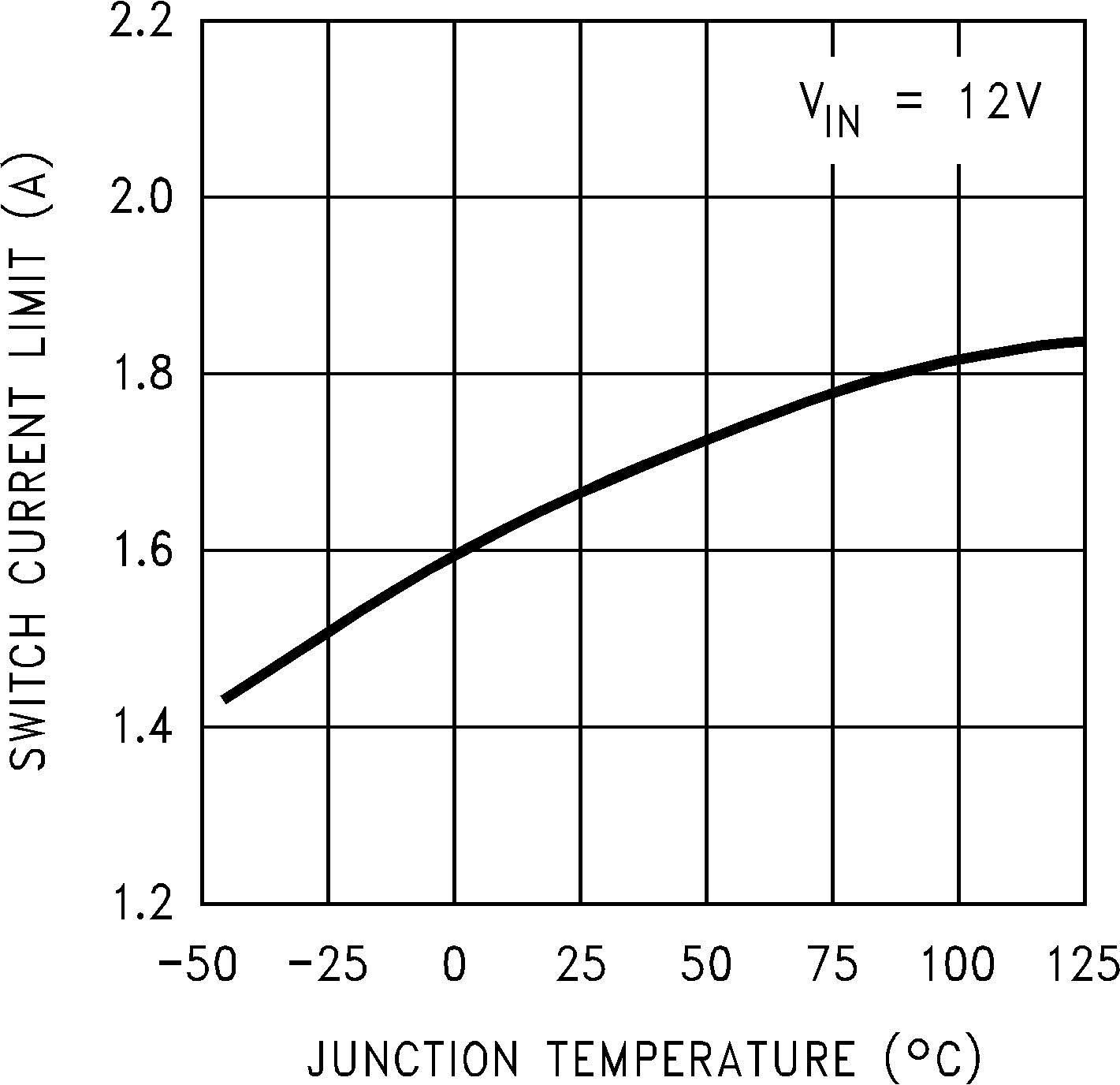

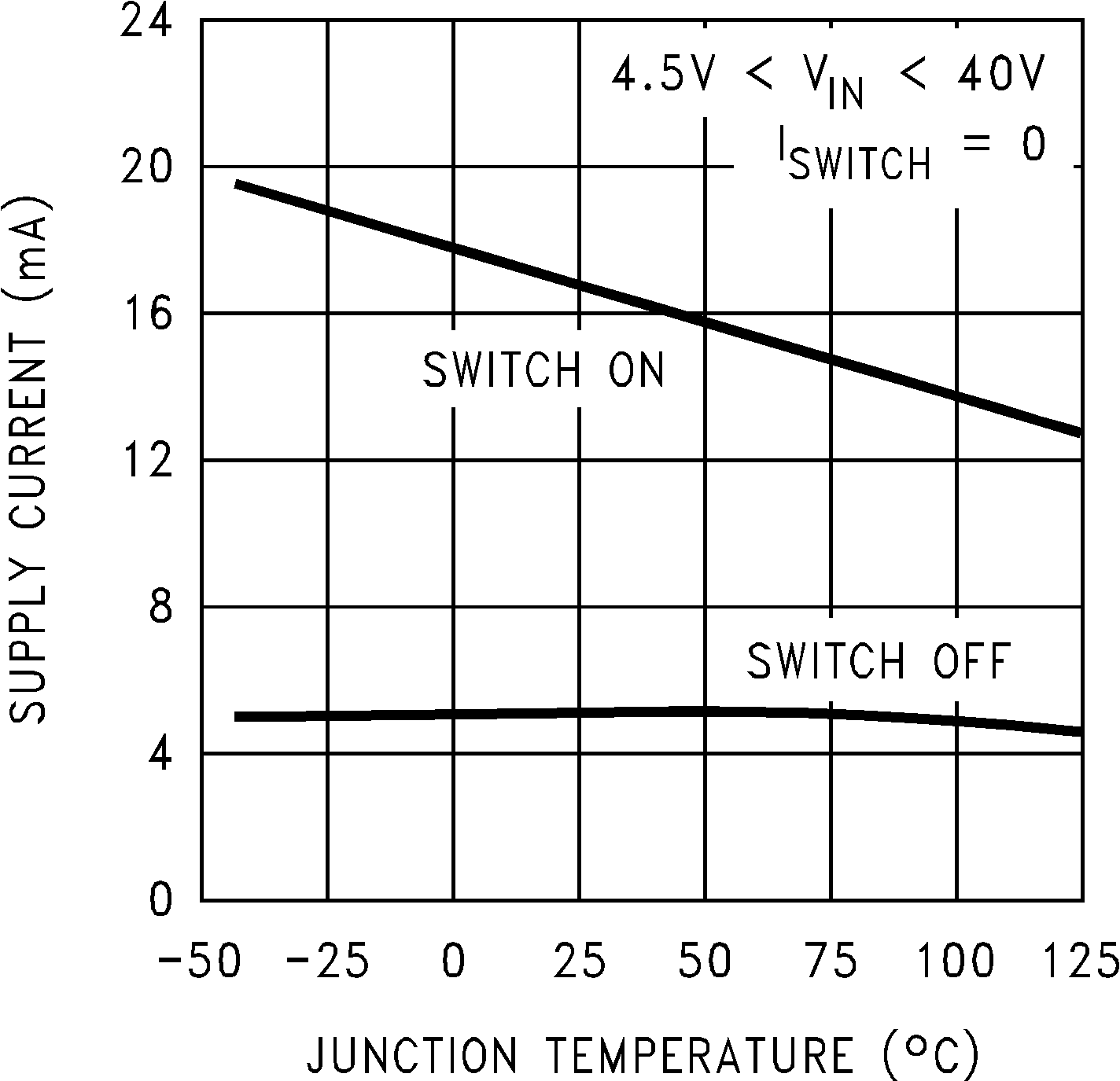

7.10 Typical Characteristics

Circuit of Figure 45 Figure 1. Normalized Output Voltage

Figure 1. Normalized Output Voltage

Figure 3. Efficiency

Figure 3. Efficiency

Figure 5. Switch Current Limit

Figure 5. Switch Current Limit

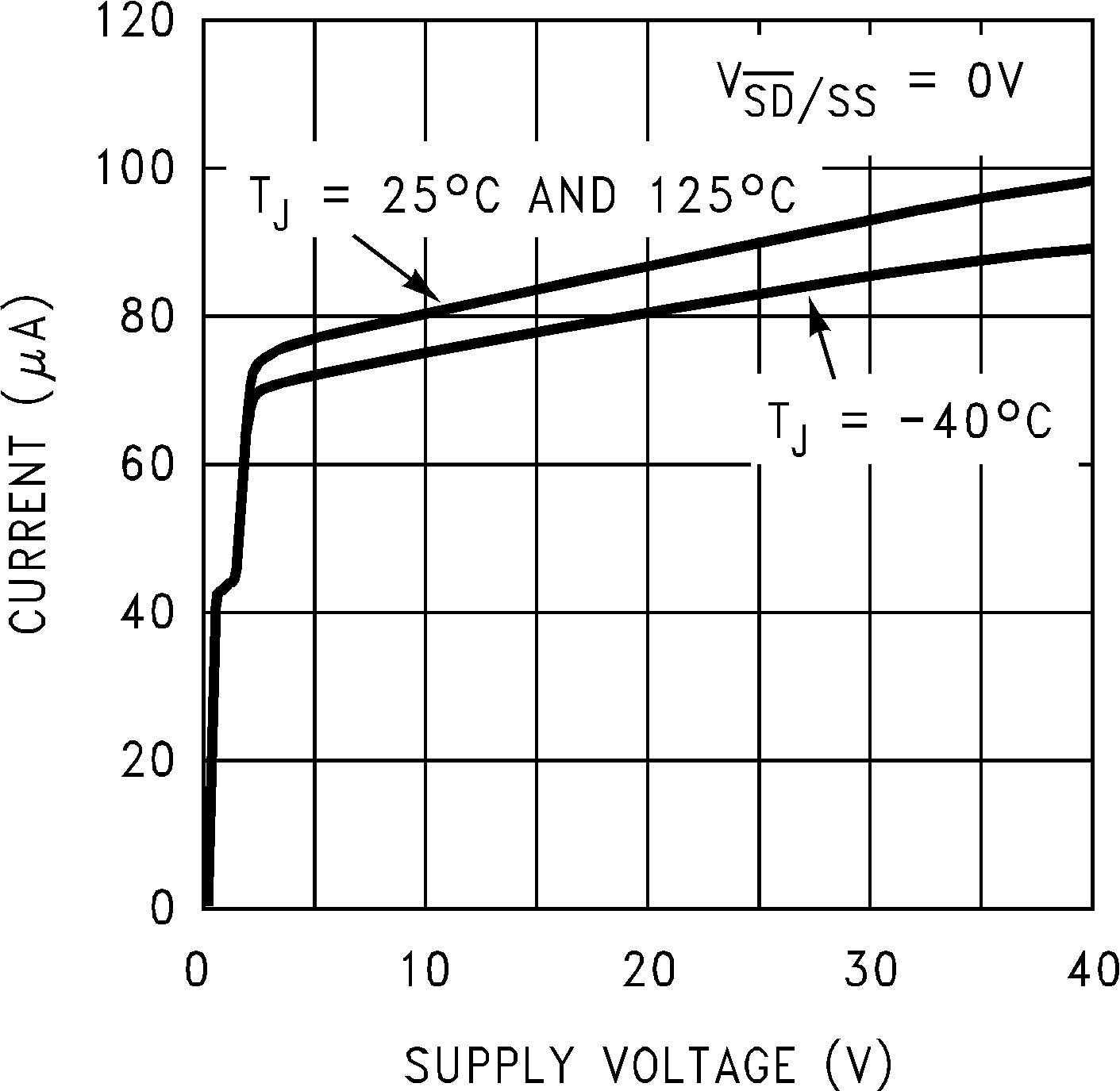

Figure 7. Operating Quiescent Current

Figure 7. Operating Quiescent Current

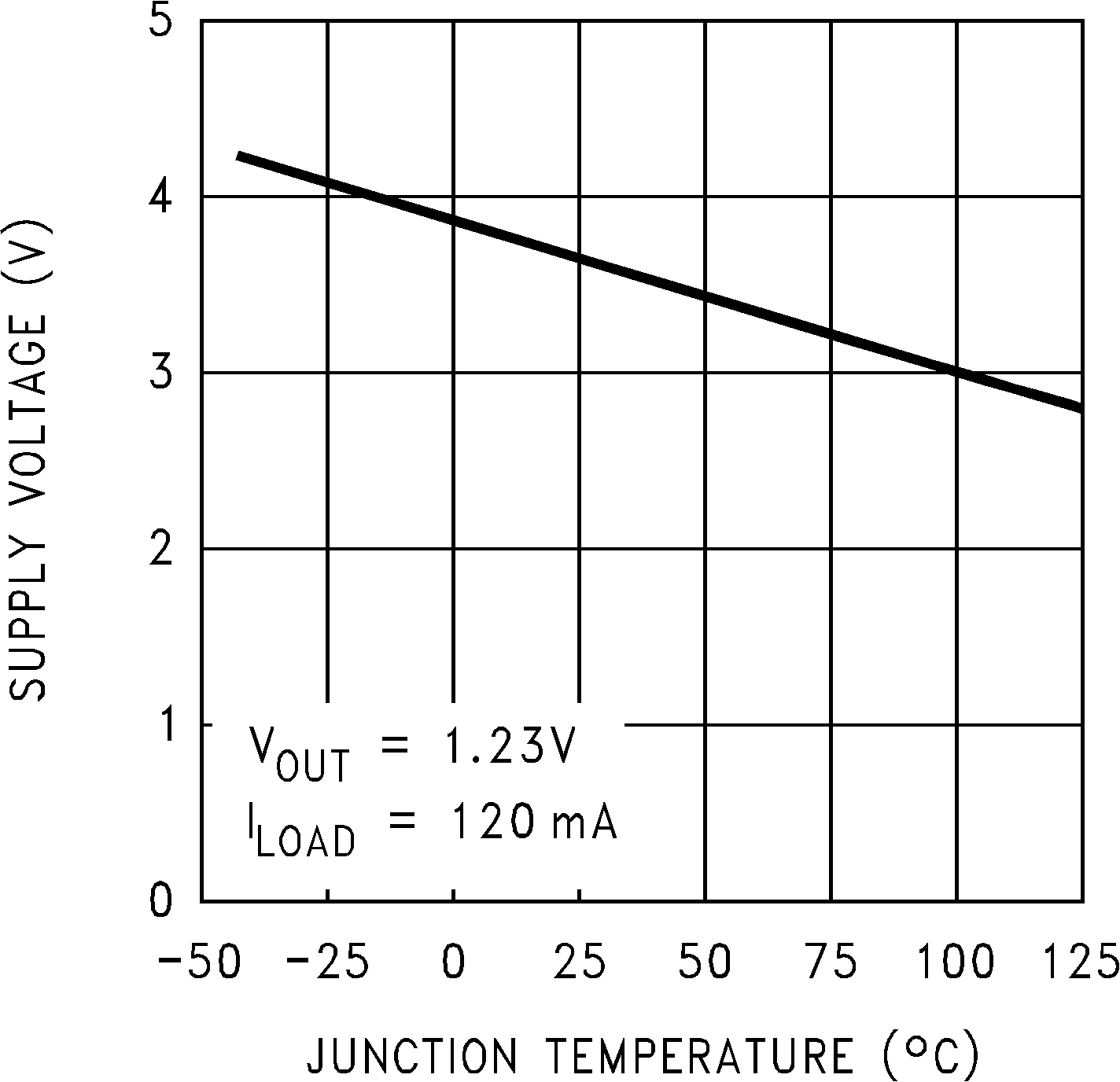

Figure 9. Minimum Operating Supply Voltage

Figure 9. Minimum Operating Supply Voltage

Figure 11. Flag Saturation Voltage

Figure 11. Flag Saturation Voltage

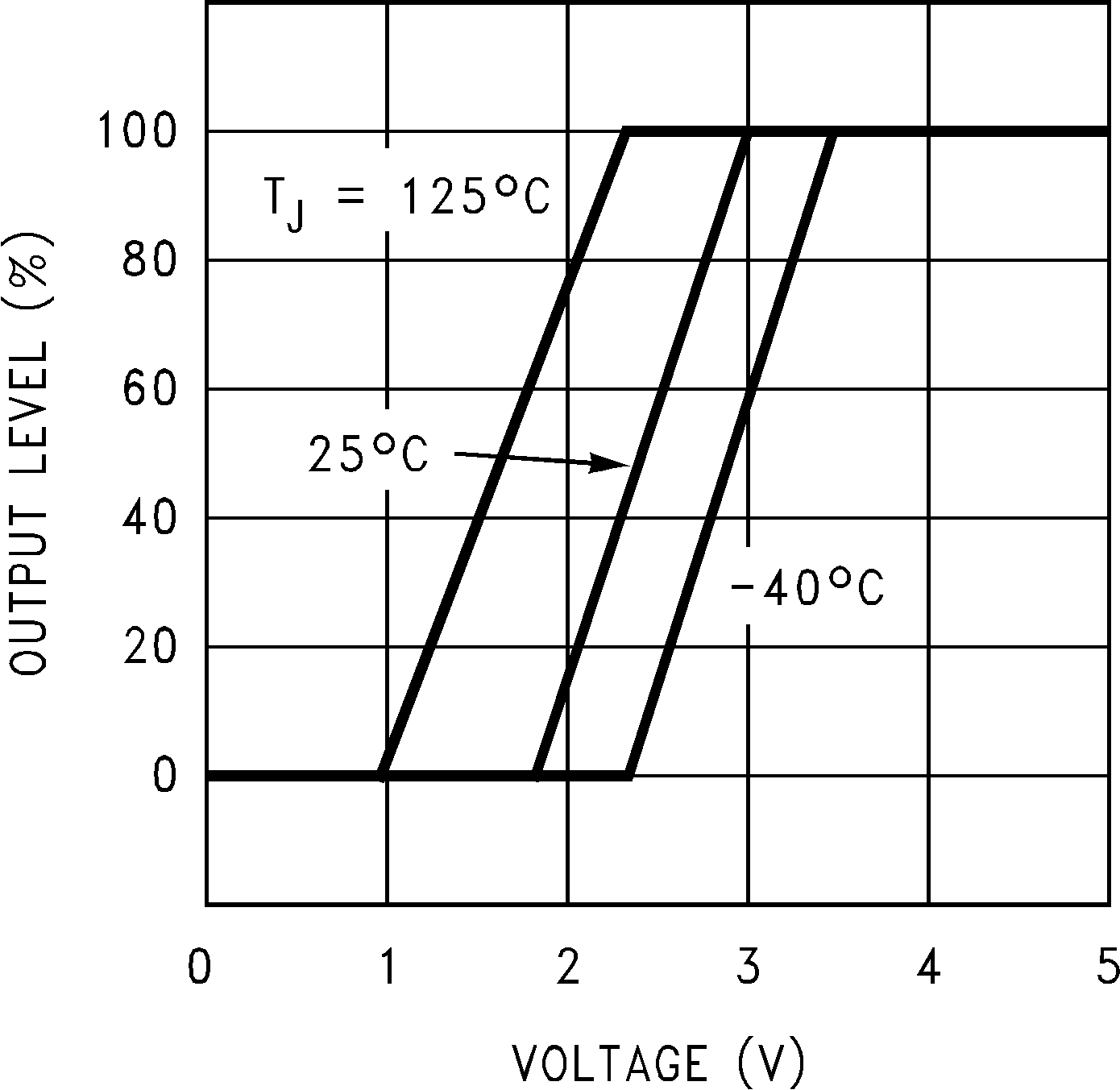

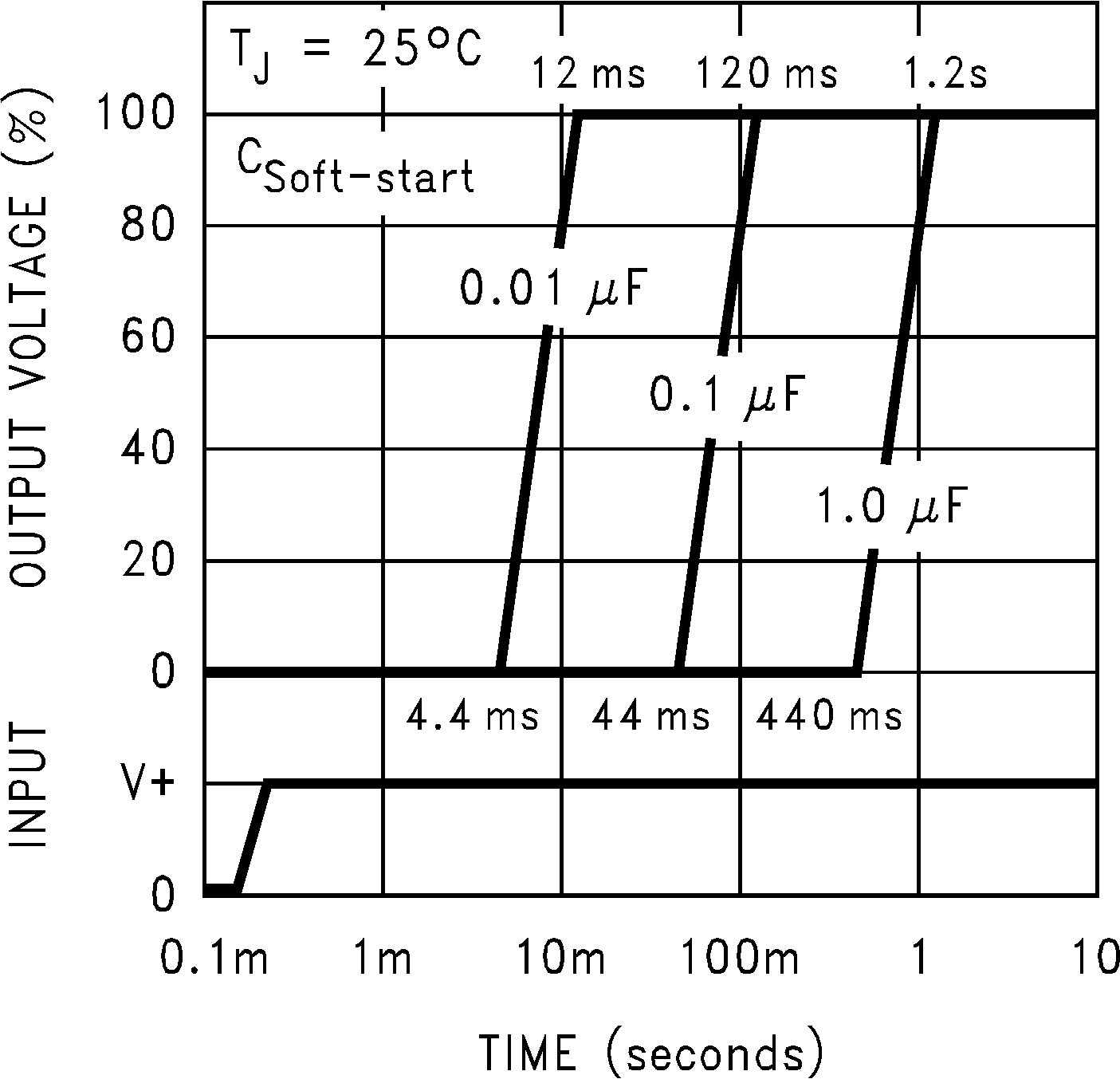

Figure 13. Soft-start

Figure 13. Soft-start

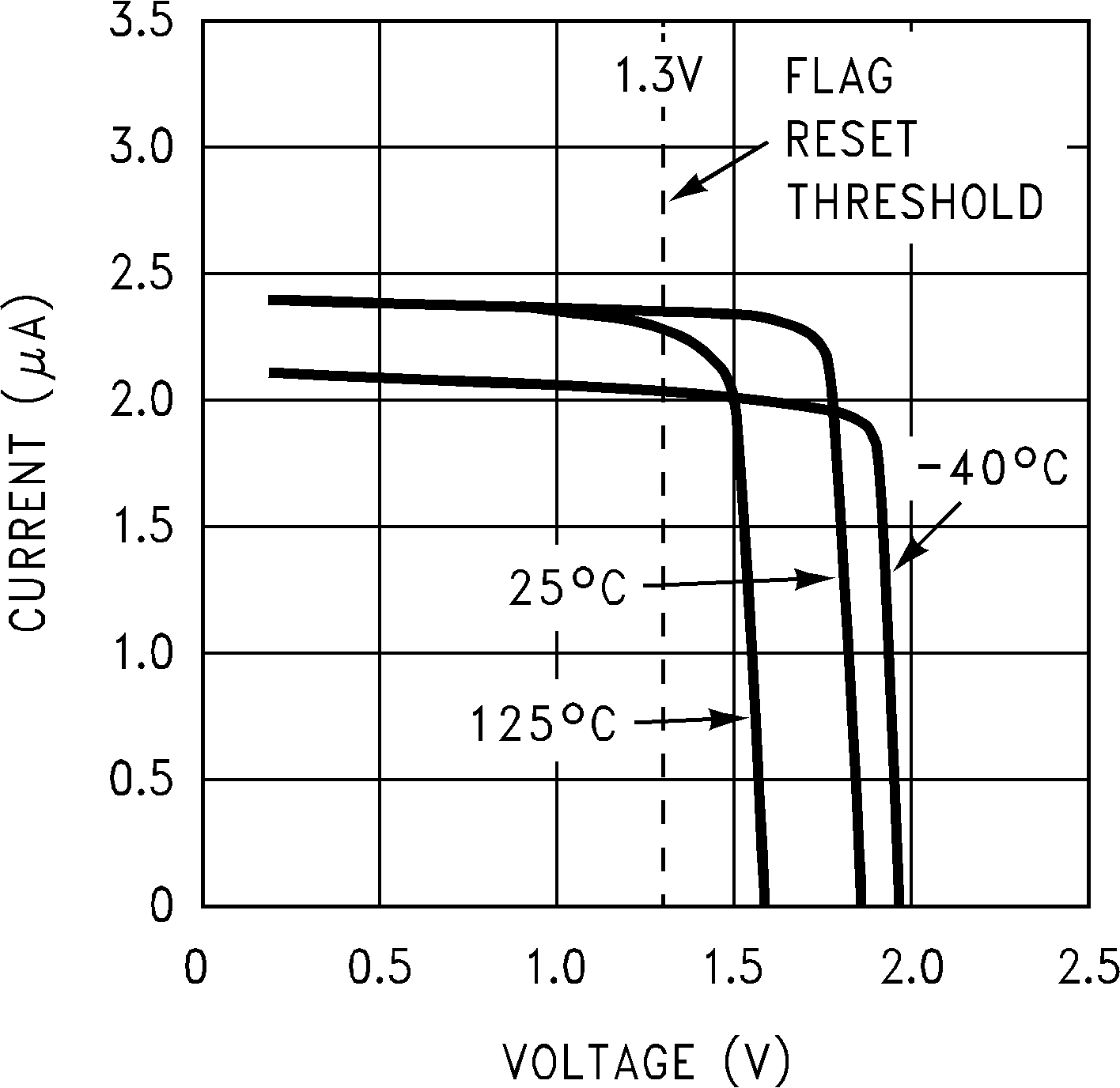

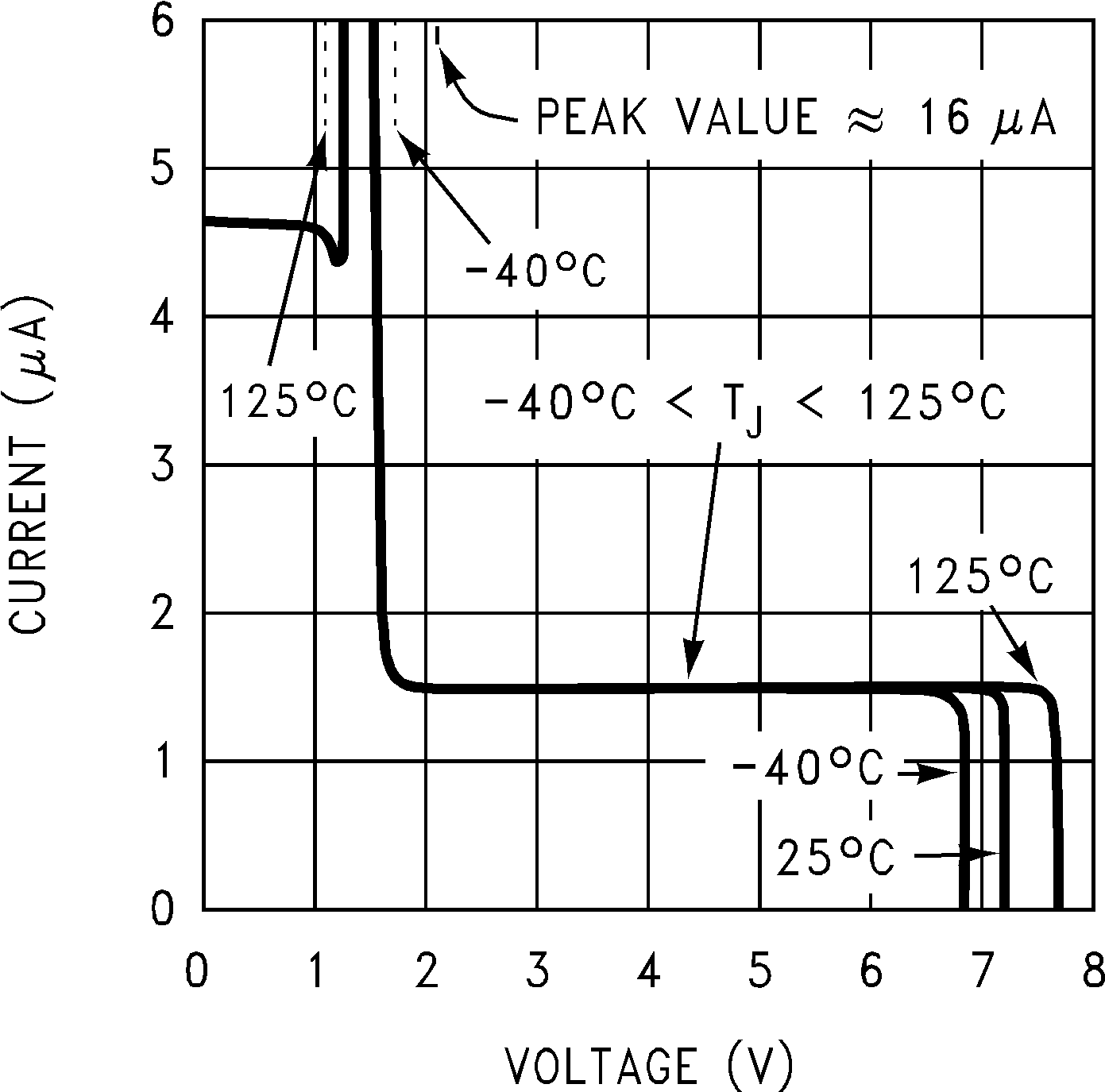

Figure 15. Delay Pin Current

Figure 15. Delay Pin Current

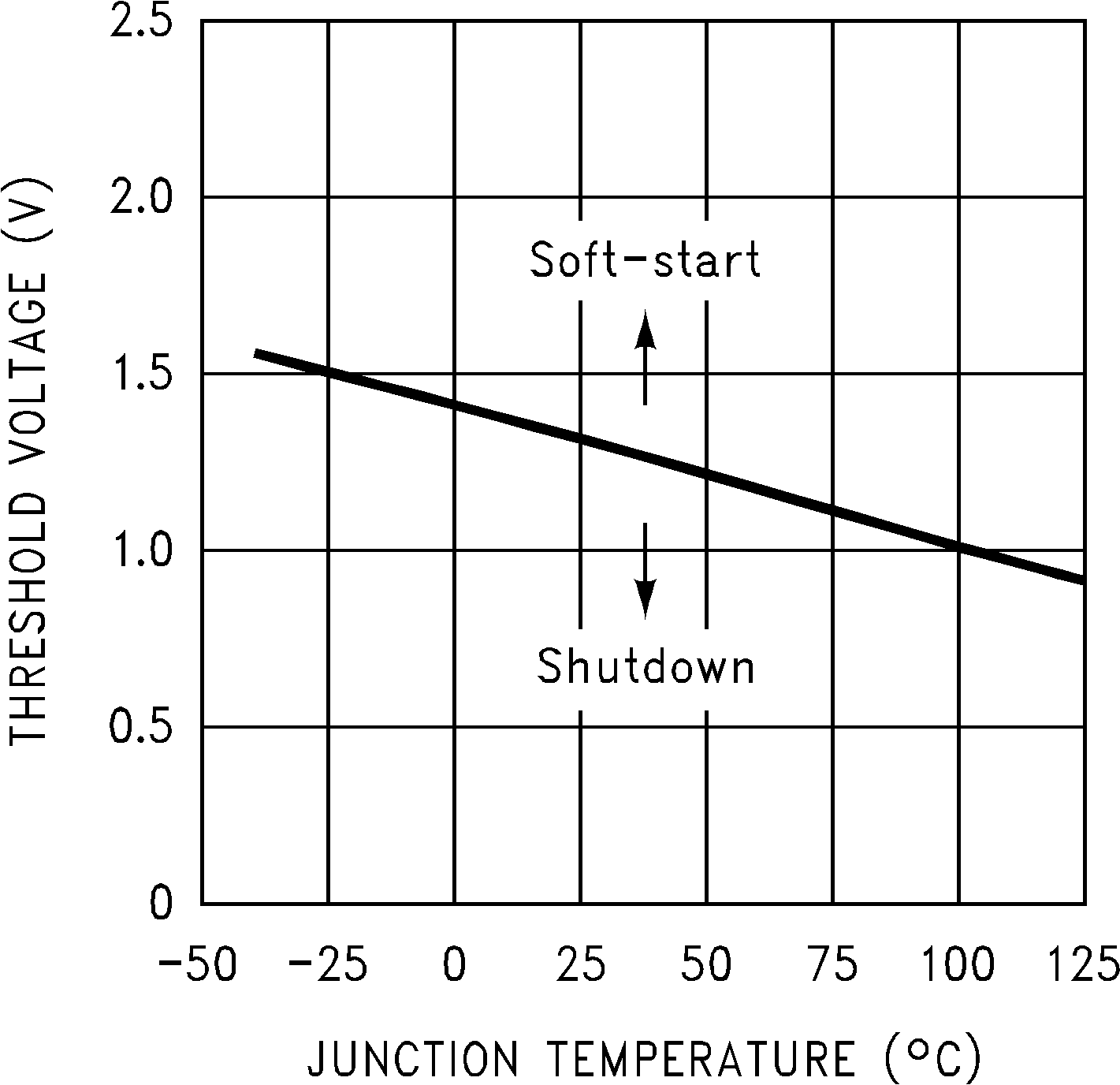

Figure 17. Shutdown and Soft-start Threshold Voltage

Figure 17. Shutdown and Soft-start Threshold Voltage

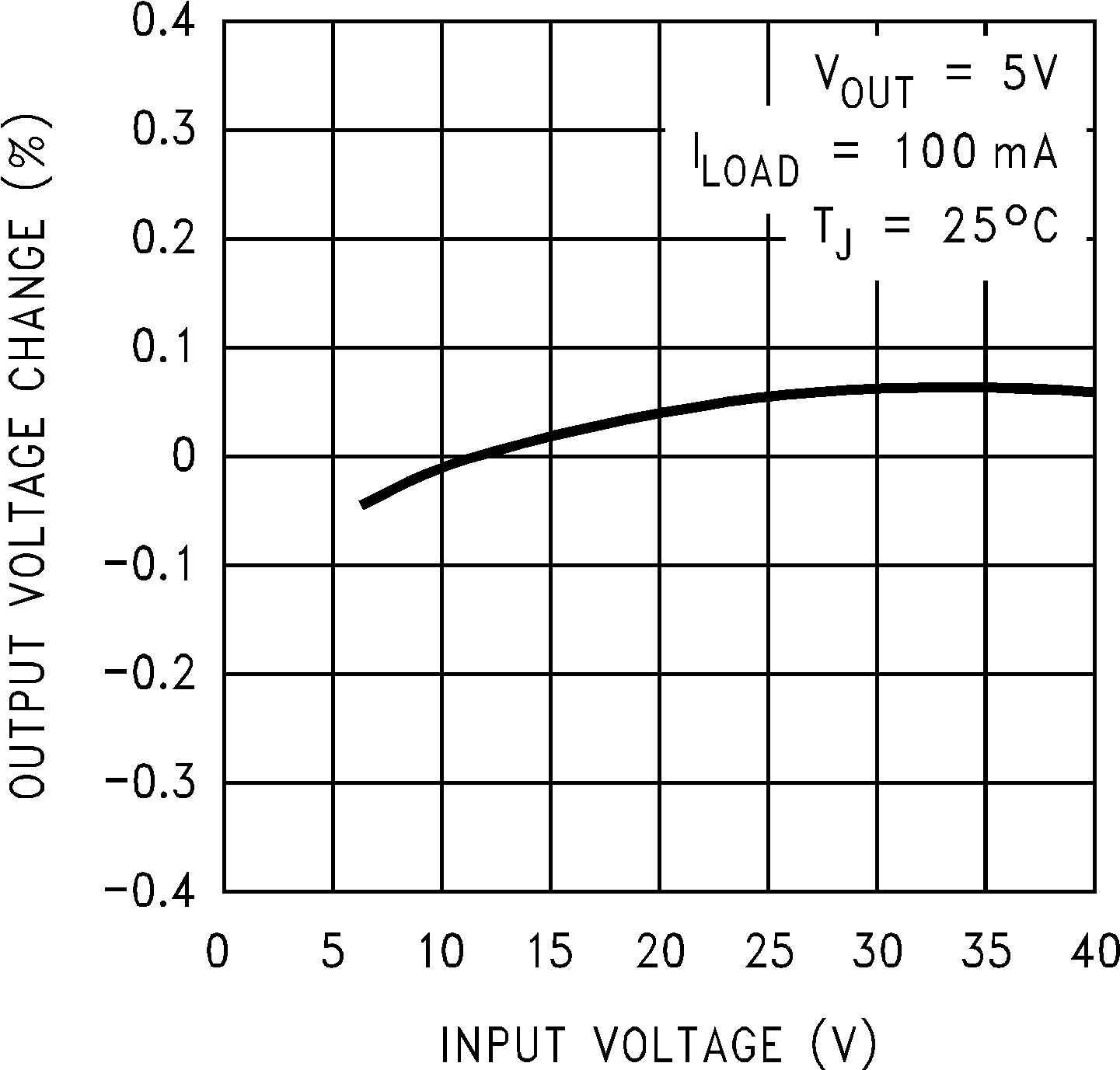

Figure 2. Line Regulation

Figure 2. Line Regulation

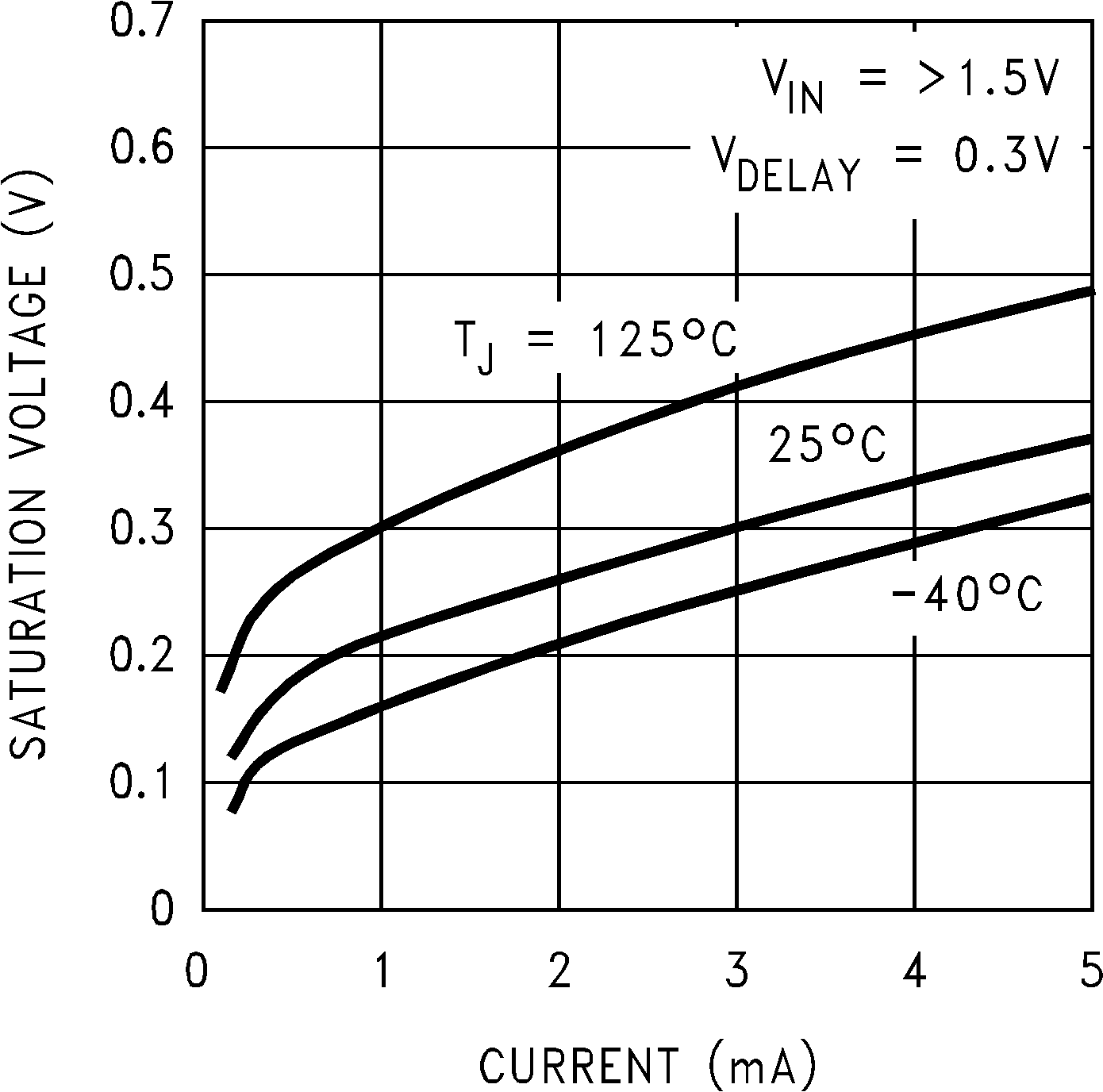

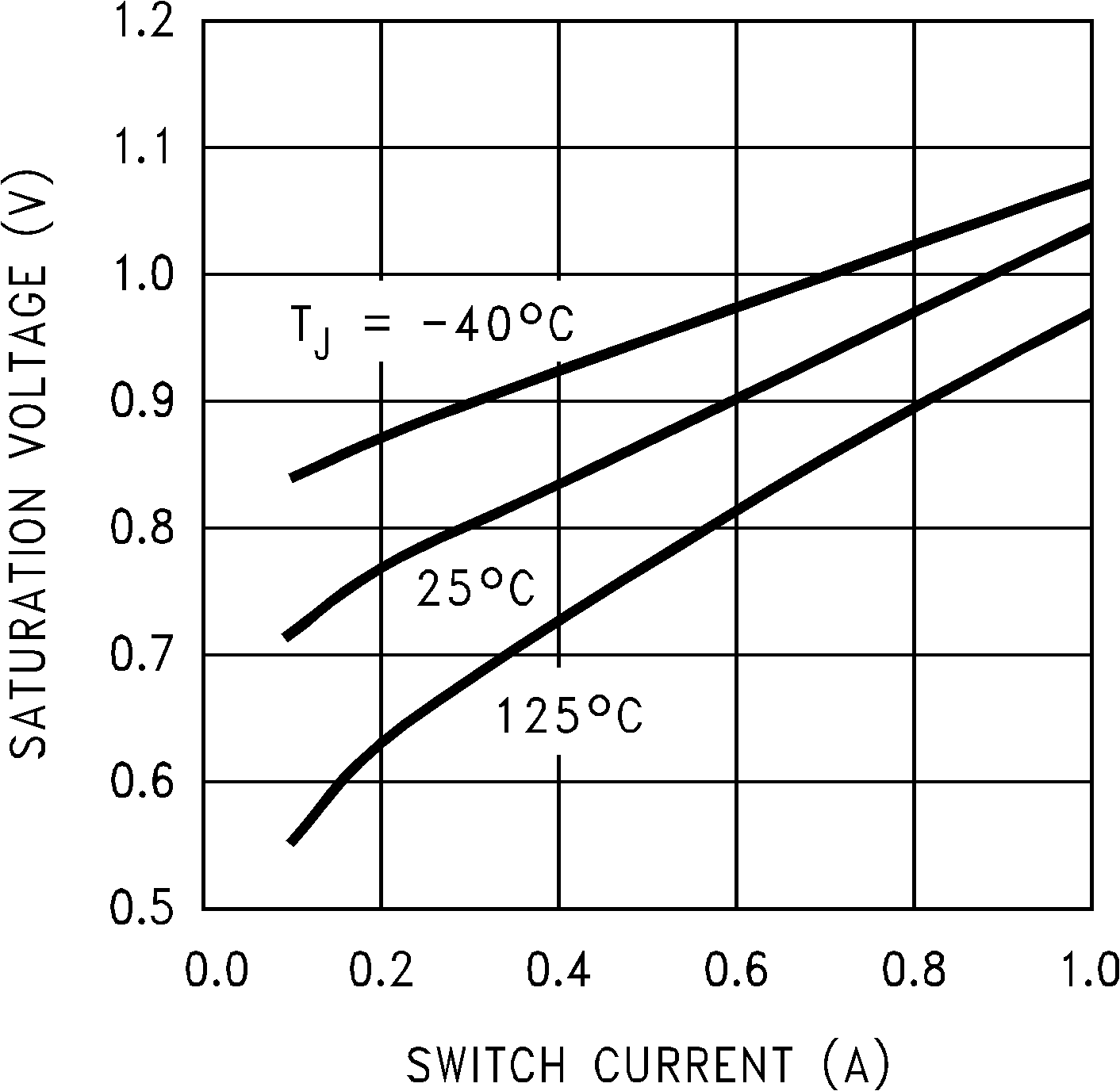

Figure 4. Switch Saturation Voltage

Figure 4. Switch Saturation Voltage

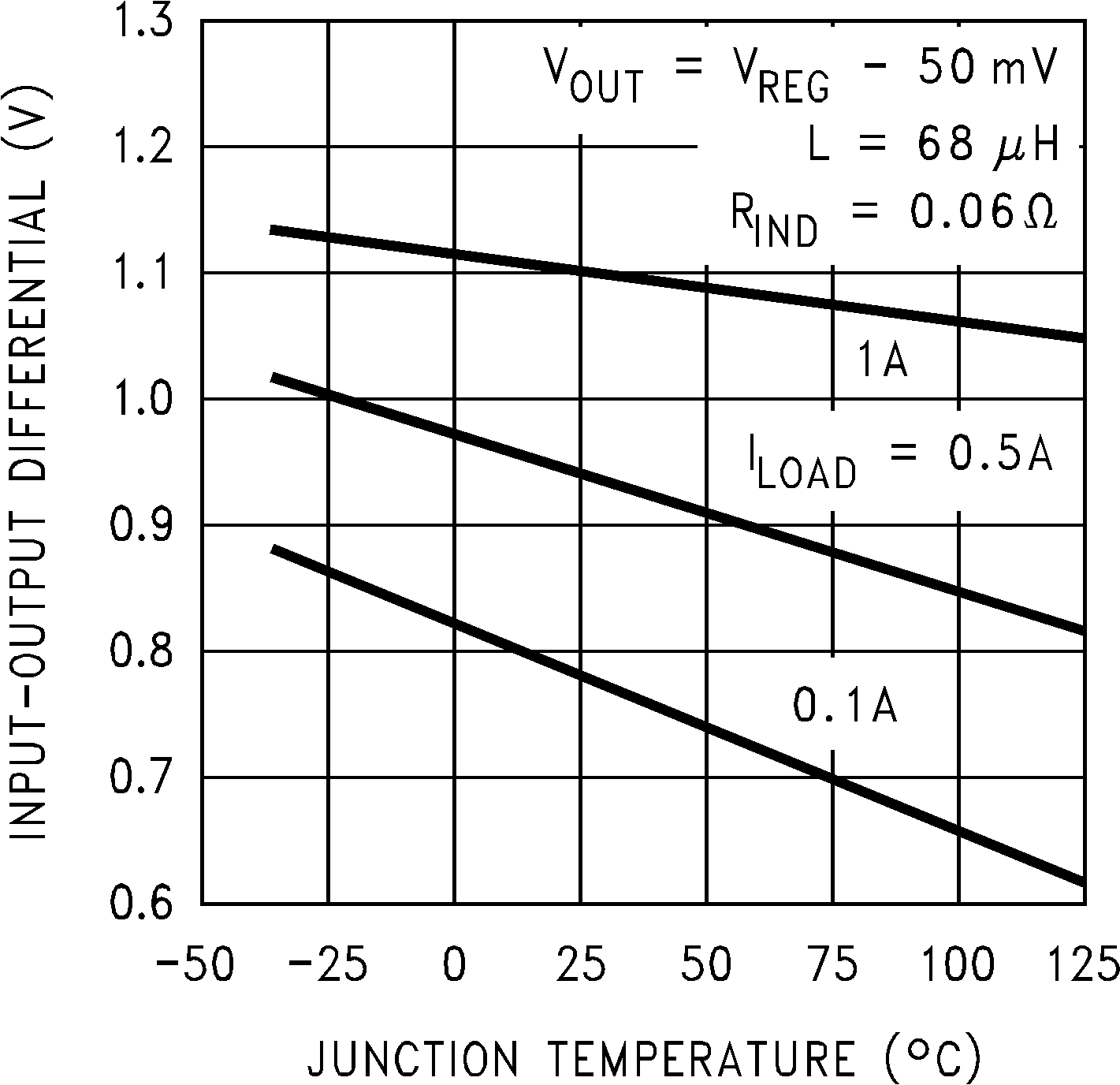

Figure 6. Dropout Voltage

Figure 6. Dropout Voltage

Figure 8. Shutdown Quiescent Current

Figure 8. Shutdown Quiescent Current

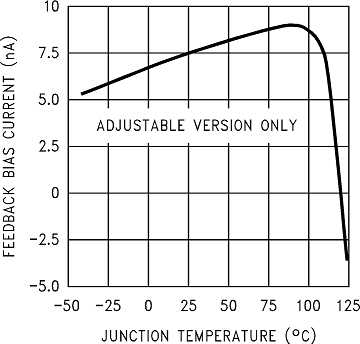

Figure 10. Feedback Pin Bias Current

Figure 10. Feedback Pin Bias Current

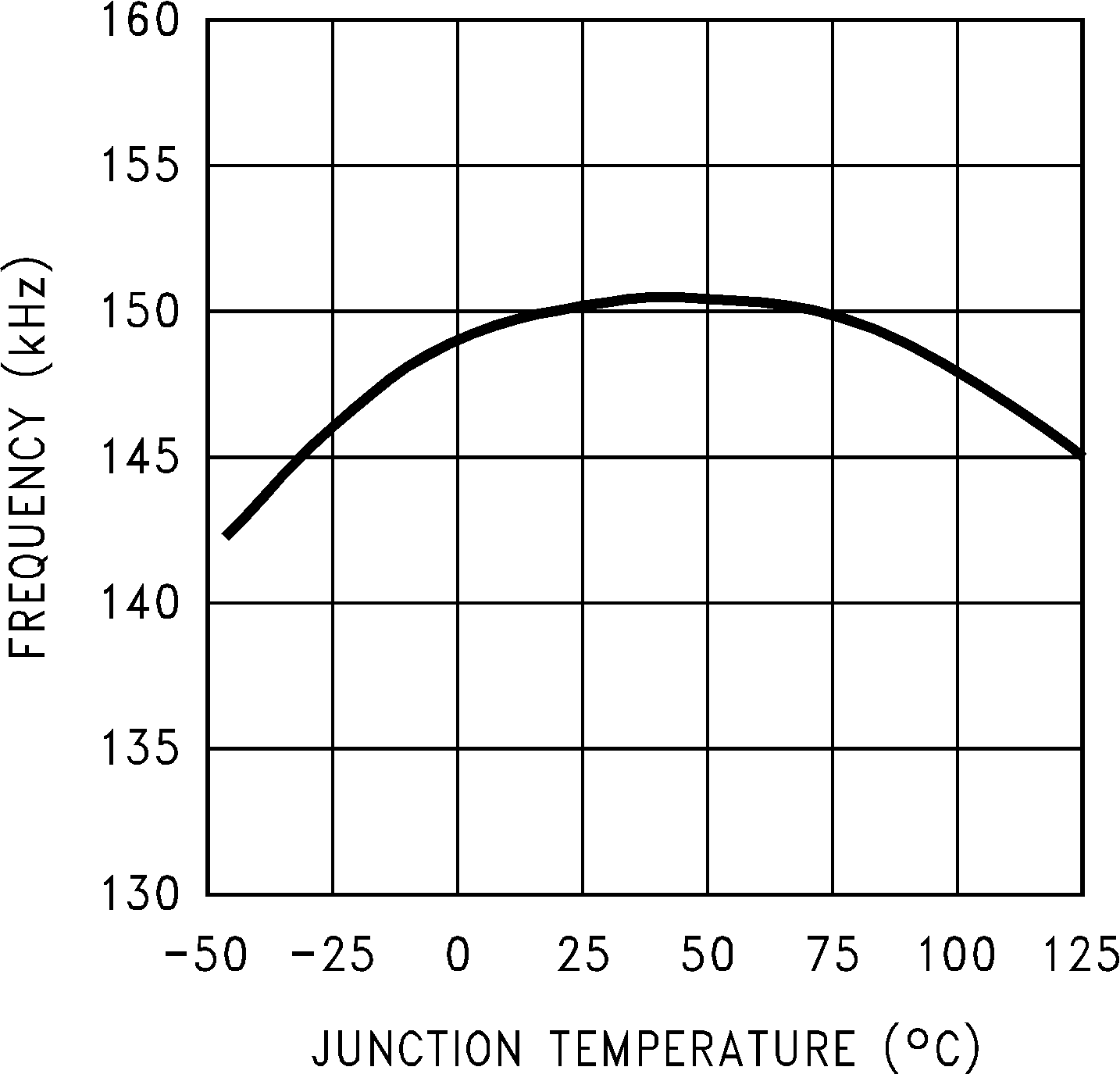

Figure 12. Switching Frequency

Figure 12. Switching Frequency

Figure 14. Shutdown/Soft-start Current

Figure 14. Shutdown/Soft-start Current

Figure 16. Soft-start Response

Figure 16. Soft-start Response