JAJSBZ1C April 2014 – October 2017 LM43602

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Fixed Frequency Peak Current-Mode Controlled Step-Down Regulator

- 7.3.2 Light Load Operation

- 7.3.3 Adjustable Output Voltage

- 7.3.4 Enable (EN)

- 7.3.5 VCC, UVLO and BIAS

- 7.3.6 Soft-Start and Voltage Tracking (SS/TRK)

- 7.3.7 Switching Frequency (RT) and Synchronization (SYNC)

- 7.3.8 Minimum ON-time, Minimum OFF-time and Frequency Foldback at Drop-Out Conditions

- 7.3.9 Internal Compensation and CFF

- 7.3.10 Bootstrap Voltage (BOOT)

- 7.3.11 Power Good (PGOOD)

- 7.3.12 Over Current and Short Circuit Protection

- 7.3.13 Thermal Shutdown

- 7.4 Device Functional Modes

-

8 Applications and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Custom Design With WEBENCH® Tools

- 8.2.2.2 Output Voltage Set-Point

- 8.2.2.3 Switching Frequency

- 8.2.2.4 Input Capacitors

- 8.2.2.5 Inductor Selection

- 8.2.2.6 Output Capacitor Selection

- 8.2.2.7 Feed-Forward Capacitor

- 8.2.2.8 Bootstrap Capacitors

- 8.2.2.9 VCC Capacitor

- 8.2.2.10 BIAS Capacitors

- 8.2.2.11 Soft-Start Capacitors

- 8.2.2.12 Under Voltage Lockout Set-Point

- 8.2.2.13 PGOOD

- 8.2.3 Application Performance Curves

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PWP|16

- DSU|16

サーマルパッド・メカニカル・データ

- PWP|16

発注情報

8 Applications and Implementation

8.1 Application Information

The LM43602 is a step down DC-to-DC regulator. It is typically used to convert a higher DC voltage to a lower DC voltage with a maximum output current of 2 A. The following design procedure can be used to select components for the LM43602. Alternately, the WEBENCH® software may be used to generate complete designs. When generating a design, the WEBENCH® software utilizes iterative design procedure and accesses comprehensive databases of components. Please go to ti.com for more details.

This section presents a simplified discussion of the design process.

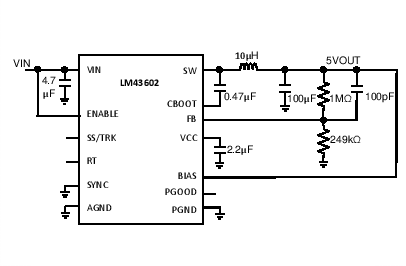

8.2 Typical Applications

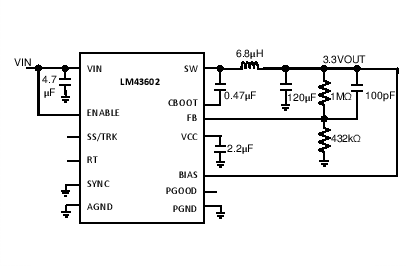

The LM43602 only requires a few external components to convert from a wide voltage range of supply to a fixed output voltage. Figure 36 shows a basic schematic when BIAS is connected to VOUT and this is recommended for VOUT ≥ 3.3 V. For VOUT < 3.3 V, BIAS should be connected to ground, as shown in Figure 37.

Figure 36. LM43602 Basic Schematic for VOUT ≥ 3.3 V, tie BIAS to VOUT

Figure 36. LM43602 Basic Schematic for VOUT ≥ 3.3 V, tie BIAS to VOUT

Figure 37. LM43602 Basic Schematic for VOUT < 3.3 V, tie BIAS to ground

Figure 37. LM43602 Basic Schematic for VOUT < 3.3 V, tie BIAS to ground

The LM43602 also integrates a full list of optional features to aid system design requirements such as: precision enable, VCC UVLO, programmable soft-start, output voltage tracking, programmable switching frequency, clock synchronization and power-good indication. Each application can select the features for a more comprehensive design. A schematic with all features utilized is shown in Figure 38.

Figure 38. LM43602 Schematic with All Features

Figure 38. LM43602 Schematic with All Features

The external components have to fulfill the needs of the application, but also the stability criteria of the device's control loop. The LM43602 is optimized to work within a range of external components. The LC output filter's inductance and capacitance have to be considered in conjunction, creating a double pole, responsible for the corner frequency of the converter (see Output Filter And Loop Stability section). Table 2 can be used to simplify the output filter component selection.

Table 2. L, COUT and CFF Typical Values

| FS (kHz) | VOUT (V) | L (µH)(5) | COUT (µF) (1) | CFF (pF) (2)(3) | RT (kΩ) | RFBB (kΩ) (2)(3) |

|---|---|---|---|---|---|---|

| 200 | 1 | 8.2 | 560 | none | 200 | 100 |

| 500 | 1 | 3.3 | 470 | none | 80.6 or open | 100 |

| 1000 | 1 | 1.5 | 220 | none | 39.2 | 100 |

| 2200 | 1 | 0.68 | 150 | none | 17.8 | 100 |

| 200 | 3.3 | 18 | 250 | 56 | 200 | 432 |

| 500 | 3.3 | 6.8 | 150 | 47 | 80.6 or open | 432 |

| 1000 | 3.3 | 4.7 | 100 | 33 | 39.2 | 432 |

| 2200 | 3.3 | 1.8 | 47 | 22 | 17.8 | 432 |

| 200 | 5 | 22 | 200 | 68 | 200 | 249 |

| 500 | 5 | 10 | 100 | 47 | 80.6 or open | 249 |

| 1000 | 5 | 4.7 | 47 | 47 | 39.2 | 249 |

| 2200 | 5 | 2.2 | 33 | 33 | 17.8 | 249 |

| 200 | 12 | 68 | 68 | See note(4) | 200 | 90.9 |

| 500 | 12 | 27 | 47 | 68 | 80.6 or open | 90.9 |

| 1000 | 12 | 15 | 33 | 47 | 39.2 | 90.9 |

| 200 | 24 | 68 | 68 | See note(4) | 200 | 43.2 |

| 500 | 24 | 27 | 47 | See note(4) | 80.6 or open | 43.2 |

| 1000 | 24 | 15 | 33 | See note(4) | 39.2 | 43.2 |

8.2.1 Design Requirements

Detailed design procedure is described based on a design example. For this design example, use the parameters listed in Table 3 as the input parameters.

Table 3. Design Example Parameters

| DESIGN PARAMETER | VALUE |

|---|---|

| Input voltage VIN | 12 V typical, range from 3.5 V to 36 V |

| Output voltage VOUT | 3.3 V |

| Input ripple voltage | 400 mV |

| Output ripple voltage | 30 mV |

| Output current rating | 2 A |

| Operating frequency | 500 kHz |

| Soft-start time | 10 ms |

8.2.2 Detailed Design Procedure

8.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM43602 device with the WEBENCH® Power Designer.

- Start by entering the input voltage (VIN), output voltage (VOUT), and output current (IOUT) requirements.

- Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

8.2.2.2 Output Voltage Set-Point

The output voltage of the LM43602 device is externally adjustable using a resistor divider network. The divider network is comprised of top feedback resistor RFBT and bottom feedback resistor RFBB. The following equation is used to determine the output voltage of the converter:

Choose the value of the RFBT to be 1 MΩ to minimize quiescent current to improve light load efficiency in this application. With the desired output voltage set to be 3.3 V and the VFB = 1.011 V, the RFBB value can then be calculated using Equation 11. The formula yields a value of 434.78 kΩ. Choose the closest available value of 432 kΩ for the RFBB. Please refer to Adjustable Output Voltage for more details.

8.2.2.3 Switching Frequency

The default switching frequency of the LM43602 device is set at 500 kHz when RT pin is open circuit. The switching frequency is selected to be 500 kHz in this application for one less passive components. If other frequency is desired, use Equation 12 to calculate the required value for RT.

For 500 kHz, the calculated RT is 79.8 kΩ and standard value 80.6 kΩ can also be used to set the switching frequency at 500 kHz.

8.2.2.4 Input Capacitors

The LM43602 device requires high frequency input decoupling capacitor(s) and a bulk input capacitor, depending on the application. The typical recommended value for the high frequency decoupling capacitor is 4.7 µF to 10 µF. A high-quality ceramic type X5R or X7R with sufficiency voltage rating is recommended. The voltage rating must be greater than the maximum input voltage. To compensate the derating of ceramic capactors, a voltage rating of twice the maximum input voltage is recommended. Additionally, some bulk capacitance can be required, especially if the LM43602 circuit is not located within approximately 5 cm from the input voltage source. This capacitor is used to provide damping to the voltage spiking due to the lead inductance of the cable or trace. The value for this capacitor is not critical but must be rated to handle the maximum input voltage including ripple. For this design, a 10 µF, X7R dielectric capacitor rated for 100 V is used for the input decoupling capacitor. The equivalent series resistance (ESR) is approximately 3 mΩ, and the current-rating is 3 A. Include a capacitor with a value of 0.1 µF for high-frequency filtering and place it as close as possible to the device pins.

NOTE

DC Bias effect: High capacitance ceramic capacitors have a DC Bias effect, which will have a strong influence on the final effective capacitance. Therefore the right capacitor value has to be chosen carefully. Package size and voltage rating in combination with dielectric material are responsible for differences between the rated capacitor value and the effective capacitance.

8.2.2.5 Inductor Selection

The first criterion for selecting an output inductor is the inductance itself. In most buck converters, this value is based on the desired peak-to-peak ripple current, ΔiL, that flows in the inductor along with the DC load current. As with switching frequency, the selection of the inductor is a tradeoff between size and cost. Higher inductance gives lower ripple current and hence lower output voltage ripple with the same output capacitors. Lower inductance could result in smaller, less expensive component. An inductance that gives a ripple current of 20% to 40% of the 2 A at the typical supply voltage is a good starting point. ΔIL = (1/5 to 2/5) x IOUT. The peak-to-peak inductor current ripple can be found by Equation 13 and the range of inductance can be found by Equation 14 with the typical input voltage used as VIN.

D is the duty cycle of the converter which in a buck converter can be approximated as D = VIN/VOUT, assuming no loss power conversion. By calculating in terms of amperes, volts, and megahertz, the inductance value will come out in micro henries. The inductor ripple current ratio is defined by:

The second criterion is the inductor saturation current rating. The inductor should be rated to handle the maximum load current plus the ripple current:

The LM43602 has both valley current limit and peak current limit. During an instantaneous short, the peak inductor current can be high due to a momentary increase in duty cycle. The inductor current rating should be higher than the HS current limit. It is advised to select an inductor with a larger core saturation margin and preferably a softer roll off of the inductance value over load current.

In general, it is preferable to choose lower inductance in switching power supplies, because it usually corresponds to faster transient response, smaller DCR, and reduced size for more compact designs. But too low of an inductance can generate too large of an inductor current ripple such that over current protection at the full load could be falsely triggered. It also generates more conduction loss, since the RMS current is slightly higher relative that with lower current ripple at the same DC current. Larger inductor current ripple also implies larger output voltage ripple with the same output capacitors. With peak current mode control, it is not recommended to have too small of an inductor current ripple. A larger peak current ripple improves the comparator signal to noise ratio.

Once the inductance is determined, the type of inductor must be selected. Ferrite designs have very low core losses and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates hard, which means that inductance collapses abruptly when the peak design current is exceeded. The ‘hard’ saturation results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate!

For the design example, a standard 6.8 μH inductor from Wurth, Coiltronics, or Vishay can be used for the 3.3 V output with plenty of current rating margin.

8.2.2.6 Output Capacitor Selection

The device is designed to be used with a wide variety of LC filters. It is generally desired to use as little output capacitance as possible to keep cost and size down. The output capacitor (s), COUT, should be chosen with care since it directly affects the steady state output voltage ripple, loop stability and the voltage over/undershoot during load current transients.

The output voltage ripple is essentially composed of two parts. One is caused by the inductor current ripple going through the Equivalent Series Resistance (ESR) of the output capacitors:

The other is caused by the inductor current ripple charging and discharging the output capacitors:

The two components in the voltage ripple are not in phase, so the actual peak-to-peak ripple is smaller than the sum of the two peaks.

Output capacitance is usually limited by transient performance specifications if the system requires tight voltage regulation in the presence of large current steps and fast slew rates. When a fast large load transient happens, output capacitors provide the required charge before the inductor current can slew to the appropriate level. The initial output voltage step is equal to the load current step multiplied by the ESR. VOUT continues to droop until the control loop response increases or decreases the inductor current to supply the load. To maintain a small over- or undershoot during a transient, small ESR and large capacitance are desired. But these also come with higher cost and size. Thus, the motivation is to seek a fast control loop response to reduce the output voltage deviation.

For a given input and output requirement, the following inequality gives an approximation for an absolute minimum output cap required:

Along with this for the same requirement, the max ESR should be calculated as per the following inequality

where

r = Ripple ratio of the inductor ripple current (ΔIL / IOUT)

ΔVOUT = Target output voltage undershoot

D’ = 1 – Duty cycle

FS = Switching Frequency

IOUT = Load Current

A general guide line for COUT range is that COUT should be larger than the minimum required output capacitance calculated by Equation 19, and smaller than 10 times the minimum required output capacitance or 1 mF. In applications with VOUT less than 3.3 V, it is critical that low ESR output capacitors are selected. This will limit potential output voltage overshoots as the input voltage falls below the device normal operating range. To optimize the transient behavior a feed-forward capacitor could be added in parallel with the upper feedback resistor. For this design example, three 47 µF,10 V, X7R ceramic capacitors are used in parallel.

8.2.2.7 Feed-Forward Capacitor

The LM43602 is internally compensated and the internal R-C values are 400 kΩ and 50 pF respectively. Depending on the VOUT and frequency FS, if the output capacitor COUT is dominated by low ESR (ceramic types) capacitors, it could result in low phase margin. To improve the phase boost an external feedforward capacitor CFF can be added in parallel with RFBT. CFF is chosen such that phase margin is boosted at the crossover frequency without CFF. A simple estimation for the crossover frequency without CFF (fx) is shown in Equation 21, assuming COUT has very small ESR.

The following equation for CFF was tested:

This equation indicates that the crossover frequency is geometrically centered on the zero and pole frequencies caused by the CFF capacitor.

For designs with higher ESR, CFF is not neeed when COUT has very high ESR and CFF calculated from Equation 22 should be reduced with medium ESR. Table 2 can be used as a quick starting point.

For the application in this design example, a 100 pF COG capacitor is selected.

8.2.2.8 Bootstrap Capacitors

Every LM43602 design requires a bootstrap capacitor, CBOOT. The recommended bootstrap capacitor is 0.47 μF and rated at 6.3 V or higher. The bootstrap capacitor is located between the SW pin and the CBOOT pin. The bootstrap capacitor must be a high-quality ceramic type with X7R or X5R grade dielectric for temperature stability.

8.2.2.9 VCC Capacitor

The VCC pin is the output of an internal LDO for LM43602. The input for this LDO comes from either VIN or BIAS (please refer to Functional Block Diagram for LM43602). To insure stability of the part, place a minimum of 2.2 µF, 10 V capacitor from this pin to ground.

8.2.2.10 BIAS Capacitors

For an output voltage of 3.3 V and greater, the BIAS pin can be connected to the output in order to increase light load efficiency. This pin is an input for the VCC LDO. When BIAS is not connected, the input for the VCC LDO will be internally connected into VIN. Since this is an LDO, the voltage differences between the input and output will affect the efficiency of the LDO. If necessary, a capacitor with a value of 1 μF can be added close to the BIAS pin as an input capacitor for the LDO.

8.2.2.11 Soft-Start Capacitors

The user can left the SS/TRK pin floating and the LM43602 will implement a soft start time of 4.1 ms typically. In order to use an external soft start capacitor, the capacitor should be sized such that the soft start time will be longer than 4.1 ms. Use the following equation in order to calculate the soft start capacitor value:

Where,

CSS = Soft start capacitor value (µF)

ISS = Soft start charging current (µA)

tSS = Desired soft start time (s)

For the desired soft start time of 10 ms and soft start charging current of 2.0 µA, the equation above yield a soft start capacitor value of 0.020 µF.

8.2.2.12 Under Voltage Lockout Set-Point

The undervoltage lockout (UVLO) is adjusted using the external voltage divider network of RENT and RENB. RENT is connected between VIN and the EN pin of the LM43602 device. RENB is connected between the EN pin and the GND pin. The UVLO has two thresholds, one for power up when the input voltage is rising and one for power down or brown outs when the input voltage is falling. The following equation can be used to determine the VIN (UVLO) level.

The EN rising threshold (VENH) for LM43602 is set to be 2.2 V (typical). Choose the value of RENB to be 1 MΩ to minimize input current from the supply. If the desired VIN UVLO level is at 5.0 V, then the value of RENT can be calculated using the equation below:

The above equation yields a value of 1.27 MΩ. The resulting falling UVLO threshold, equals 4.3 V, can be calculated by below equation, where EN falling threshold (VENL) is 1.9 V (typical).

8.2.2.13 PGOOD

A typical pull-up resistor value is 10 kΩ to 100 kΩ from PGOOD pin to a voltage no higher than 12 V. If it is desired to pull up PGOOD pin to a voltage higher than 12 V, a resistor can be added from PGOOD pin to ground to divide the voltage seen by the PGOOD pin to a value no higher than 12 V.

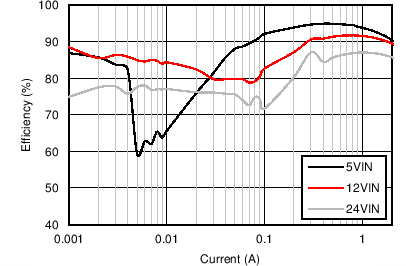

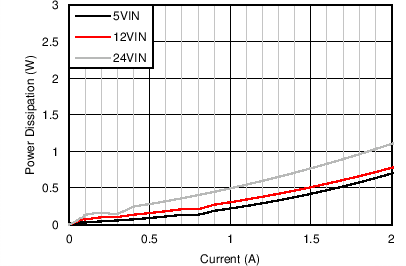

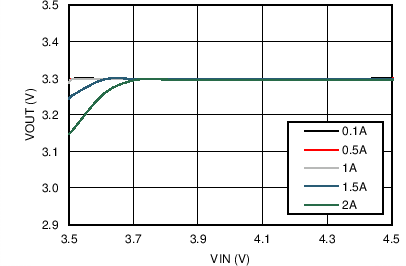

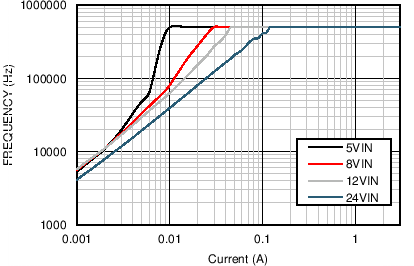

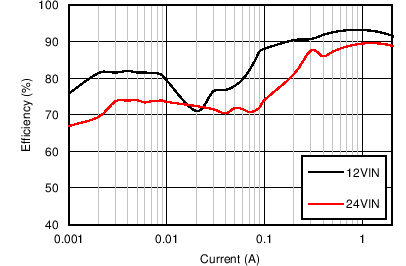

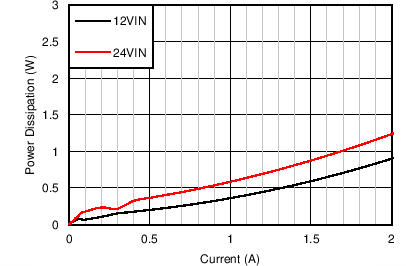

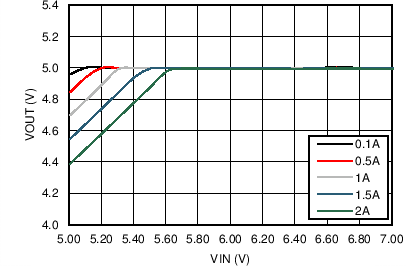

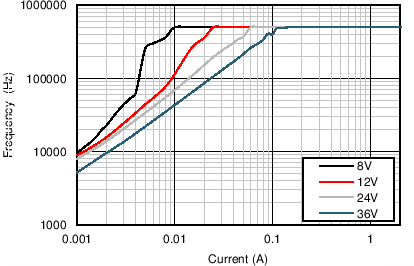

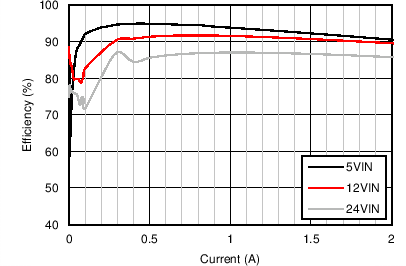

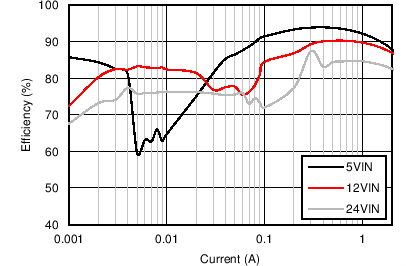

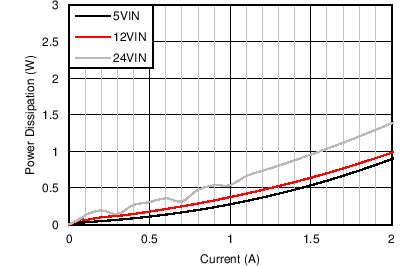

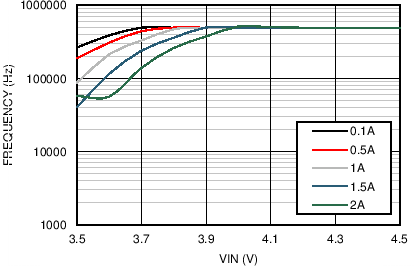

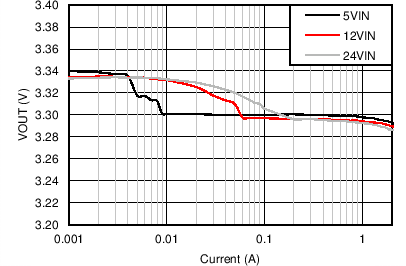

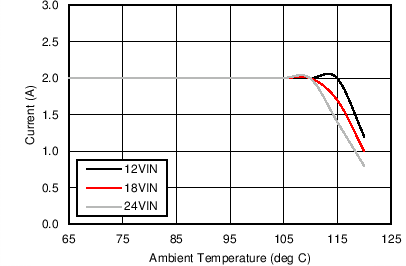

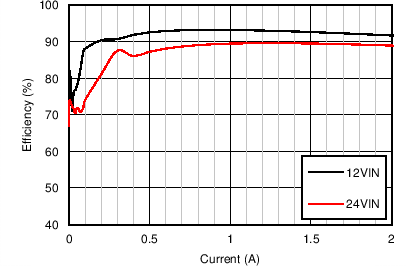

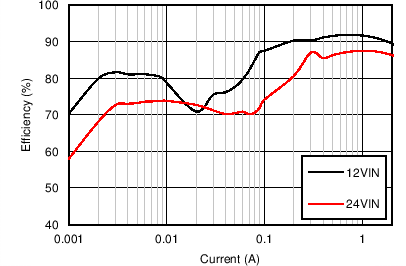

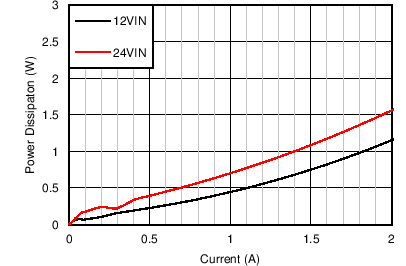

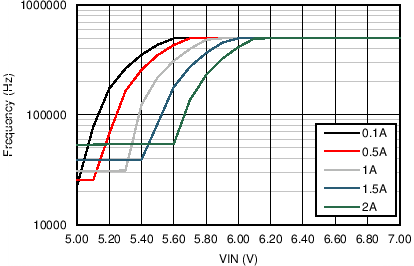

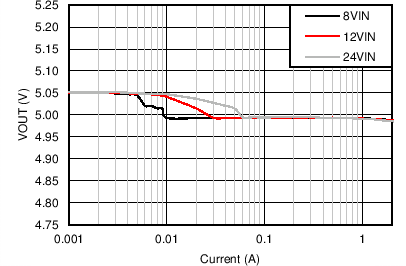

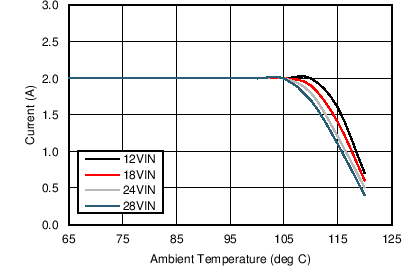

8.2.3 Application Performance Curves

Unless otherwise specified, VIN = 12V, VOUT = 3.3 V, FS = 500 kHz. Please refer to Application Performance Curves for Bill of materials for each VOUT and FS combination.

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz | VIN =12 V |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 1 MHz | VIN = 12V |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz | VIN = 24 V |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 3.3 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |

| VOUT = 5 V | FS = 500 kHz |