JAJSL65A February 2023 – January 2025 LM5148-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 概要 (続き)

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Input Voltage Range (VIN)

- 7.3.2 High-Voltage Bias Supply Regulator (VCC, VCCX, VDDA)

- 7.3.3 Precision Enable (EN)

- 7.3.4 Power-Good Monitor (PG)

- 7.3.5 Switching Frequency (RT)

- 7.3.6 Dual Random Spread Spectrum (DRSS)

- 7.3.7 Soft Start

- 7.3.8 Output Voltage Setpoint (FB)

- 7.3.9 Minimum Controllable On Time

- 7.3.10 Error Amplifier and PWM Comparator (FB, EXTCOMP)

- 7.3.11 Slope Compensation

- 7.3.12 Inductor Current Sense (ISNS+, VOUT)

- 7.3.13 Hiccup Mode Current Limiting

- 7.3.14 High-Side and Low-Side Gate Drivers (HO, LO)

- 7.3.15 Output Configurations (CNFG)

- 7.3.16 Single-Output Dual-Phase Operation

- 7.4 Device Functional Modes

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1

Design 1 – High Efficiency 2.1MHz Synchronous

Buck Regulator

- 8.2.1.1 Design Requirements

- 8.2.1.2

Detailed Design Procedure

- 8.2.1.2.1 Custom Design with WEBENCH® Tools

- 8.2.1.2.2 Custom Design with Excel Quickstart Tool

- 8.2.1.2.3 Buck Inductor

- 8.2.1.2.4 Current-Sense Resistance

- 8.2.1.2.5 Output Capacitors

- 8.2.1.2.6 Input Capacitors

- 8.2.1.2.7 Frequency Set Resistor

- 8.2.1.2.8 Feedback Resistors

- 8.2.1.2.9 Compensation Components

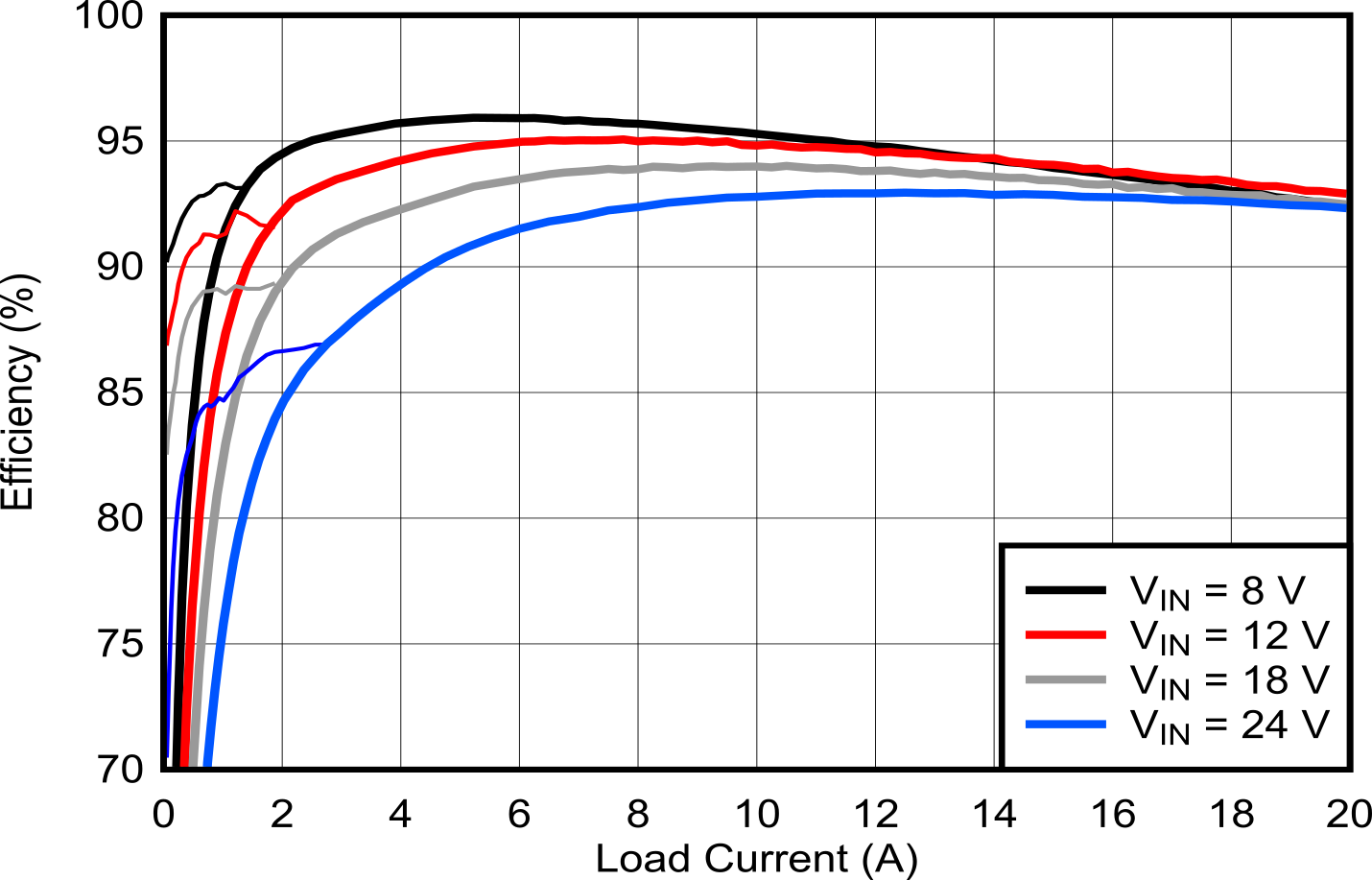

- 8.2.1.3 Application Curves

- 8.2.2 Design 2 – High Efficiency 48-V to 12-V 400-kHz Synchronous Buck Regulator

- 8.2.3 Design 3 – High Efficiency 440-kHz Synchronous Buck Regulator

- 8.2.4 Design 4 – Dual-Phase 400-kHz 20-A Synchronous Buck Regulator

- 8.2.1

Design 1 – High Efficiency 2.1MHz Synchronous

Buck Regulator

- 8.3 Power Supply Recommendations

- 8.4 Layout

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

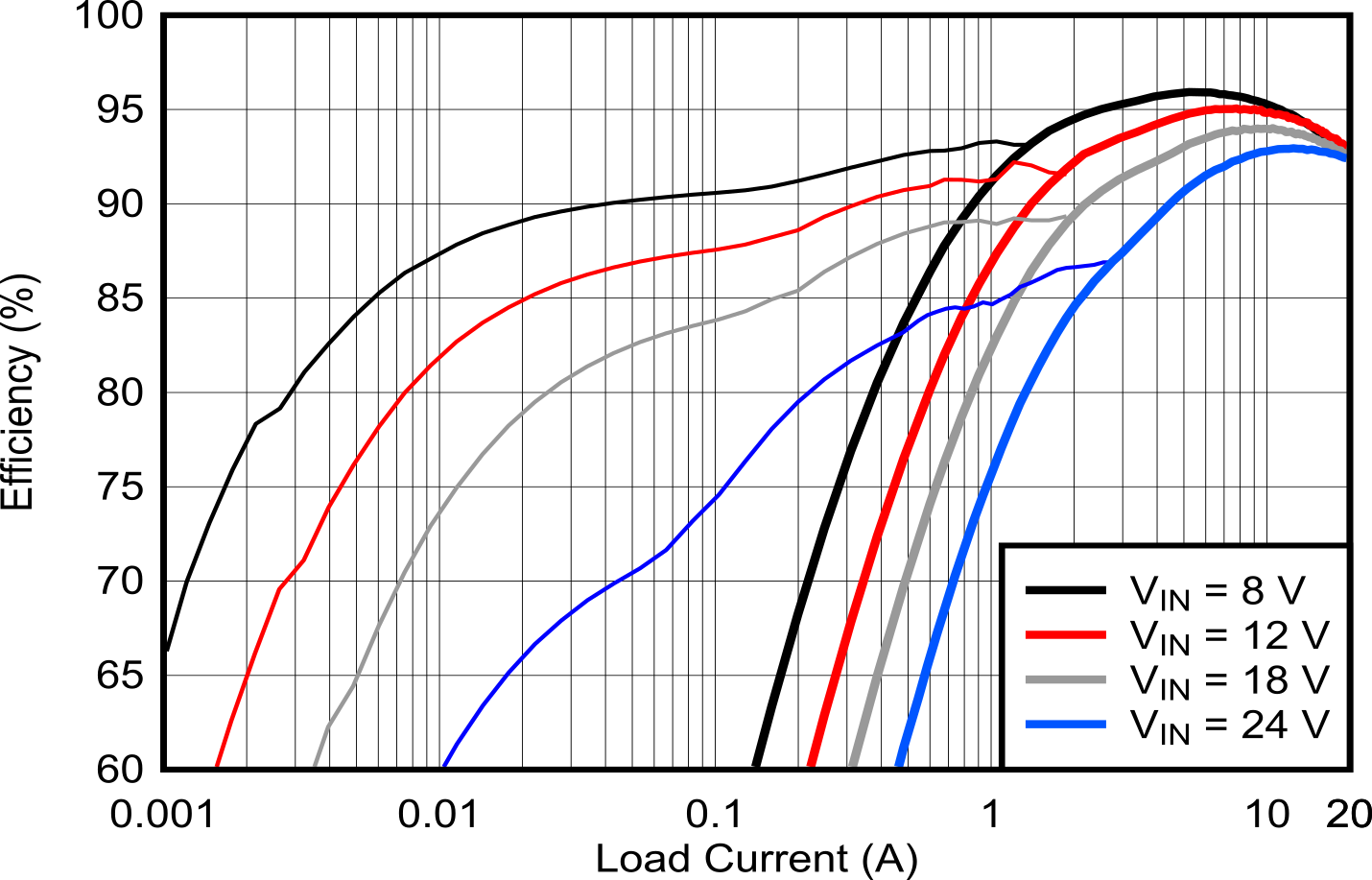

8.2.4.3 Application Curves

| 3.3-V output | |||

| VIN step to 12 V | 20-A load |

| VIN = 12 V | FPWM |

| 3.3-V output |

| VIN = 12 V | 20-A load |

| VIN = 12 V | FPWM |