JAJSGD5E October 2014 – October 2018 LM5160 , LM5160A

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

LM5160 Synchronous Buck (10-V to 60-V Input, 5-V Output, 1.5-A Load)

- 9.2.1.1 Design Requirements

- 9.2.1.2

Detailed Design Procedure

- 9.2.1.2.1 Custom Design With WEBENCH® Tools

- 9.2.1.2.2 Feedback Resistor Divider - RFB1, RFB2

- 9.2.1.2.3 Switching Frequency - RON

- 9.2.1.2.4 Inductor - L

- 9.2.1.2.5 Output Capacitor - COUT

- 9.2.1.2.6 Series Ripple Resistor - RESR

- 9.2.1.2.7 VCC and Bootstrap Capacitors - CVCC, CBST

- 9.2.1.2.8 Input Capacitor - CIN

- 9.2.1.2.9 Soft-Start Capacitor - CSS

- 9.2.1.2.10 EN/UVLO Resistors - RUV1, RUV2

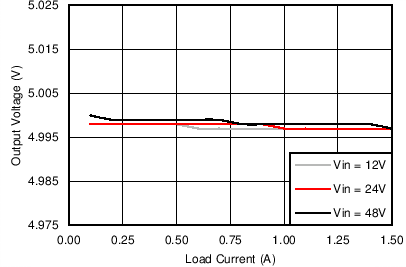

- 9.2.1.3 Application Curves

- 9.2.2 LM5160 Isolated Fly-Buck (18-V to 32-V Input, 12-V, 4.5-W Isolated Output)

- 9.2.3 LM5160A Isolated Fly-Buck (18-V to 32-V Input, 12-V, 4.5-W Isolated Output)

- 9.2.1

LM5160 Synchronous Buck (10-V to 60-V Input, 5-V Output, 1.5-A Load)

- 9.3 Do's and Don'ts

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

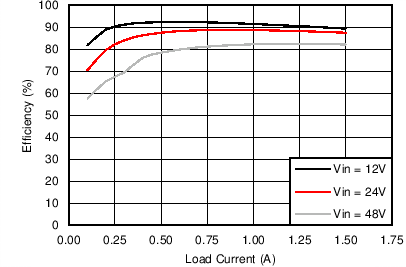

9.2.1.3 Application Curves

Figure 22. EN/UVLO Start-Up at VIN= 24 V and IOUT = 1 A

Figure 22. EN/UVLO Start-Up at VIN= 24 V and IOUT = 1 A  Figure 24. EN/UVLO Start-Up at VIN= 24 V and

Figure 24. EN/UVLO Start-Up at VIN= 24 V and

RLOAD = 100 Ω

Figure 26. Load Transient (300 mA – 1.5 A) at VIN = 24 V With Type 3 Ripple Configuration

Figure 26. Load Transient (300 mA – 1.5 A) at VIN = 24 V With Type 3 Ripple Configuration  Figure 21. Efficiency vs IOUT

Figure 21. Efficiency vs IOUT  Figure 23. Prebias Start-Up at VIN= 48 V and RLOAD = 3 Ω

Figure 23. Prebias Start-Up at VIN= 48 V and RLOAD = 3 Ω  Figure 25. Start-Up at VIN= 48 V and RLOAD = 10 Ω

Figure 25. Start-Up at VIN= 48 V and RLOAD = 10 Ω  Figure 27. Output Short-Circuit at VIN = 48 V

Figure 27. Output Short-Circuit at VIN = 48 V