JAJSTE0A March 2024 – December 2025 LMK05318B-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 説明

- 4 デバイスの比較

- 5 ピン構成および機能

- 6 仕様

- 7 パラメータ測定情報

-

8 詳細説明

- 8.1 概要

- 8.2 機能ブロック図

- 8.3

機能説明

- 8.3.1 発振器入力 (XO_P/N)

- 8.3.2 リファレンス入力 (PRIREF_P/N と SECREF_P/N)

- 8.3.3 クロック入力インターフェイスおよび終端

- 8.3.4 リファレンス入力マルチプレクサの選択

- 8.3.5 ヒットレス スイッチング

- 8.3.6 リファレンス入力でのギャップド クロックのサポート

- 8.3.7 入力クロックおよび PLL 監視、ステータス、割り込み

- 8.3.8

PLL の関係

- 8.3.8.1 PLL 周波数の関係

- 8.3.8.2 アナログ PLL (APLL1、APLL2)

- 8.3.8.3 APLL のリファレンスの経路

- 8.3.8.4 APLL の位相周波数検出器 (PFD) とチャージ ポンプ

- 8.3.8.5 APLL の帰還分周器の経路

- 8.3.8.6 APLL のループ フィルタ (LF1、LF2)

- 8.3.8.7 APLL の電圧制御発振器 (VCO1、VCO2)

- 8.3.8.8 APLL の VCO クロック分配の経路 (P1、P2)

- 8.3.8.9 DPLL のリファレンス (R) 分周器の経路

- 8.3.8.10 DPLL の時間 / デジタル コンバータ (TDC)

- 8.3.8.11 DPLL のループ フィルタ (DLF)

- 8.3.8.12 DPLL の帰還 (FB) 分周器の経路

- 8.3.9 出力クロックの分配

- 8.3.10 出力チャネル マルチプレクサ

- 8.3.11 出力分周器 (OD)

- 8.3.12 クロック出力 (OUTx_P/N)

- 8.3.13 出力クロックの起動時のグリッチなし

- 8.3.14 クロック出力のインターフェイスと終端

- 8.3.15 出力同期 (SYNC)

- 8.3.16 1PPS 入力から出力の位相整列 (PRIREF から OUT7 同期)

- 8.4 デバイスの機能モード

- 8.5 プログラミング

- 9 アプリケーションと実装

- 10デバイスおよびドキュメントのサポート

- 11改訂履歴

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- RGZ|48

サーマルパッド・メカニカル・データ

- RGZ|48

発注情報

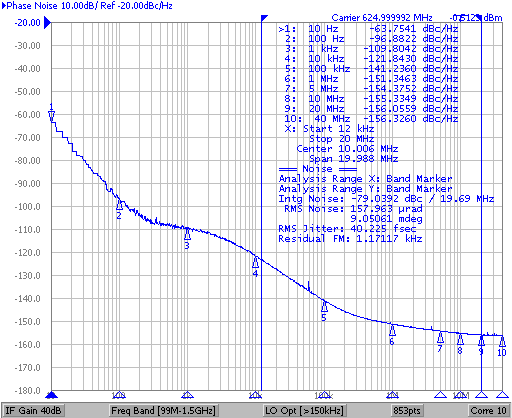

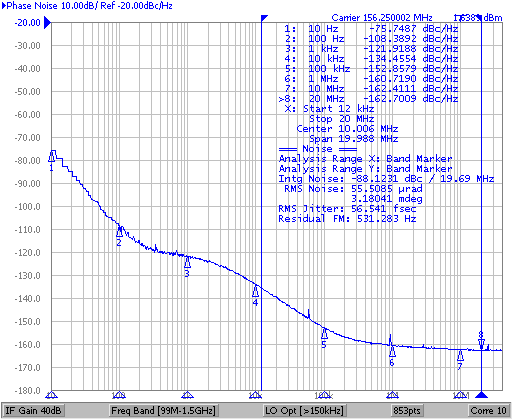

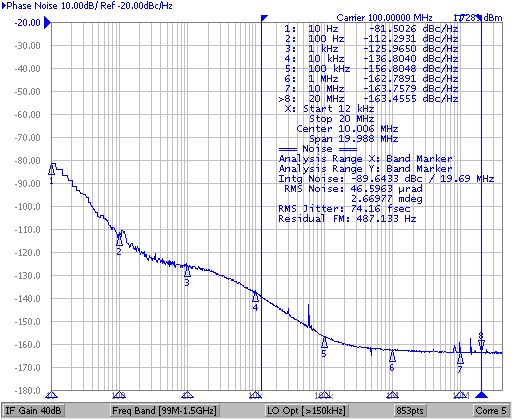

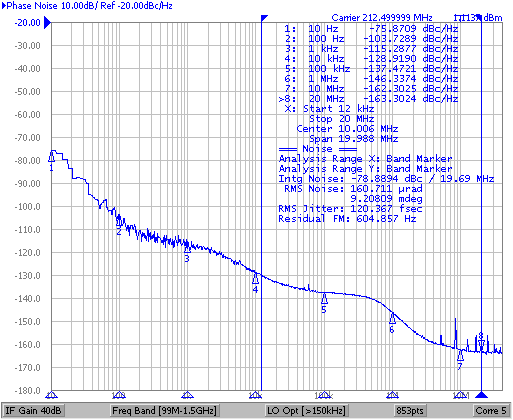

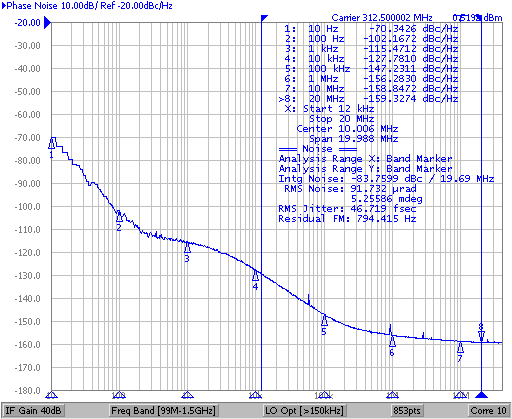

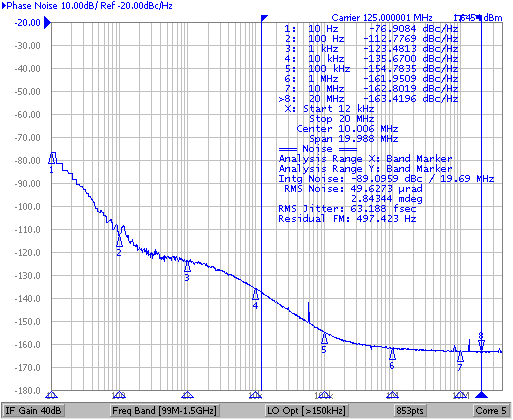

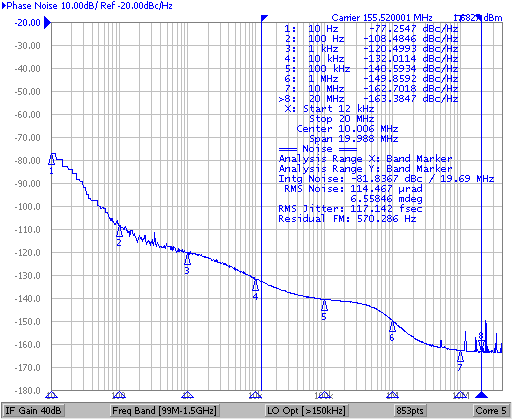

6.8 代表的特性

特に記述のない限り以下のとおり:VDD = 3.3V、VDDO = 1.8V、TA = 25°C、AC-LVPECL 出力測定値。DPLL:fREF = 25MHz、fTDC = 25MHz、BW DPLL = 10Hz、DPLL はリファレンスにロック。APLL1:fXO = 48MHz、fPD1 = 24MHz (fXO÷2) 、fVCO1 = 2500MHz、BW APLL1 = 2.5kHz、DPLL モード。APLL2:fPD2 = 138。8MHz (fVCO1÷18) 、BW APLL2 = 500kHz、APLL2 のカスケード モードは図 6-10および図 6-11です。さまざまな周波数オフセットでの PLL 出力クロックの位相ノイズは、外部クロック入力源 (REF IN、OCXO、XO) 、内部ノイズ源 (PLL、VCO) 、および構成済みの PLL ループ帯域幅 (BW REF-DPLL、BW TCXO-DPLL、BW APLL) など、さまざまなノイズの寄与要因によって決定されます。各外部クロック ソース (fSOURCE) に示される位相ノイズ プロファイルは、ソースで測定された位相ノイズに 20×LOG 10 (fOUT / fSOURCE) を追加し、PLL 出力周波数 (fOUT) によって正規化されます。

| ジッタ = 40fs RMS (12kHz ~ 20MHz) |

| DPLL モード (APLL2 無効) |

| ジッタ = 56fs RMS (12kHz ~ 20MHz) |

| DPLL モード (APLL2 無効) |

| ジッタ = 74fs RMS (12kHz ~ 20MHz) |

| DPLL モード (APLL2 無効) |

| ジッタ = 120fs RMS (12kHz ~ 20MHz) |

| カスケード接続 APLL2 による DPLL モード |

| fVCO2 = 5737.5MHz |

| 電源に注入される 25mVpp のノイズ (VDD = 3.3V、VDDO = 1.8V) |

| DJSPUR (ps pk-pk) = 2×10(dBc/20) / (π×fOUT) ×1E6。ここで、dBc は PSNR スプリアスレベル (dBc) 、fOUT は出力周波数 (MHz) です |

| ジッタ = 47fs RMS (12kHz ~ 20MHz) |

| DPLL モード (APLL2 無効) |

| ジッタ = 63fs RMS (12kHz ~ 20MHz) |

| DPLL モード (APLL2 無効) |

| ジッタ = 117fs RMS (12kHz ~ 20MHz) |

| カスケード接続 APLL2 による DPLL モード |

| fVCO2 = 5598.72MHz |

| 電源に注入される 50mVpp のノイズ (VDD = 3.3V、VDDO = 3.3V) |