JAJSR90A September 2023 – July 2024 LMQ64480-Q1 , LMQ644A0-Q1 , LMQ644A2-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Device Comparison Table

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Input Voltage Range (VIN)

- 7.3.2 Enable EN Pin and Use as VIN UVLO

- 7.3.3 Output Voltage Selection and Soft Start

- 7.3.4 SYNC Allows Clock Synchronization and Mode Selection

- 7.3.5 Clock Locking

- 7.3.6 Adjustable Switching Frequency

- 7.3.7 Power-Good Output Voltage Monitoring

- 7.3.8 Internal LDO, VCC UVLO, and BIAS Input

- 7.3.9 Bootstrap Voltage and VCBOOT-UVLO (CB1 and CB2 Pin)

- 7.3.10 CONFIG Device Configuration Pin

- 7.3.11 Spread Spectrum

- 7.3.12 Soft Start and Recovery From Dropout

- 7.3.13 Overcurrent and Short-Circuit Protection

- 7.3.14 Hiccup

- 7.3.15 Thermal Shutdown

- 7.4 Device Functional Modes

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Choosing the Switching Frequency

- 8.2.2.2 Setting the Output Voltage

- 8.2.2.3 Inductor Selection

- 8.2.2.4 Output Capacitor Selection

- 8.2.2.5 Input Capacitor Selection

- 8.2.2.6 BOOT Capacitor

- 8.2.2.7 VCC

- 8.2.2.8 CFF and RFF Selection

- 8.2.2.9 SYNCHRONIZATION AND MODE

- 8.2.2.10 External UVLO

- 8.2.2.11 Typical Thermal Performance

- 8.2.3 Application Curves

- 8.3 Power Supply Recommendations

- 8.4 Layout

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

3 概要

LMQ644xx-Q1 は、大電流の単一出力またはデュアル出力に対応する 36V 同期整流降圧 DC/DC コンバータです。このデバイスは、インターリーブされたスタック可能な電流モード制御アーキテクチャを使用しているので、ループ補償が簡単であり、過渡応答が高速で、優れた負荷およびライン レギュレーションが可能です。出力クロックによって正確な電流共有を行い、最大 36A の電流について最大 6 相をサポートできます。最小オン時間 50ns のハイサイド スイッチは、大きい降圧率に対応でき、12V、24V または 車載用入力から低電圧レールへの直接変換が可能になり、システムの複雑度と設計コストを下げることができます。

LMQ644xx-Q1 は、ウェッタブル フランク付きの最適化された拡張 HotRod QFN パッケージに拡散スペクトラムを搭載し、EMI を最小限に抑えるために 4 つの 22nF 高周波コンデンサを内蔵しています。デュアル ランダム拡散スペクトラム (DRSS) 周波数ホッピングは ±10% (標準値) に設定されており、三角波と疑似ランダム変調の組み合わせにより、放射を大幅に低減します。BIAS ピンを使用すると、LMQ644xx-Q1 はコンバータの出力からデバイスに電力を供給することで損失を節約でき、無負荷時の静止電流は 9μA となり、バッテリ駆動システムの動作時間を延長できます。LMQ644xx-Q1 は、複数のデバイスをスタックする場合でも、軽負荷動作時に高効率を維持し、負荷範囲全体にわたって高効率を実現できます。

| 部品番号 (2) | パッケージ (1) | 本体サイズ (公称) |

|---|---|---|

| LMQ644A2-Q1 | RXA (VQFN-FCRLF、24) | 4.0mm × 5.0mm |

| LMQ644A0-Q1 | ||

| LMQ64480-Q1 |

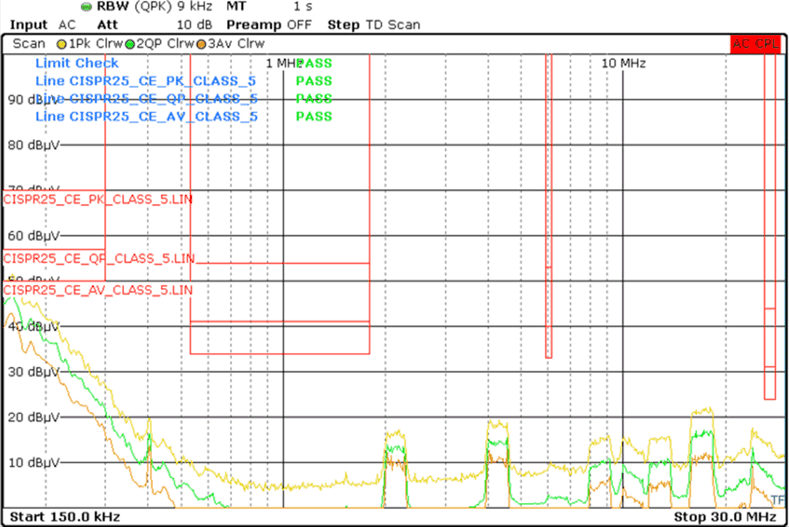

CISPR 25

伝導、VOUT = 3.3V、2.1MHz、12A

CISPR 25

伝導、VOUT = 3.3V、2.1MHz、12A