JAJSG01D June 2012 – August 2018 LMZ20502

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- SIL|8

サーマルパッド・メカニカル・データ

発注情報

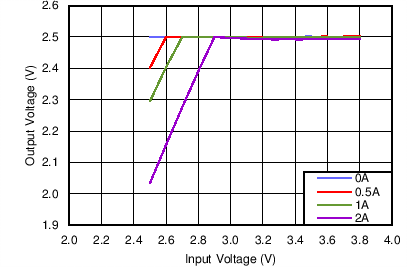

7.3.5 Dropout Behavior

When the input voltage is close to the output voltage the regulator will operate at very large duty cycles. Normal time delays of the internal circuits prevents the attainment of controlled duty cycles near 100%. In this condition the LMZ20502 will skip switching cycles in order to maintain regulation with the highest possible input-to-output ratio. Some increase in output voltage ripple may appear as the regulator skips cycles. As the input voltage gets closer to the output voltage, the regulator will eventually reach 100% duty cycle, with the high side switch turned on. The output will then follow the input voltage minus the drop across the high side switch and inductor resistance. Figure 11 and Figure 12 show typical drop-out behavior for output voltages of 2.5 V and 3.3 V.

Since the internal gate drive levels of the LMZ20502 are dependent on input voltage, the Rdson of the power FETs will increase at low input voltages. This will result in degraded efficiency at output currents of greater than 1 A and input voltages below about 2.9 V. Also, combinations of low input voltage and high output voltage increases the effective switch duty cycle which may result in increased output voltage ripple.

Figure 11. Typical Drop-Out Behavior, VOUT = 2.5 V

Figure 11. Typical Drop-Out Behavior, VOUT = 2.5 V  Figure 12. Typical Drop-Out Behavior, VOUT = 3.3 V

Figure 12. Typical Drop-Out Behavior, VOUT = 3.3 V