SLAS928B March 2013 – November 2016 LP3988-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device And Documentation Support

- 13Mechanical, Packaging, And Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DBV|5

サーマルパッド・メカニカル・データ

発注情報

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Voltage | −0.3 | 6.5 | V | |

| Power Good (OUT, EN) | −0.3 | See(3) | V | |

| Junction temperature, TJ | 150 | °C | ||

| Power dissipation(4) | 469 | mW | ||

| Storage temperature, Tstg | −65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pin.

(3) The lesser of VIN + 0.3 V or 6 V.

(4) The Absolute Maximum power dissipation depends on the ambient temperature and can be calculated using the formula: PD = (TJ – TA) / RθJA, where TJ is the junction temperature, TA is the ambient temperature, and R θJA is the junction-to-ambient thermal resistance. The 469-mW rating appearing under Absolute Maximum Ratings for the 5-pin SOT-23 package results from substituting the absolute-maximum junction temperature, 150°C, for TJ, 70°C for TA, and 170.5°C/W for RθJA. More power can be dissipated safely at ambient temperatures below 70°C . Less power can be dissipated safely at ambient temperatures above 70°C. The absolute-maximum power dissipation can be increased by 5.86 mW for each degree below 70°C, and it must be derated by 5.86 mW for each degree above 70°C.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±2000 | V |

| Charged-device model (CDM), per AEC Q100-011 | ±750 | |||

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| IN(2) | 2.5 | 6 | V | ||

| OUT, EN | 0 | VIN | V | ||

| Junction temperature, TJ | –40 | 125 | °C | ||

(1) All voltages are with respect to the potential at the GND pin.

(2) The minimum VIN is dependant on the device output option. For VOUT(NOM) < 2.5 V, VIN(MIN) equals 2.5 V. For VOUT(NOM) ≥ 2.5 V, VIN(MIN) equals VOUT(NOM) + 200 mV.

6.4 Thermal Information

| THERMAL METRIC(1) | LP3988-Q1 | UNIT | |

|---|---|---|---|

| DBV (SOT-23) | |||

| 5 PINS | |||

| RθJA(2) | Junction-to-ambient thermal resistance, High-K | 170.5 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 124.4 | °C/W |

| RθJB | Junction-to-board thermal resistance | 30.9 | °C/W |

| ψJT | Junction-to-top characterization parameter | 17.6 | °C/W |

| ψJB | Junction-to-board characterization parameter | 30.4 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics.

(2) Thermal resistance value RθJA is based on the EIA/JEDEC High-K printed circuit board defined by: JESD51-7 - High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages.

6.5 Electrical Characteristics

Unless otherwise specified: VEN = 1.8 V, VIN = VOUT + 0.5 V, CIN = 1 µF, IOUT = 1 mA, COUT = 1 µF; typical values and limits are for TJ = 25°C, and minimum and maximum values and limits apply over the entire junction temperature range for operation, −40°C to +125°C.(1)(2)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ΔVOUT | Output voltage tolerance | TJ = 25°C | −2 | 2 | % of VOUT(NOM) | |

| –3.5 | 3.5 | |||||

| Line regulation error | VIN = VOUT(NOM) + 0.5 V to 6 V TJ = 25°C |

−0.15 | 0.15 | %/V | ||

| VIN = VOUT(NOM) + 0.5 V to 6 V | –0.2 | 0.2 | ||||

| Load regulation error(3) | IOUT = 1 mA to 150 mA, TJ = 25°C | 0.005 | %/mA | |||

| IOUT = 1 mA to 150 mA | 0.007 | |||||

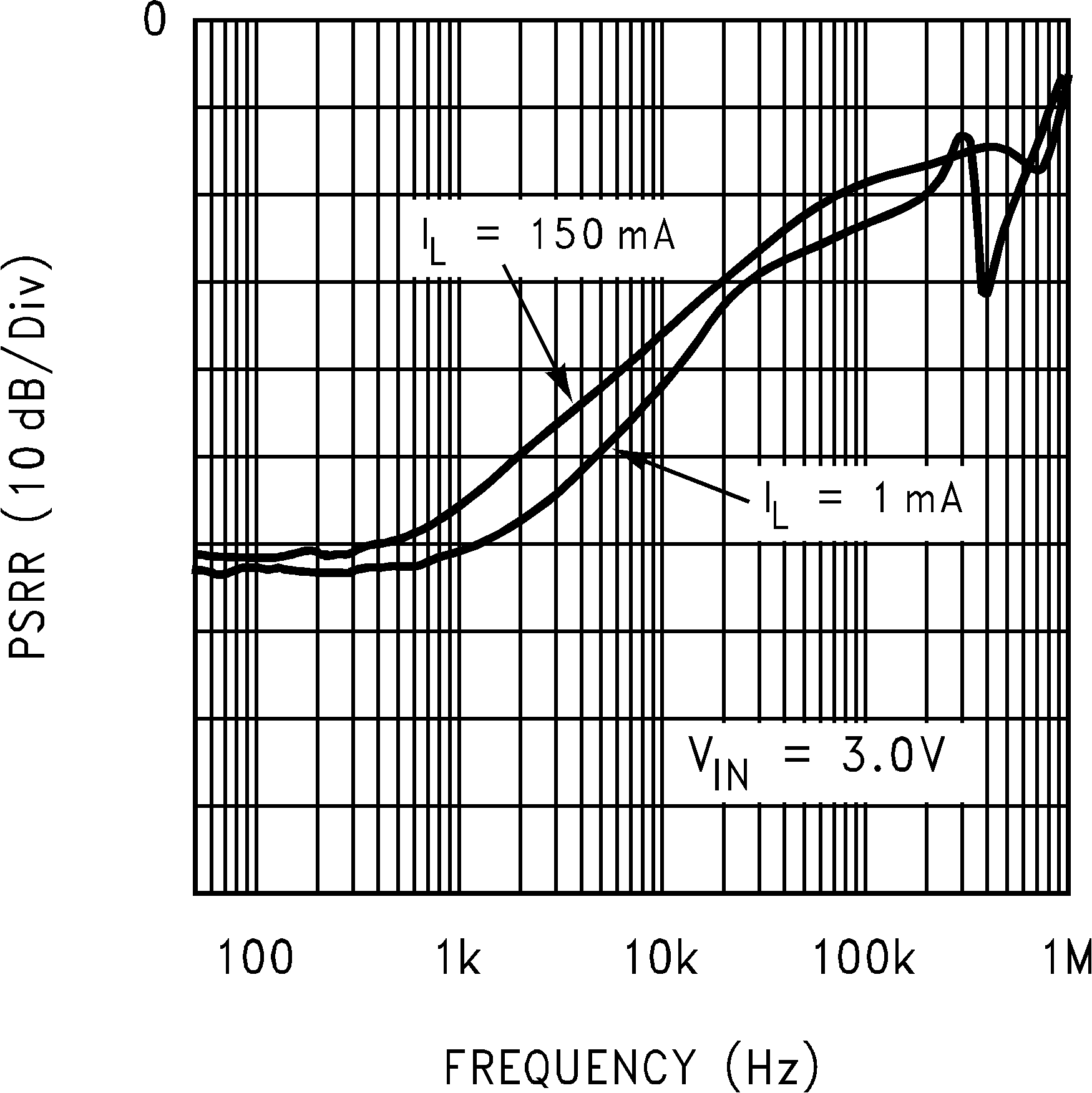

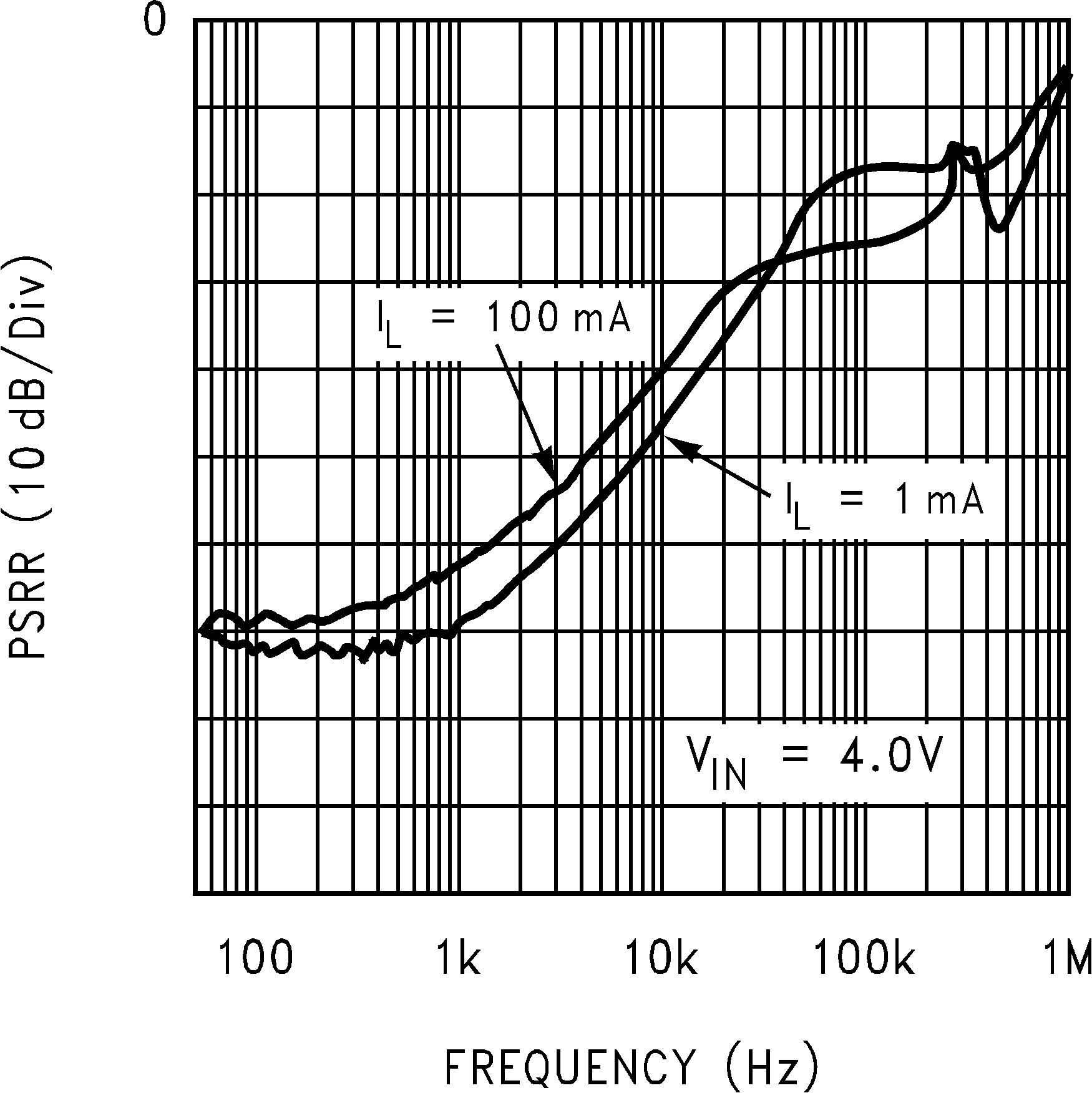

| PSRR | Power supply rejection ratio | VIN = VOUT(NOM) + 1 V, ƒ = 1 kHz, IOUT = 50 mA (See Figure 15) |

65 | dB | ||

| VIN = VOUT(nom) + 1 V, ƒ = 10 kHz, IOUT = 50 mA (See Figure 15) |

45 | |||||

| IQ | Quiescent current | VEN = 1.4 V, IOUT = 0 mA, TJ = 25°C | 85 | 120 | µA | |

| VEN = 1.4 V, IOUT = 0 to 150 mA | 140 | 200 | ||||

| VEN = 0.4 V | 0.003 | 1 | ||||

| VDO | Dropout voltage(4) | IOUT = 1 mA | 1 | 5 | mV | |

| IOUT = 150 mA, TJ = 25°C | 80 | 115 | ||||

| IOUT = 150 mA | 150 | |||||

| ISC | Short-circuit current limit | See(5) | 600 | mA | ||

| en | Output noise voltage | BW = 10 Hz to 100 kHz, COUT = 1 µF |

220 | µVRMS | ||

| COUT | Output capacitor | Capacitance(6) | 1 | 20 | µF | |

| ESR(6) | 5 | 500 | mΩ | |||

| TSD | Thermal shutdown temperature | 160 | °C | |||

| Thermal shutdown hysteresis | 20 | |||||

| ENABLE CONTROL CHARACTERISTICS | ||||||

| IEN | Maximum input current at EN | VEN = 0 V and VIN = 6 V | 0.1 | µA | ||

| VIL | Logic low input threshold | VIN = 2.5 V to 6 V | 0.5 | V | ||

| VIH | Logic high input threshold | VIN = 2.5 V to 6 V | 1.2 | V | ||

| POWER GOOD | ||||||

| VTHL | PG low threshold | % of VOUT (PG ON), TJ = 25°C(7) | 90% | 93% | 95% | |

| VTHH | PG high threshold | % of VOUT (PG OFF), TJ = 25°C(7) | 92% | 95% | 98% | |

| VOL | PG output logic low voltage | IPULLUP = 100 µA, fault condition | 0.02 | 0.1 | V | |

| IPGL | PG output leakage current | PG off, VPG = 6 V | 0.02 | µA | ||

(1) All electrical characteristics having room-temperature limits are tested during production with TJ = 25°C or correlated using statistical quality control (SQC) methods. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) The target output voltage, which is labeled VOUT(NOM), is the desired voltage option.

(3) An increase in the load current results in a slight decrease in the output voltage and vice versa.

(4) Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value.

(5) Short-circuit current is measured on input supply line after pulling down VOUT to 95% VOUT(NOM).

(6) Specified by design. Not production tested. The capacitor tolerance should be ±30% or better over the full temperature range. The full range of operating conditions such as temperature, DC bias and even capacitor case size for the capacitor in the application must be considered during device selection to ensure this minimum capacitance specification is met. TI recommends X7R capacitor types to meet the full device temperature range.

(7) The low and high thresholds are generated together. Typically a 2.6% difference is seen between these thresholds.

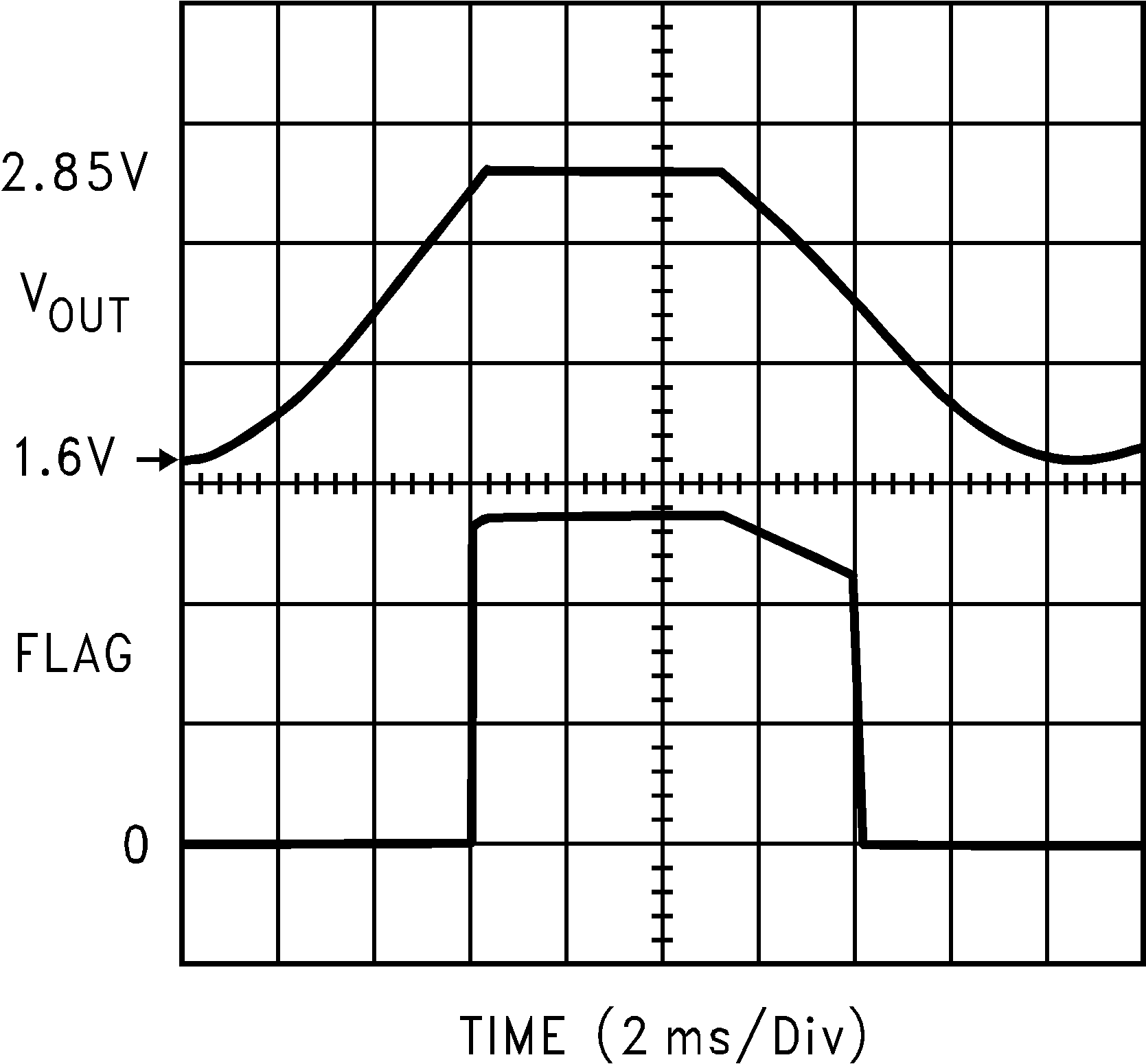

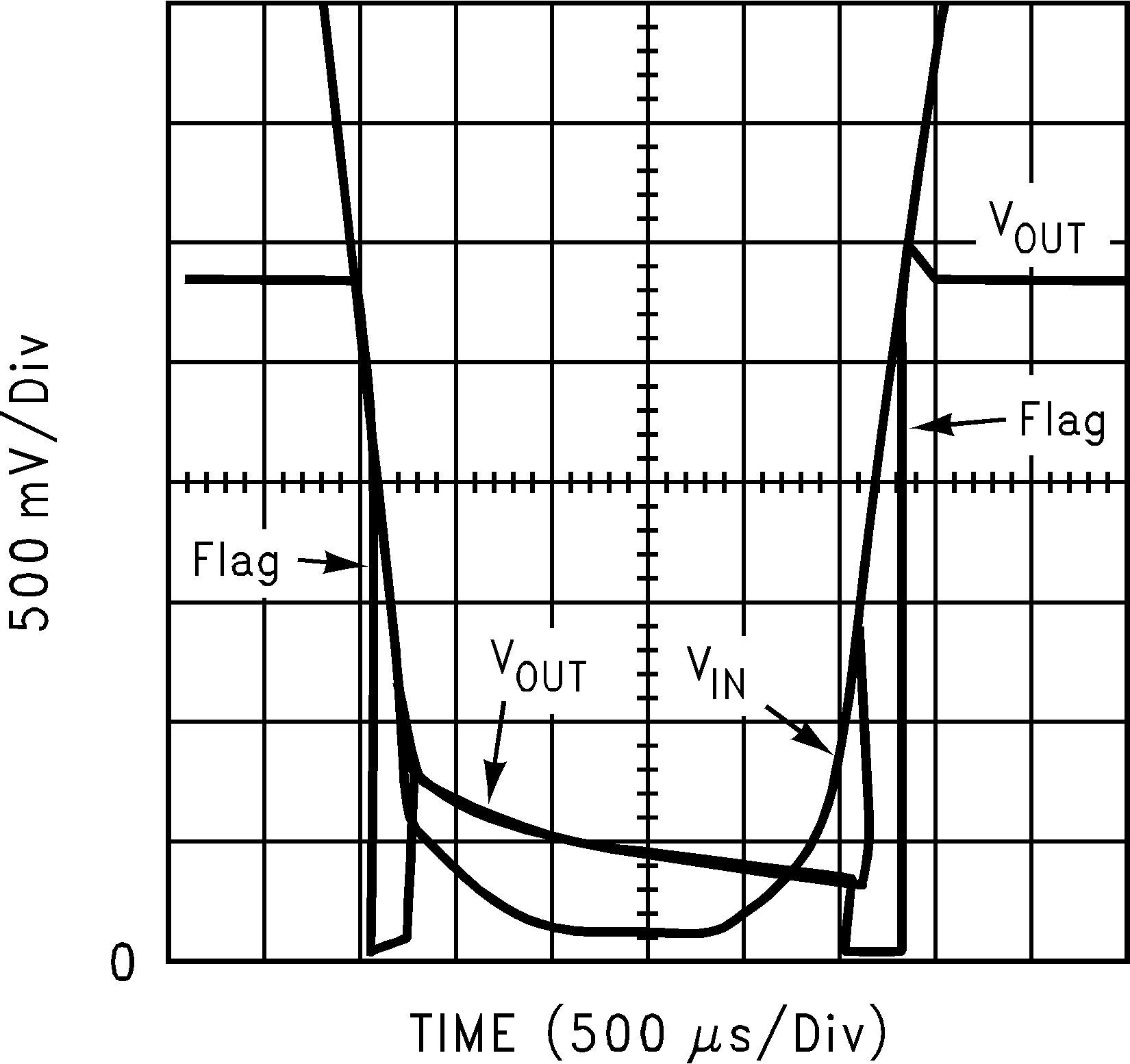

6.6 Timing Requirements

| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| TON | PG turnon time(1), VIN = 4.2 V | 10 | µs | ||

| TOFF | PG turnoff time(1), VIN = 4.2 V | 10 | µs | ||

6.7 Typical Characteristics

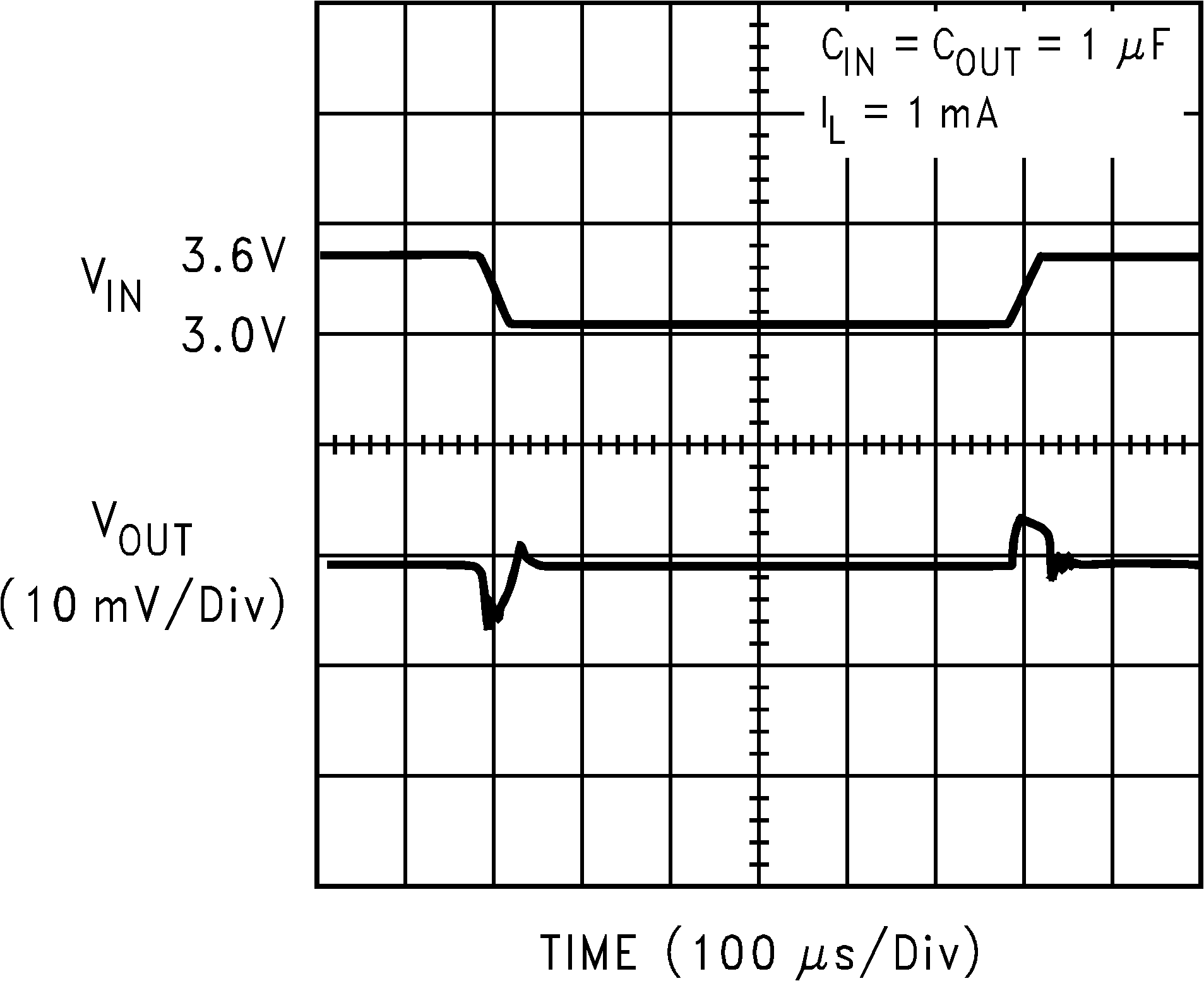

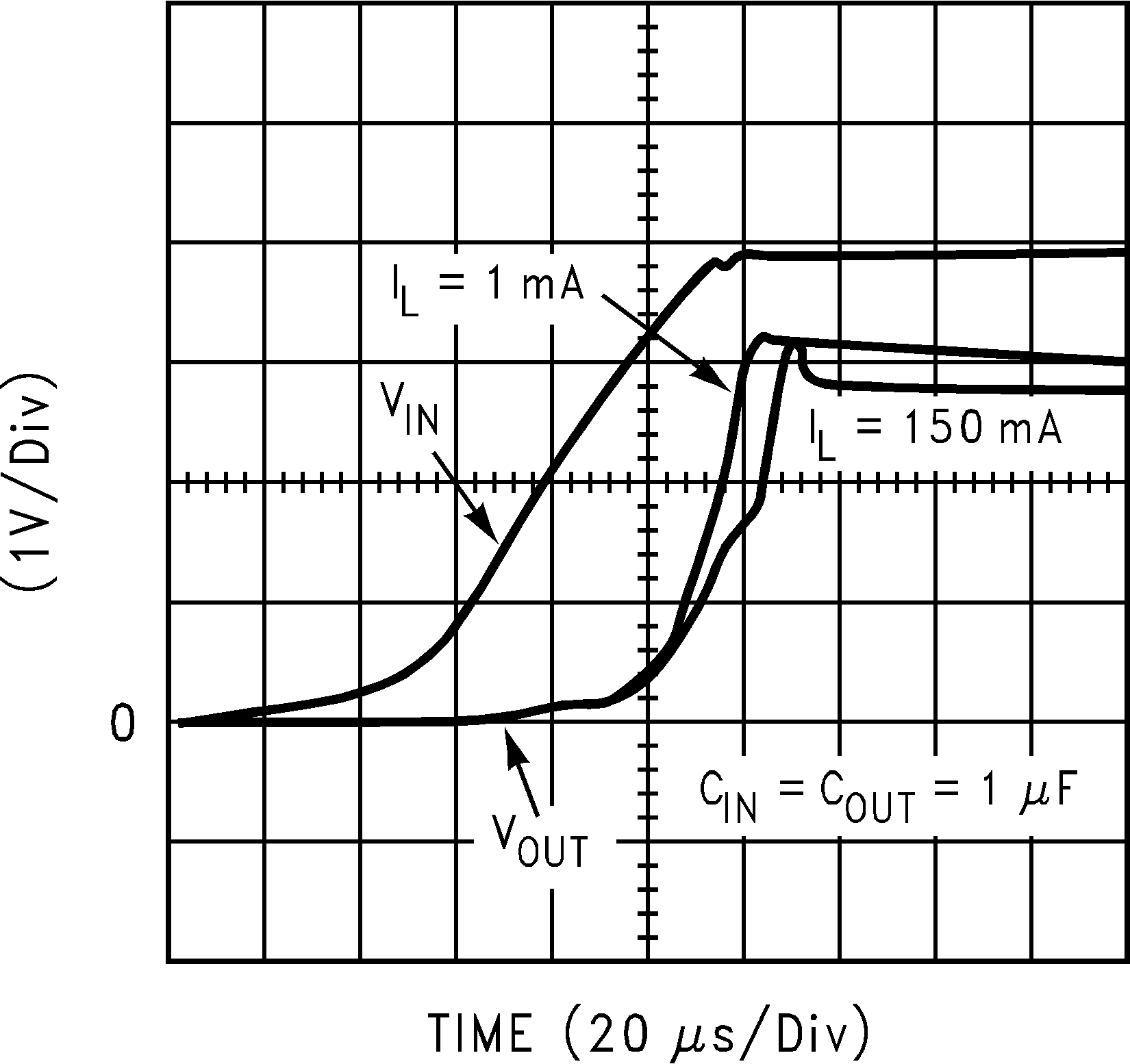

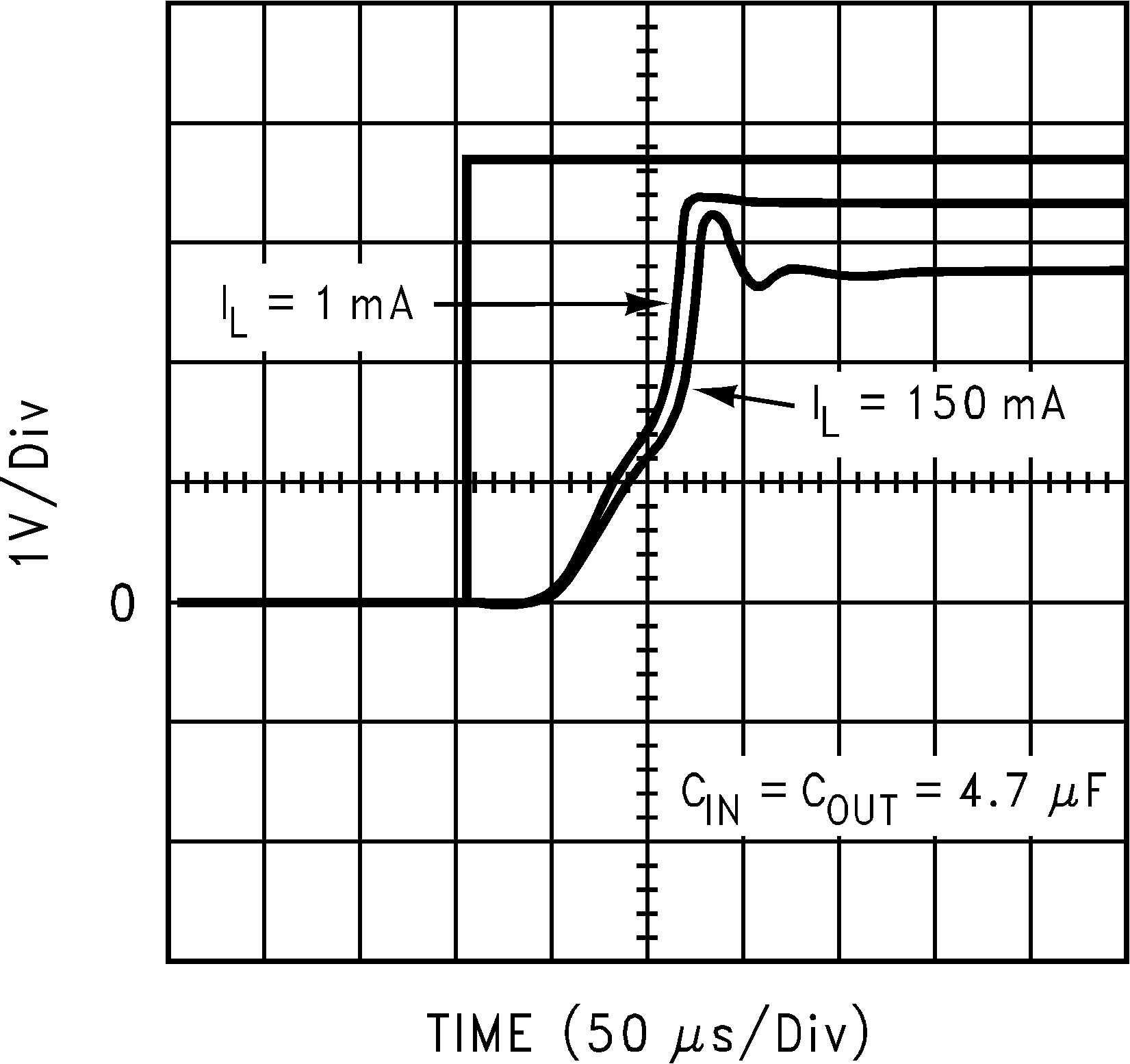

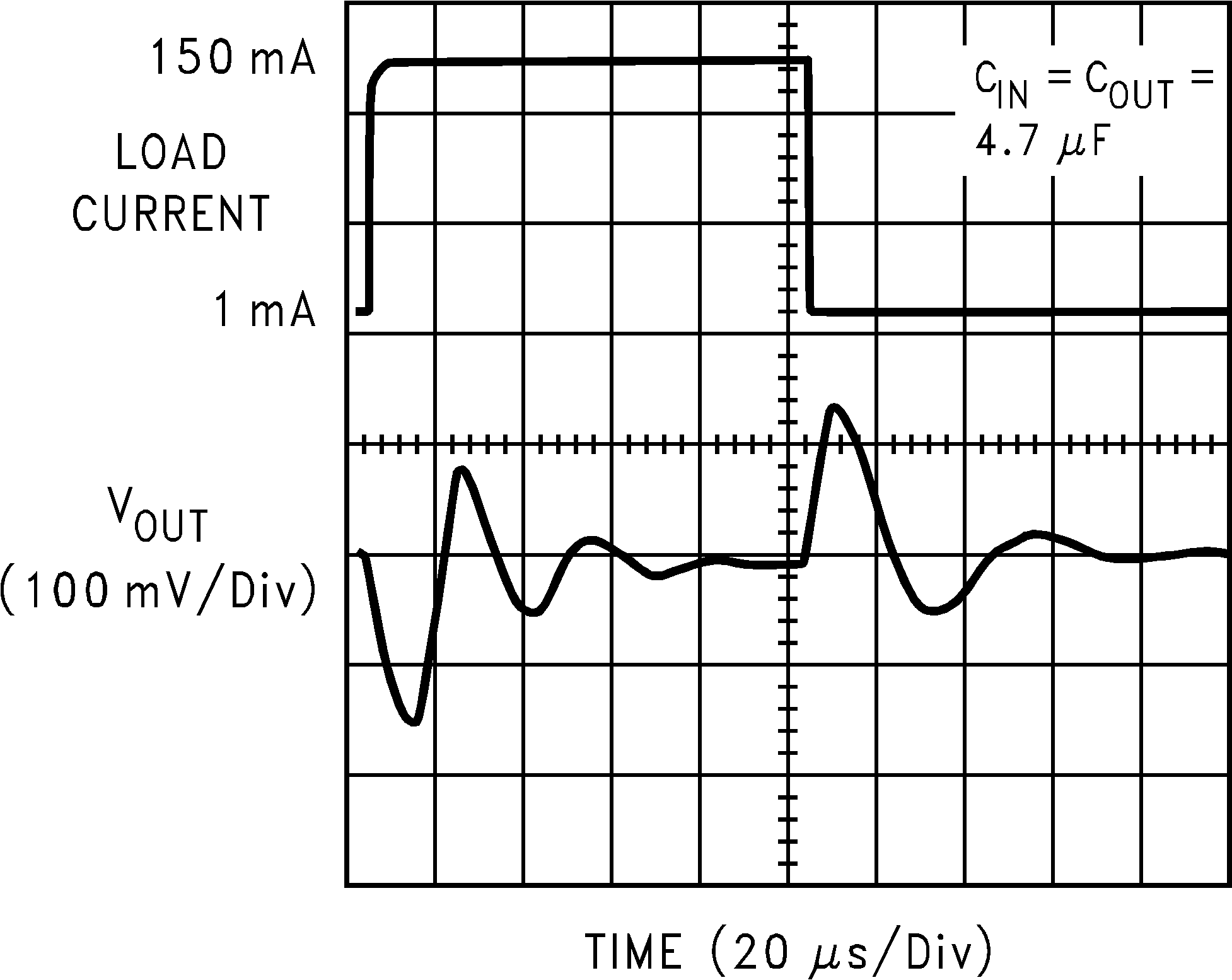

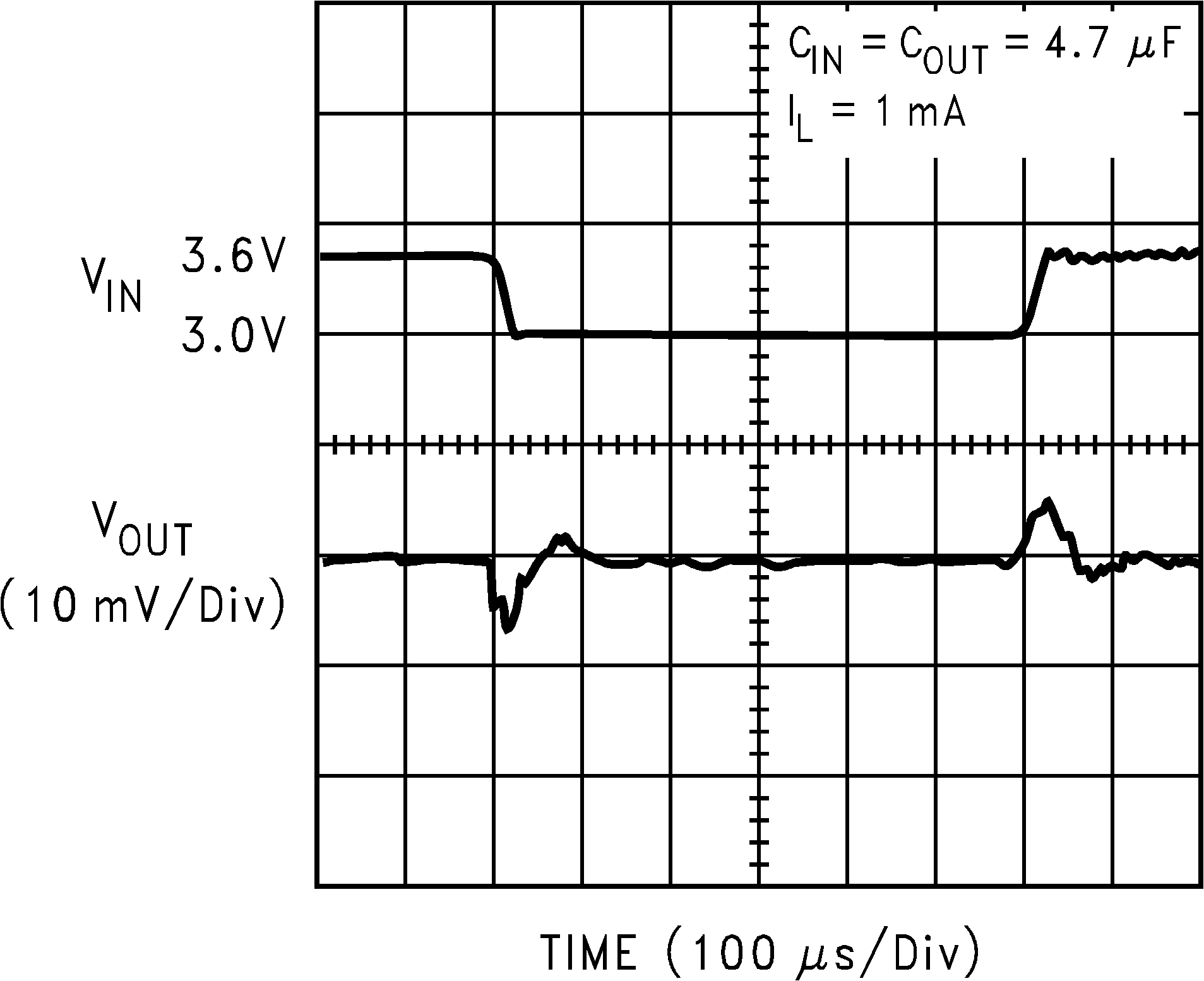

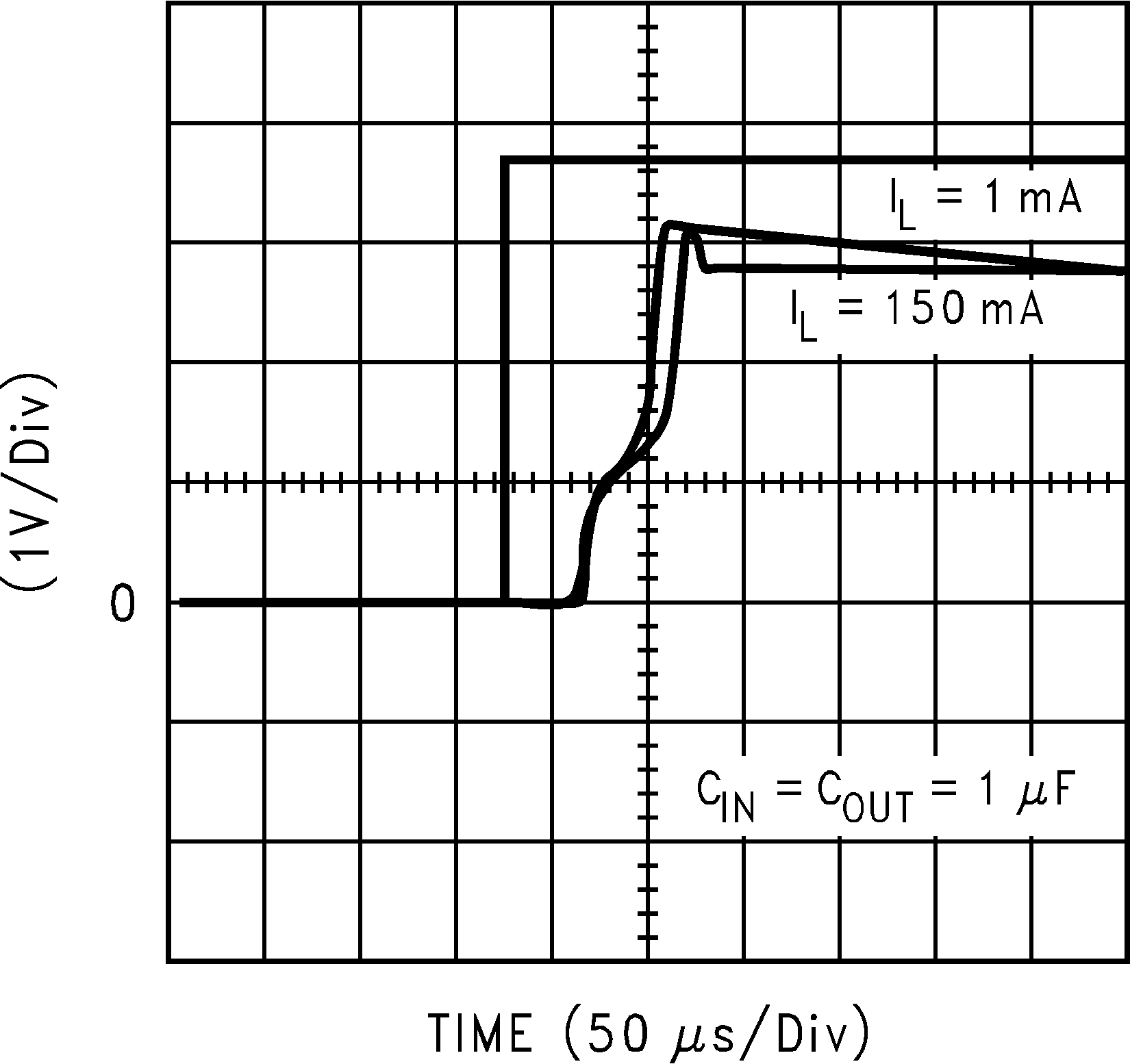

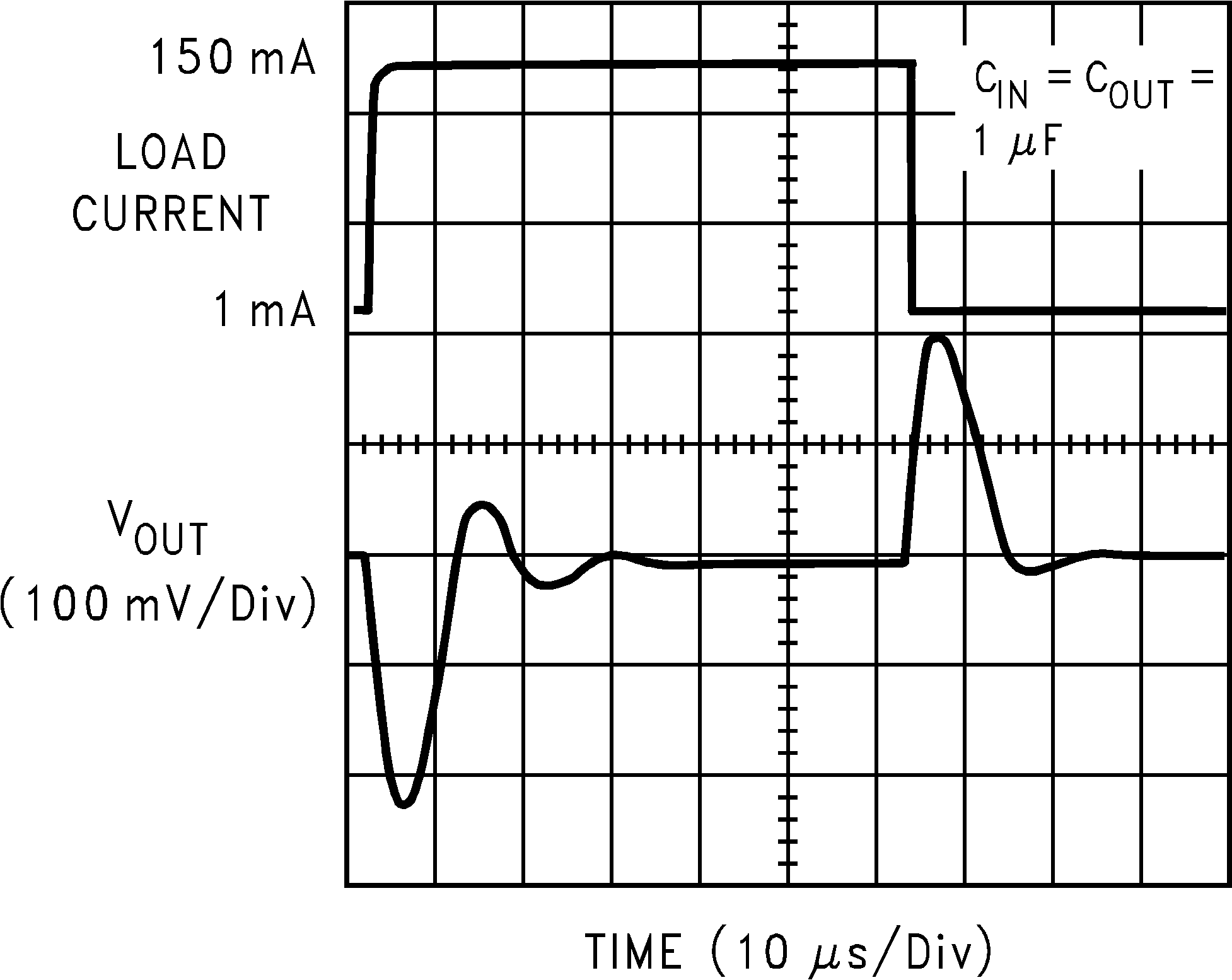

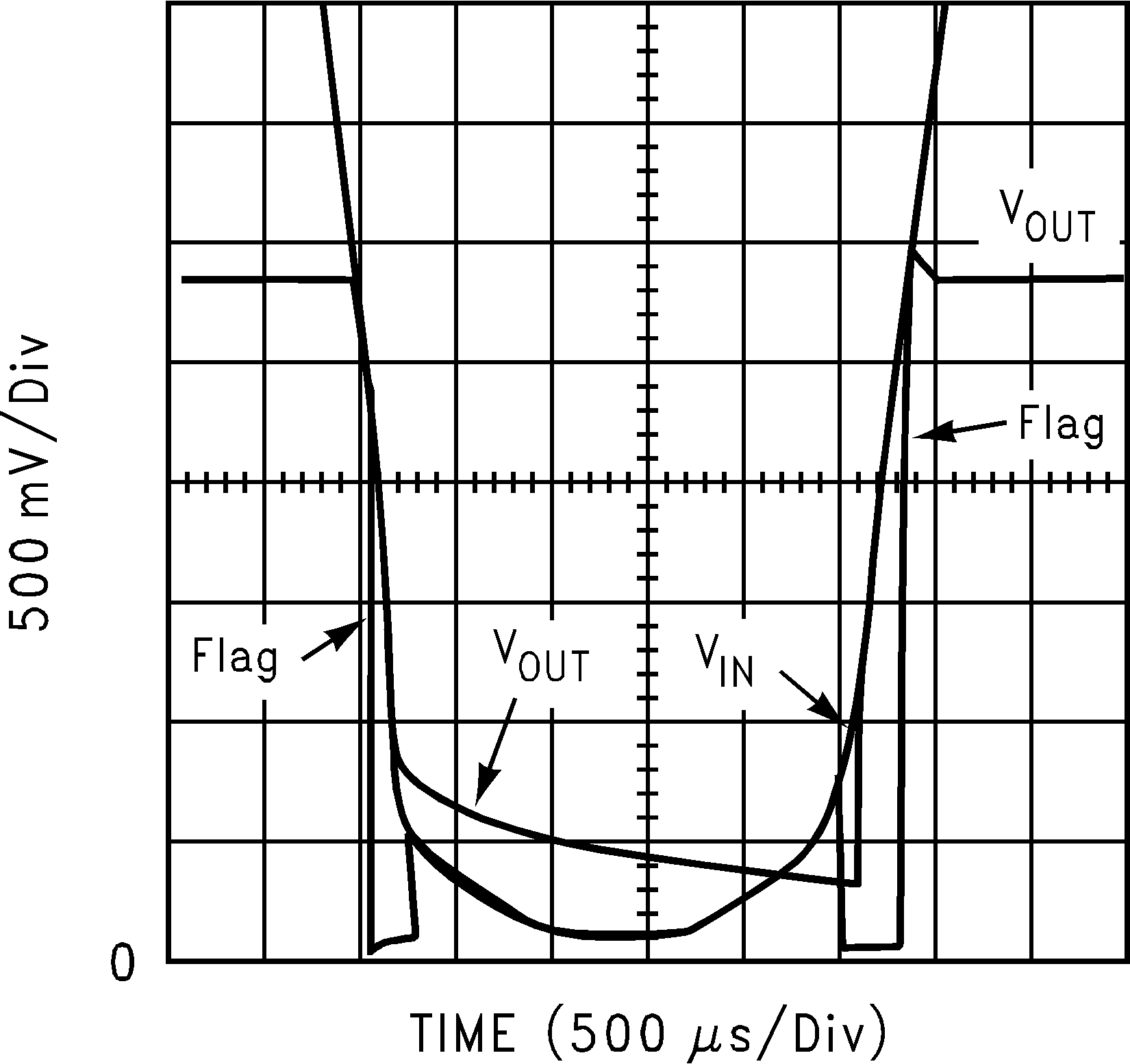

Unless otherwise specified, CIN = COUT = 1-µF ceramic, VIN = VOUT + 0.2 V, TA = 25°C, EN pin is tied to VIN.

| FLAG pin pulled to VOUT through a 100-kΩ resistor | ||

| FLAG pin pulled to VOUT through a 100-kΩ resistor | ||

| FLAG pin pulled to VIN through a 100-kΩ resistor | ||