SNVSA15B December 2013 – December 2015 LP8557

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Function and Configurations

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Boost Converter Electrical Characteristics

- 7.7 LED Driver Electrical Characteristics (LED1 To LED6 Pins)

- 7.8 PWM Interface Characteristics (PWM Pin)

- 7.9 Logic Interface Characteristics (PWM, FSET/SDA, ISET/SCL Pins)

- 7.10 I2C Serial Bus Timing Parameters (SDA, SCL)

- 7.11 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

8 Detailed Description

8.1 Overview

The LP8557 and LP8557I are high-efficiency LED drivers each featuring an integrated DC-DC inductive boost converter and six high-precision current sinks. LP8557 is intended for applications that exclusively use a pulse width modulated (PWM) signal for controlling the brightness while LP8557I is intended for applications that can utilize an I2C master as well.

The boost converter has adaptive output voltage control. This feature minimizes the power consumption by adjusting the voltage to the lowest sufficient level under all conditions.

The adaptive current sink headroom voltage control scales the headroom voltage with the LED current for optimal system efficiency.

The LED string auto-detect function enables use of the same device in systems with 1 to 6 LED strings for the maximum design flexibility.

Proprietary hybrid PWM plus current mode dimming enables additional system power savings. Phase shift PWM allows reduced audible noise and smaller boost output capacitors.

Flexible CABC support combines brightness level selections based on the PWM input and I2C commands.

The LP8557 and LP8557I feature a full set of features that ensure robust operation of the device and external components. The set consists of input undervoltage lockout, thermal shutdown, overcurrent protection, overvoltage protection, and LED open and short detection.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Boost Converter Overview

8.3.1.1 Operation

The boost DC-DC converter generates a 7-V to 28-V boost output voltage from a 2.7-V to 5.5-V boost input voltage.

The converter is a magnetic switching PWM mode DC-DC inductive boost converter with a current limit. It uses current programmed mode control, where the inductor current is measured and controlled with the feedback. During start-up, the soft-start function reduces the peak inductor current. Figure 20 shows the boost block diagram.

Figure 20. Boost Circuit Block Diagram

Figure 20. Boost Circuit Block Diagram

8.3.1.2 Adaptive Boost Output Voltage Control

The boost converter operates in adaptive boost control mode. In this mode, the voltage at the LED pins is monitored by the control loop. It raises the boost voltage when the measured voltage of ANY of the LED strings falls below the voltage threshold of its corresponding LOW comparator. If the headrooms of ALL of the LED strings are above the voltage threshold of their corresponding MID comparator, then the boost voltage is lowered.

Figure 21. Adaptive Headroom Detail

Figure 21. Adaptive Headroom Detail

8.3.2 Brightness Control

The brightness can be controlled using an external PWM signal or the Brightness registers accessible via an I2C interface or both. Which of these two input sources is selected is set by the BRTMODE bits. The LP8557 operates exclusively in BRTMODE = 00. While the LP8557I, by default, operates in BRTMODE = 11, it can operate in all BRTMODE settings by configuring the bits via the I2C interface. How the brightness is controlled in each of the four possible modes is described in the following sections.

8.3.2.1 PWM Input Duty Measurement

When using PWM input for brightness control the input PWM duty cycle is measured as described in following diagram and the brightness is controlled based on the result. When changing the brightness it must be noted that the measurement cycle is from rising edge to next rising edge and brightness change must be done accordingly (time from rising to rising edge is constant (=cycle time) and falling edge defines the brightness).

Figure 22. PWM Input Duty Cycle Measurement

Figure 22. PWM Input Duty Cycle Measurement

8.3.2.2 BRTMODE = 00b

With BRTMODE = 00b, the LED output current is controlled by the PWM input duty cycle. The PWM detector block measures the duty cycle at the PWM pin and uses it to generate a PWM-based brightness code. Before the output is generated, the code goes through the curve shaper block. Then the code goes into the hybrid PWM & I Dimming block which determines the range of the PWM and Current control. The outcome of the hybrid PWM & I dimming block is current and/or up to 6 PWM output signals.

Figure 23. Brightness Data Path for BRTMODE = 00b

Figure 23. Brightness Data Path for BRTMODE = 00b

Figure 24. Typical Application Circuit for Devices Configured With BRTMODE = 00

Figure 24. Typical Application Circuit for Devices Configured With BRTMODE = 00

8.3.2.3 BRTMODE = 01b

With BRTMODE = 01b, the LED output current is controlled by the BRTHI/BRTLO registers. Before the output is generated the BRTHI/BRTLO registers-based brightness code goes through the Curve Shaper block. Then the code goes into the hybrid PWM & I dimming block which determines the range of the PWM and current control. The outcome of the Hybrid PWM&I Dimming block is Current and/or up to 6 PWM output signals.

Figure 25. Brightness Data Path for BRTMODE = 01b

Figure 25. Brightness Data Path for BRTMODE = 01b

8.3.2.4 BRTMODE = 10b

With BRTMODE = 10b, the LED output current is controlled by the PWM input duty cycle and the BRTHI/BRTLO registers. The PWM detector block measures the duty cycle at the PWM pin and uses it to generate PWM-based brightness code. Before the code is multiplied with the BRTHI/BRTLO registers-based brightness code, it goes through the curve shaper block. After the multiplication, the resulting code goes into the hybrid PWM & I dimming block which determines the range of the PWM and Current control. The outcome of the hybrid PWM & I dimming block is current or up to 6 PWM output signals.

Figure 26. Brightness Data Path for BRTMODE = 10b

Figure 26. Brightness Data Path for BRTMODE = 10b

8.3.2.5 BRTMODE = 11b

With BRTMODE = 11b, the LED output current is controlled by the PWM input duty cycle and the BRTHI/BRTLO registers. The PWM detector block measures the duty cycle at the PWM pin and uses it to generate PWM-based brightness code. In this mode, the BRTHI/BRTLO registers-based brightness code goes through the curve shaper block before it is multiplied with the PWM input duty cycle-based brightness code. After the multiplication, the resulting code goes into the hybrid PWM & I dimming block which determines the range of the PWM and Current control. The outcome of the hybrid PWM & I dimming block is current and/or up to 6 PWM output signals.

Figure 27. Brightness Data Path for BRTMODE = 11b

Figure 27. Brightness Data Path for BRTMODE = 11b

Figure 28. Typical Application Circuit for Devices Configured With BRTMODE = 01, 10, or 11

Figure 28. Typical Application Circuit for Devices Configured With BRTMODE = 01, 10, or 11

8.3.2.6 Hybrid PWM & I Dimming Control

Hybrid PWM & I dimming control combines PWM dimming and LED current-dimming control methods. With this dimming control, better optical efficiency is possible from the LEDs compared to pure PWM control while still achieving smooth and accurate control and low brightness levels. The switch point from current-to-PWM control can be set to get the optimal compromise between good matching of the LEDs brightness/white point at low brightness and good optical efficiency.

Figure 29. Dimming Methods

Figure 29. Dimming Methods

8.3.2.7 Phase Shift PWM Scheme

The phase shift PWM (PSPWM) scheme allows delay of the time when each LED current sink is active. When the LED current sinks are not activated simultaneously, the peak load current from the boost output is greatly decreased. This reduces the ripple seen on the boost output and allows smaller output capacitors to be used. Reduced ripple also reduces the output ceramic capacitor audible ringing. The PSPWM scheme also increases the load frequency seen on the boost output by up to six times, therefore transferring the possible audible noise to the frequencies outside the audible range.

The phase difference between each active driver is automatically determined as 360°/number of active drivers.

Figure 30. Phase Shift PWM Dimming Scheme Diagram

Figure 30. Phase Shift PWM Dimming Scheme Diagram

8.3.3 Slope and Advanced Slope

The transition time between two brightness values can be programmed with the STEP bits from 0 to 200 ms. The same slope time is used for sloping up and down. With advanced slope the brightness changes can be made more pleasing to a human eye. It is implemented with a digital smoothing filter. The filter strength is set with SMOOTH bits.

Figure 31. Slope and Advanced Slope

Figure 31. Slope and Advanced Slope

8.3.4 LED String Count Auto Detection

The LP8557 and LP8557I can auto-detect the number of the LED strings attached. During the auto-detect routine, the devices automatically remove the unused current sink(s) and adjust the phasing of the remaining current sinks. The LED OPEN* fault condition is not supported with auto-detect function enabled. On the LP8557I, the user may disable the function by setting CONFIG.AUTO bit to 0 via an I2C write.

8.3.5 EMI Reduction Schemes

LP8557I features two EMI reduction schemes. By default, the schemes are disabled; however, the schemes can be enabled by I2C writes to SSEN and SREN bits in COMMAND register. The schemes are unavailable on the LP8557.

The first scheme, programmable slew rate control, uses a combination of three drivers for boost switch. Enabling all three drivers allows boost switch on/off transition times to be the shortest. On the other hand, enabling just one driver allows boost switch on/off transition times to be the longest. The longer the transition times, the lower the switching noise on the SW terminal. It should also be noted that the shortest transition times bring the best efficiency as the switching losses are the lowest. This scheme can be enabled by setting SREN=1 with an I2C write.

The second EMI reduction scheme is the spread spectrum scheme. This scheme deliberately spreads the frequency content of the boost switching waveform, which inherently has a narrow bandwidth, makes the switching waveform's bandwidth wider and ultimately reduces its EMI spectral density. This scheme can be enabled by setting SSEN = 1 with an I2C write.

Figure 32. EMI Reduction Schemes

Figure 32. EMI Reduction Schemes

8.3.6 Fault Detection

The LP8557 and LP8557I have fault detection for LED SHORT, UVLO, BST_OVP, BST_OCP, BST_UV, and TSD. Additionally, the LP8557I can support LED OPEN* fault. Faults are recorded in the STATUS register. Each time the STATUS register is read it is automatically cleared.

8.3.6.1 LED Short Detection

Voltages at the individual current sinks are constantly monitored for the LED SHORT fault. This fault may occur when some LEDs in a string are electrically bypassed making that LED string shorter than the other LED strings. The reduced forward voltage causes the current sink attached to that string to have a higher headroom voltage than the other current sinks. When the headroom voltage is higher than the fault comparator threshold (configured with the 0V field in the LEDEN register), that current sink is disabled, and the PWM phasing is automatically adjusted. The fault comparator threshold is at 2 V, typical.

8.3.6.2 LED OPEN* Detection

When the auto-detect function is disabled, each current sink is also monitored for the LED OPEN* condition. The condition is set when the headroom voltage on one or more current sinks is below the LOW comparator threshold, and the boost voltage is at the maximum. This fault condition may be caused by one or more OPEN LED strings or by one or more current sinks shorted to GND. The LP8557I immediately shuts down the backlight whenever an LED OPEN* condition is detected on any enabled LED drivers. The backlight does not turn on again (regardless of the COMMAND.ON bit) until the STATUS register is read.

8.3.6.3 Undervoltage Detection

The device continuously monitors the voltage on the VDD pin. When the VDD voltage drops below 2.5 V the backlight is immediately shut down, and the UVLO bit is set in the STATUS register. The backlight automatically starts again when the voltage has increased above 2.5 V + 50 mV hysteresis. Hysteresis is implemented to avoid continuously triggering undervoltage.

8.3.6.4 Thermal Shutdown

If the internal temperature reaches 150°C, the deviceimmediately shuts down the backlight to protect it from damage. The TSD bit is also set in the STATUS register. The device re-activates the backlight again when the internal temperature drops below 130°C.

8.3.6.5 Boost Overcurrent Protection

The device automatically limits boost current to 2.4 A . When the 2.4-A limit is reached the BST_OCP bit is set in the STATUS register. It is normal for the device to trigger the boost current limit during the start-up or sudden brightness changes. The STATUS register can be cleared by reading the bit. If the bit is permanently set, it may indicate an issue in the application.

8.3.6.6 Boost Overvoltage Protection

The device automatically limits boost voltage to VBOOST_MAX + 1.6 V. When the limit is reached the BST_OVP bit is set in the STATUS register. It is normal for the device to trigger the boost OVP limit during the start-up or sudden brightness changes. The status register can be cleared by reading the bit. If the bit is permanently set, it may indicate an issue in the application.

8.3.6.7 Boost Undervoltage Protection

The device can detect when the boost voltage is below VBOOST – 2.5 V for longer than 6 ms. When the threshold is reached the BST_UV bit is set in the STATUS register.

8.4 Device Functional Modes

8.4.1 Shutdown Mode

The device is in shutdown mode when the VDD pin is low. Current consumption in this mode from VDD pin is

< 1 µA.

8.4.2 Active Mode

In active mode the backlight is enabled either with setting the ON register bit high (LP8557I) or by activating PWM input (LP8557). The power supplying the VDD pin must be present. Brightness is controlled with I2C writes to brightness registers or by changing PWM input duty cycle (operation without I2C control). Configuration registers are not accessible in Active mode to prevent damage to the device by accidental writes. Current consumption from VDD terminal in this mode is typically 2.2 mA when LEDs are not drawing any current.

8.5 Programming

8.5.1 I2C-Compatible Serial Bus Interface

8.5.1.1 Interface Bus Overview

The I2C-compatible synchronous serial interface provides access to the programmable functions and registers on the device. This protocol uses a two-wire interface for bi-directional communications between the devices connected to the bus. The two interface lines are the serial data line (SDA), and the serial clock line (SCL). These lines must be connected to a positive supply, via a pull-up resistor and remain HIGH even when the bus is idle.

The default 7-bit I2C address for the LP8557I slave is 2Ch.

8.5.1.2 Start and Stop Conditions

START and STOP conditions classify the beginning and the end of the I2C session (see Figure 33). A START condition is defined as SDA transitioning from HIGH to LOW while SCL is HIGH. A STOP condition is defined as SDA transitioning from LOW to HIGH while SCL is HIGH. The I2C master always generates START and STOP conditions. The I2C bus is considered busy after a START condition and free after a STOP condition. During data transmission the I2C master can generate repeated START conditions. A START and a repeated START condition are equivalent function-wise. The data on SDA must be stable during the HIGH period of the clock signal (SCL). In other words, the state of SDA can only be changed when SCL is LOW.

Figure 33. Start And Stop Conditions

Figure 33. Start And Stop Conditions

After the START condition, the I2C master sends the 7-bit address followed by an eighth read or write bit (R/W). R/W = 0 indicates a WRITE, and R/W = 1 indicates a READ. The second byte following the chip address selects the register address to which the data is written. The third byte contains the data for the selected register.

8.5.1.3 Data Transactions

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock’s high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol permits a single data line to transfer both command/control information and data using the synchronous serial clock.

Figure 34. Bit Transfer

Figure 34. Bit Transfer

Each data transaction is composed of a START Condition, a number of byte transfers (set by the software) and a STOP Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow. The following sections provide further details of this process.

8.5.1.4 Acknowledge Cycle

The Acknowledge Cycle consists of two signals: the acknowledge clock pulse the master sends with each byte transferred, and the acknowledge signal sent by the receiving device.

The master generates the acknowledge clock pulse on the ninth clock pulse of the byte transfer. The transmitter releases the SDA line (permits it to go high) to allow the receiver to send the acknowledge signal. The receiver must pull down the SDA line during the acknowledge clock pulse and ensure that SDA remains low during the high period of the clock pulse, thus signaling the correct reception of the last data byte and its readiness to receive the next byte.

Figure 35. Bus Acknowledge Cycle

Figure 35. Bus Acknowledge Cycle

8.5.1.5 Acknowledge After Every Byte Rule

The master generates an acknowledge clock pulse after each byte transfer. The receiver sends an acknowledge signal after every byte received.

There is one exception to the acknowledge after every byte rule. When the master is the receiver, it must indicate to the transmitter an end of data by not-acknowledging (negative acknowledge) the last byte clocked out of the slave. This negative acknowledge still includes the acknowledge clock pulse (generated by the master), but the SDA line is not pulled down.

8.5.1.6 Control Register Write Cycle

- Master device generates start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master sends data byte to be written to the addressed register.

- Slave sends acknowledge signal.

- If master sends further data bytes the control register address is incremented by one after acknowledge signal.

- Write cycle ends when the master creates stop condition.

8.5.1.7 Control Register Read Cycle

- Master device generates a start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master device generates repeated start condition.

- Master sends the slave address (7 bits) and the data direction bit (r/w = 1).

- Slave sends acknowledge signal if the slave address is correct.

- Slave sends data byte from addressed register.

- If the master device sends acknowledge signal, the control register address is incremented by one. Slave device sends data byte from addressed register.

- Read cycle ends when the master does not generate acknowledge signal after data byte and generates stop condition.

Table 1. Data Read and Write Cycles

| ADDRESS MODE | |

|---|---|

| Data Read | <Start Condition> |

| <Slave Address><r/w = ‘0’>[Ack] | |

| <Register Addr.>[Ack] | |

| <Repeated Start Condition> | |

| <Slave Address><r/w = ‘1’>[Ack] | |

| [Register Data]<Ack or Nack> | |

| … additional reads from subsequent | |

| register address possible | |

| <Stop Condition> | |

| Data Write | <Start Condition> |

| <Slave Address><r/w=’0’>[Ack] | |

| <Register Addr.>[Ack] | |

| <Register Data>[Ack] | |

| … additional writes to subsequent | |

| register address possible | |

| <Stop Condition> |

<> Data from master; [] Data from slave

8.5.1.8 Register Read and Write Detail

Figure 36. Register Write Format

Figure 36. Register Write Format

Figure 37. Register Read Format

Figure 37. Register Read Format

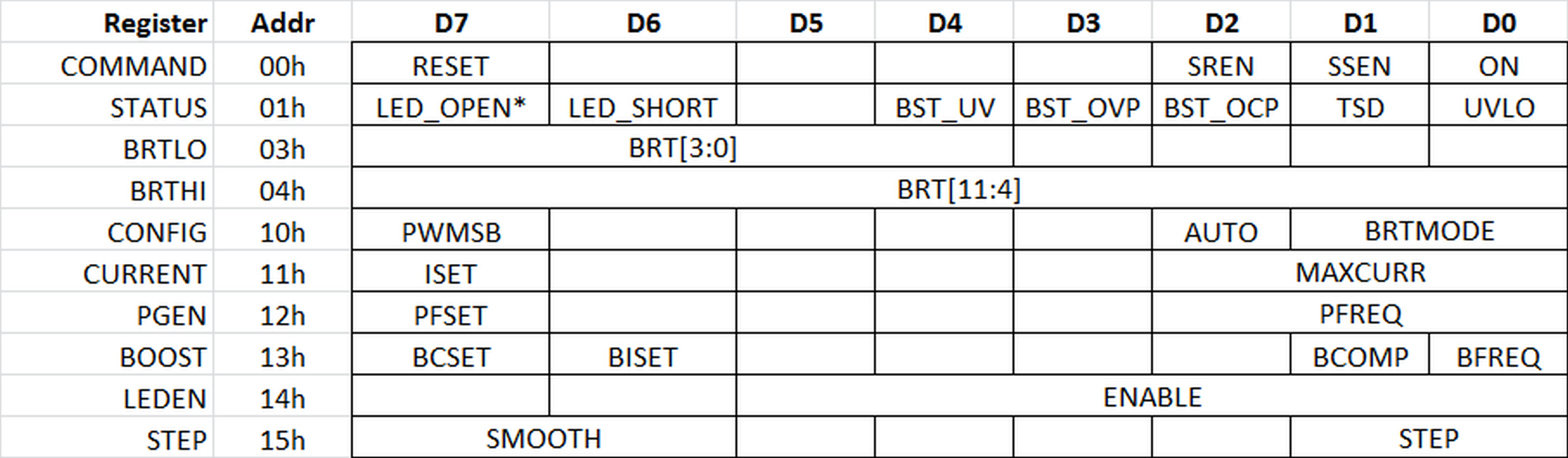

8.6 Register Maps

The register map is useful for LP8557I users intending to re-configure the register reset values. If re-configuration is necessary, it has to be done every time the power on VDD pin is recycled.

There is a restriction on register writes. The COMMAND, BRTLO, and BRTHI registers can be written at any time; however, the remaining registers only accept writes when the COMMAND.ON bit is low. All registers can be read at any time.

Many registers contain empty bit locations. These blank areas are reserved for future use. When writing to a register any empty fields must not be modified; when reading a register, these empty fields should be ignored.

8.6.1 Register Bit Descriptions

8.6.1.1 COMMAND

Address: 0x00h

Reset: 0x00h (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| RESET | — | SREN | SSEN | ON | |||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7 | RESET | R/W | 0b | Write 1 to reset the device. This bit is self-clearing and is always 0 when read. |

| 6:3 | reserved | R/O | 0000b | |

| 2 | SREN | R/W | 0b | Enable the boost slew rate control. 0 = Slew-rate control off (Default) 1 = Slew-rate control on |

| 1 | SSEN | R/W | 0b | Enable the spread-spectrum boost clocking. 0 = Spread-spectrum off (Default) 1 = Spread-spectrum on |

| 0 | ON | R/W | See Description | Turn on the backlight. 0 = backlight off (Default) 1 = backlight on |

The COMMAND.ON bit is used to turn on the backlight.

The COMMAND.SSEN and COMMAND.SREN bits may be updated at any time. It is not necessary for the backlight to be off when changing COMMAND.SSEN or COMMAND.SREN.

8.6.1.2 STATUS

Address: 0x01h

Reset: 0x00h

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| LED_OPEN* | LED_SHORT | – | BST_UV | BST_OVP | BST_OCP | TSD | UVLO |

| Bits | Field | Type | Default | Description |

| 7 | LED_OPEN* | R/O | 0b | An LED_OPEN* condition was detected on one or more strings. The condition is set when the headroom voltage on one or more current sinks is below the LOW comparator threshold, and the boost voltage is at the maximum. This fault condition may be caused by one or more OPEN LED strings or by one or more current sinks shorted to GND. Once set this bit stays set until the STATUS register is read. An LED_OPEN* condition turns off the backlight when CONFIG.AUTO is 0. When CONFIG.AUTO is 1, the condition is never set. |

| 6 | LED_SHORT | R/O | 0b | An LED SHORT condition was detected on one or more strings. The condition is set when the headroom voltage on one or more current sinks is above the FAULT comparator threshold and at least one driver has the headroom voltage in regulation (between LOW and MID comparator thresholds). This fault condition may be caused by one or more shorted LEDs on one or more (but not all) strings. Once set this bit stays set until the STATUS register is read. |

| 5 | reserved | R/O | 0b | |

| 4 | BST_UV | R/O | 0b | A boost output undervoltage condition was detected. The boost voltage is 2.5 V (typical) or more below the target. Once set this bit stays set until the STATUS register is read. |

| 3 | BST_OVP | R/O | 0b | A boost overvoltage protection condition was detected. The boost voltage is 1.6 V (typical) above the VMAX value. Once set this bit stays set until the STATUS register is read. |

| 2 | BST_OCP | R/O | 0b | A boost overcurrent protection condition was detected. Once set this bit stays set until the STATUS register is read. |

| 1 | TSD | R/O | 0b | A thermal shutdown condition was detected. Once set, this bit stays set until the STATUS register is read. A thermal shutdown condition turns off the backlight. |

| 0 | UVLO | R/O | 0b | An input undervoltage lockout condition was detected. Once set, this bit stays set until the STATUS register is read. An undervoltage lockout condition turns off the backlight. |

8.6.1.3 BRTLO

Address: 0x03h

Reset: 0x00h

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| BRT[3:0] | — | ||||||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7:4 | BRT[3:0] | R/W | 0000b | Least significant bits of the 12-bit wide brightness level. If controlling the brightness with 8-bit resolution, writing to this register is not needed. |

| 6:0 | reserved | R/O | 0000b | Reserved. |

8.6.1.4 BRTHI

Address: 0x04h

Reset: 0x00h

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| BRT[11:4] | |||||||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7:0 | BRT[11:4] | R/W | 00h | Most significant bits of the 12-bit wide brightness level. If controlling the brightness with the 8-bit resolution, writing to this register is all that is needed. |

The brightness level can be updated via one (8 bits) or two (16 bits) register writes. The internal brightness level is 12 bits wide and is only updated when the BRTHI register is written. If the BRTHI register is written without a previous write to the BRTLO register, then the lower order bits of the internal brightness is synthesized from the BRTHI register value.

| BRTLO | BRTHI | Brightness | Comments |

|---|---|---|---|

| write 0x95 | write 0xFC | 0xFC9 | BRTLO[3:0] is ignored |

| write 0x10 | write 0xDC | 0xDC1 | set to an exact 12-bit value |

| no write | write 0x8C | 0x8C8 | synthesize low order bits |

| no write | write 0x0C | 0x0C0 | synthesize low order bits |

| no write | write 0x00 | 0x000 | 0% brightness |

| no write | write 0xFF | 0xFFF | 100% brightness |

8.6.1.5 CONFIG

Address: 0x10h

Reset: 0x07h (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| PWMSB | — | AUTO | BRTMODE[1:0] | ||||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7 | PWMSB | R/W | 0b | Enables PWM standby mode 0 = COMMAND.ON alone turns the backlight on/off (Default) 1 = turn off the backlight after 52 ms of PWM pin low |

| 6:3 | reserved | R/O | 0000b | |

| 2 | AUTO | R/W | 1b | Automatic LED string configuration0 = enable LED strings using just LEDEN.ENABLE 1 = disable all open LED strings (Default) |

| 1:0 | BRTMODE | R/W | 11b | Brightness mode

00 = PWM 01 = BRTHI/BRTLO registers 10 = PWM × unshaped BRTHI/BRTLO registers 11 = Unshaped PWM × BRTHI/BRTLO registers |

The AUTO bit is set, and the LED string configuration is done automatically. The LP8557I allows users to disable the auto-detect function by setting AUTO bit to 0b.

8.6.1.6 CURRENT

Address: 0x11h

Reset: 0x07h (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| ISET | —— | MAXCURR[2:0] | |||||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7 | ISET | R/W | 0b | Set full-scale LED current via the ISET pin. 0 = Full-scale current is set with MAXCURR bits. (Default) 1 = Full-scale current is set with an external, RISET, resistor. |

| 6:3 | reserved | R/O | 0000b | |

| 2:0 | MAXCURR | R/W | 111b | Full-scale current (100% brightness). 000 = 5 mA 001 = 10 mA 010 = 13 mA 011 = 15 mA 100 = 18 mA 101 = 20 mA 110 = 23 mA 111 = 25 mA (Default) |

The ISET bit determines how the maximum LED current is set. On the LP8557I (ISET = 0), the maximum LED current is 25 mA. It may be re-configured via the I2C interface by overriding MAXCURR bits. Note that re-configuration must be done every time the power on VDD pin is recycled.

8.6.1.7 PGEN

Address: 0x12h

Reset: 0x29h (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| PFSET | — | THRESHOLD | PRFEQ[2:0] | ||||

The PFSET bit distinguishes how the PWM dimming frequency is set. On the LP8557I (PFSET = 0), the PWM dimming frequency is 9.8 kHz by default. It may be re-configured via I2C interface by overriding PFREQ bits. Note that re-configuration must be done every time the power on VDD pin is recycled.

8.6.1.8 BOOST

Address: 0x13h

Reset: 0x02h (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| BFSET | BCSET | — | BCOMP | BFREQ | |||

The BFSET bit distinguishes how the boost switching frequency is set. If BFSET = 0, the boost switching frequency is set by the BFREQ bit. If BFSET = 1, the switching frequency is set with an external resistor. On the LP8557I (BFSET = 0), the boost switching frequency is 500 kHz by default. It may be re-configured via the I2C interface by overriding the BFREQ bit. Please note the re-configuration must be done every time the power on the VDD pin is recycled.

The BCSET bit distinguishes how the boost inductor and compensation is set. If BCSET = 0, the boost inductor and compensation is set by the BCOMP bit. If BCSET = 1, the boost inductor and compensation is set with an external resistor. On the LP8557I (BCSET = 0), the boost compensation is set to option 1 by default. It may be re-configured via I2C interface by overriding BCOMP bit. Please note the re-configuration must be done every time the power on the VDD pin is recycled.

8.6.1.9 LEDEN

Address: 0x14h

Reset: 0xBFh (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| - | ENABLE[6:1] | ||||||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7:6 | reserved | R/W | 10b | |

| 5:0 | ENABLE | R/W | 111111b | LED string enables. 000001 = Only 1 current sink enabled. . . 001111 = Current sinks 1-4 enabled. 011111 = Current sinks 1-5 enabled. 111111 = All 6 current sinks enabled (Default) |

The ENABLE field configures the strings if the AUTO bit is 0. The LP8557I allows re-configuration of the ENABLE bits via I2C writes. Note that re-configuration must be done every time the power on the VDD pin is recycled.

8.6.1.10 STEP

Address: 0x15h

Reset: 0x00h (LP8557I)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| SMOOTH[1:0] | — | STEP[1:0] | |||||

| Bits | Field | Type | Default | Description |

|---|---|---|---|---|

| 7:6 | SMOOTH | R/W | 00b | Filter strength for digital smoothing filter.

00 = no smoothing (Default) 10 = light smoothing 10 = medium smoothing 11 = heaving smoothing |

| 5:2 | reserved | R/W | 0000b | |

| 1:0 | STEP | R/W | 00b | Ramp time for a 0% to 100% current change.

00 = 0 ms (Default) 01 = 50 ms (12.2 µs/12-bit LSB) 10 = 100 ms (24.4 µs/12-bit LSB) 11 = 200 ms (48.8 µs/12-bit LSB) |

On LP8557I, it is possible to enable slope and advanced slope functions by re-configuration of the STEP and SMOOTH bits appropriately via I2C writes. Note that re-configuration must be done every time power on the VDD pin is recycled.

The STEP field controls the rate of brightness level changes (slope function). Brightness transitions have a fixed step time. The time required to complete a ramp between two levels also depends upon the difference between the starting and ending current levels. For example, when STEP is set to 10b a brightness transition from 0% to 100% takes 100 ms, while a transition from 50% to 100% takes 50 ms.

The SMOOTH field controls the digital smoothing filter (advanced slope function). This filter behaves much like an RC filter. It can be used to remove the overshoot that appears to occur on large brightness changes. The actual amount of smoothing is tailored for the STEP field setting. For example, medium filter strength is higher for 100-ms ramp times than for 50-ms ramp times. This gives 16 possible brightness-level ramping configurations.