JAJSQO4A September 2000 – September 2023 OPA177

PRODUCTION DATA

- 1

- 1特長

- 2アプリケーション

- 3概要

- 4Revision History

- 5Pin Configuration and Functions

- 6Specifications

- 7Application and Implementation

- 8Device and Documentation Support

- 9Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|8

- P|8

サーマルパッド・メカニカル・データ

発注情報

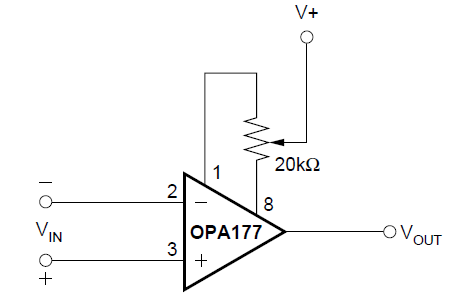

7.2 Typical Application

Trim range is approximately ±3.0

mV.

Figure 7-1 Optional Offset Nulling

Circuit

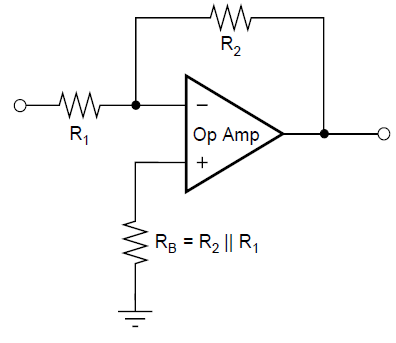

Conventional op amp with

external bias current cancellation resistor.

Figure 7-2 Input Bias Current

Cancellation With Conventional Op Amp

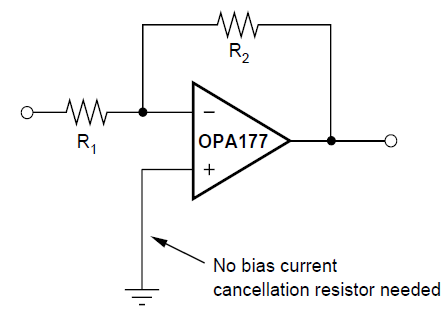

OPA177 with no external bias

current cancellation resistor.

Figure 7-3 Input Bias Current

Cancellation With OPA177