JAJSCY2A November 2016 – January 2017 OPA2316-Q1 , OPA316-Q1 , OPA4316-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

1 特長

2 アプリケーション

- 車載用アプリケーション

- ADAS (先進運転支援システム)

- 車体エレクトロニクスおよび照明

- 電流検出

- バッテリ管理システム

3 概要

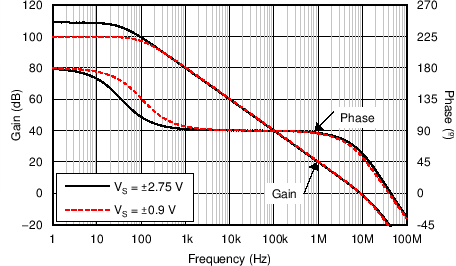

OPAx316-Q1ファミリのシングルおよびデュアル・オペアンプは、新世代の汎用、低消費電力のオペアンプを代表する製品です。レール・ツー・レールの入力および出力、低い静止電流(標準値400μA/ch)、10MHzの広い帯域幅、非常に低いノイズ(1kHzにおいて11nV/√Hz)という特長から、このファミリは優れた速度/電力比を必要とする回路に適しています。

入力バイアス電流が小さいため、これらのオペアンプはメガオームのソース・インピーダンスを持つアプリケーションに対応できます。OPAx316-Q1は入力バイアス電流が小さいため、電流ノイズもごく小さく、高インピーダンスのセンサ・インターフェイスに魅力的な選択肢です。

OPAx316-Q1は堅牢に設計されており、ユニティ・ゲイン安定、RFIおよびEMI除去フィルタの内蔵、オーバードライブ状態で位相反転が発生しない、高い静電放電(ESD)保護(4kV HBM)という特長から、回路設計者が簡単に使用できます。

これらのデバイスは、最小1.8V (±0.9V)、最大5.5V (±2.75V)の低電圧での動作に最適化されています。この車載グレードの低電圧CMOSオペアンプが追加されたことにより、広い帯域幅、低ノイズ、低消費電力で、広範なアプリケーションの要求を満たす製品ファミリとなりました。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(typ) |

|---|---|---|

| OPA316-Q1 | SOT-23 (5) | 1.60mm×2.90mm |

| OPA2316-Q1 | VSSOP (8) | 3.00mm×3.00mm |

| OPA4316-Q1 | TSSOP (14) | 4.40mm×5.00mm |

- 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

シングル・ポールのローパス・フィルタ

10MHz帯域幅での低い消費電流(400µA/ch)