SLLS396G SEPTEMBER 1999 – December 2015 SN65LVDS104 , SN65LVDS105

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Selection Guide to LVDS Repeaters

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings—JEDEC

- 7.3 ESD Ratings—MIL-STD

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 SN65LVDS104 Electrical Characteristics

- 7.7 SN65LVDS105 Electrical Characteristics

- 7.8 SN65LVDS104 Switching Characteristics

- 7.9 SN65LVDS105 Switching Characteristics

- 7.10 Dissipation Ratings

- 7.11 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Point-to-Point Communications

- 10.2.2 Design Requirements

- 10.2.3

Detailed Design Procedure

- 10.2.3.1 Bypass Capacitance

- 10.2.3.2 Driver Supply Voltage

- 10.2.3.3 Driver Input Voltage

- 10.2.3.4 Driver Output Voltage

- 10.2.3.5 Interconnecting Media

- 10.2.3.6 PCB Transmission Lines

- 10.2.3.7 Termination Resistor

- 10.2.3.8 Receiver Supply Voltage

- 10.2.3.9 Receiver Input Common-Mode Range

- 10.2.3.10 Receiver Input Signal

- 10.2.3.11 Receiver Output Signal

- 10.2.4 Application Curve

- 10.3 Multidrop Communications

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PW|16

- D|16

サーマルパッド・メカニカル・データ

発注情報

12 Layout

12.1 Layout Guidelines

12.1.1 Microstrip vs. Stripline Topologies

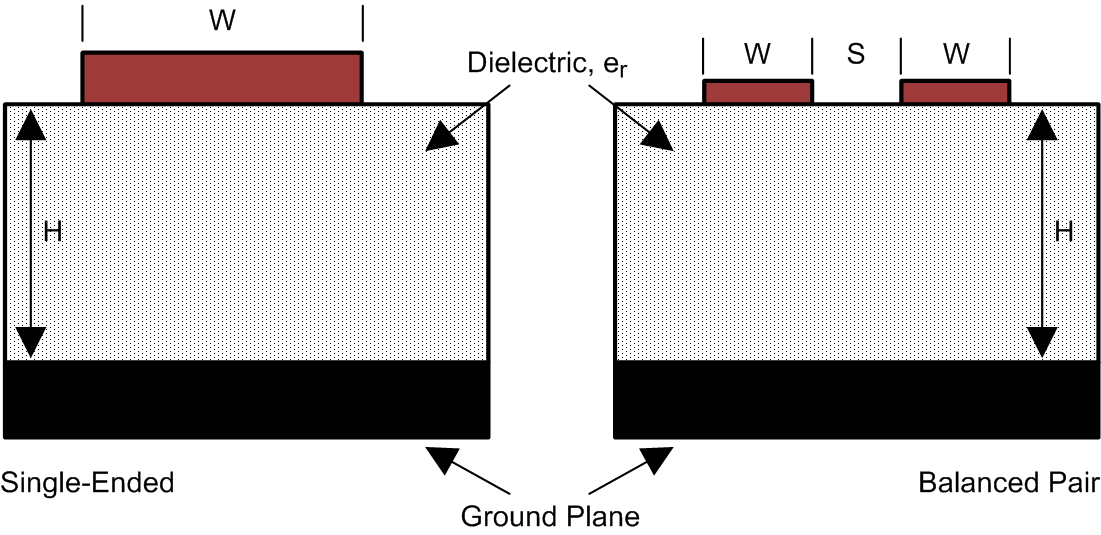

As per SLLD009, printed-circuit boards usually offer designers two transmission line options: microstrip and stripline. Microstrips are traces on the outer layer of a PCB, as shown in Figure 42.

Figure 42. Microstrip Topology

Figure 42. Microstrip Topology

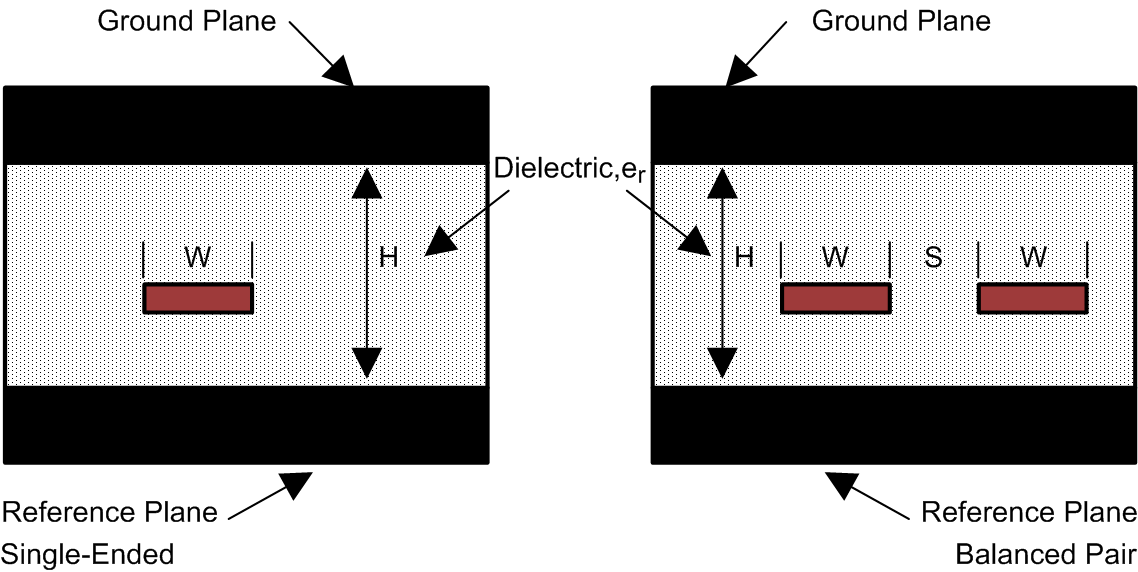

On the other hand, striplines are traces between two ground planes. Striplines are less prone to emissions and susceptibility problems because the reference planes effectively shield the embedded traces. However, from the standpoint of high-speed transmission, juxtaposing two planes creates additional capacitance. TI recommends routing LVDS signals on microstrip transmission lines, if possible. The PCB traces allow designers to specify the necessary tolerances for ZO based on the overall noise budget and reflection allowances. Footnotes (1), (2)and (3)provide formulas for ZO and tPD for differential and single-ended traces.

Figure 43. Stripline Topology

Figure 43. Stripline Topology

12.1.2 Dielectric Type and Board Construction

The speeds at which signals travel across the board dictates the choice of dielectric. FR-4, or equivalent, usually provides adequate performance for use with LVDS signals. If rise or fall times of TTL/CMOS signals are less than 500 ps, empirical results indicate that a material with a dielectric constant near 3.4, such as Rogers™ 4350 or Nelco N4000-13 is better suited. Once the designer chooses the dielectric, there are several parameters pertaining to the board construction that can affect performance. The following set of guidelines were developed experimentally through several designs involving LVDS devices:

- Copper weight: 15 g or 1/2 oz start, plated to 30 g or 1 oz

- All exposed circuitry must be solder-plated (60/40) to 7.62 μm or 0.0003 in. (minimum)

- Copper must must be 25.4 μm or 0.001 in. (minimum)

12.1.3 Recommended Stack Layout

Following the choice of dielectrics and design specifications, you must decide how many levels to use in the stack. To reduce the TTL/CMOS to LVDS crosstalk, it is a good practice to have at least two separate signal planes as shown in Figure 44.

Figure 44. Four-Layer PCB Board

Figure 44. Four-Layer PCB Board

NOTE

The separation between layers 2 and three should be 127 µm (0.005 in). By keeping the power and ground planes tightly coupled, the increased capacitance acta as a bypass for transients.

One of the most common stack configurations is the six-layer board as shown in Figure 45

Figure 45. Six-Layer PCB Board

Figure 45. Six-Layer PCB Board

In this particular configuration, it is possible to isolate each signal layer from the power plane by at least one ground plane. The result is improved signal integrity; however, fabrication is more expensive. Using the 6-layer board is preferable, because it offers the layout designer more flexibility in varying the distance between signal layers and referenced planes, in addition to ensuring reference to a ground plane for signal layers 1 and 6.

12.1.4 Separation Between Traces

The separation between traces depends on several factors. However, the amount of coupling that can be tolerated usually dictates the actual separation. Low noise coupling requires close coupling between the differential pair of an LVDS link to benefit from the electromagnetic field cancellation. The traces must be 100-Ω differential and thus coupled in the manner that best fits this requirement. In addition, differential pairs must have the same electrical length to ensure that they are balanced, thus minimizing problems with skew and signal reflection.

In the case of two adjacent single-ended traces, one must use the 3-W rule, which stipulates that the distance between two traces must be greater than two times the width of a single trace, or three times its width measured from trace center to trace center. This increased separation effectively reduces the potential for crosstalk. The same rule must be applied to the separation between adjacent LVDS differential pairs, whether the traces are edge-coupled or broad-side-coupled.

Figure 46. 3-W Rule for Single-Ended and Differential Traces (Top View)

Figure 46. 3-W Rule for Single-Ended and Differential Traces (Top View)

You must exercise caution when using autorouters, because they do not always account for all factors affecting crosstalk and signal reflection. For instance, it is best to avoid sharp 90° turns to prevent discontinuities in the signal path. Using successive 45° turns tends to minimize reflections.

12.1.5 Crosstalk and Ground Bounce Minimization

To reduce crosstalk, it is important to provide a return path to high-frequency currents that is as close as possible to its originating trace. A ground plane usually achieves this. Because the returning currents always choose the path of lowest inductance, they are most likely to return directly under the original trace, thus minimizing crosstalk. Lowering the area of the current loop lowers the potential for crosstalk. Traces kept as short as possible with an uninterrupted ground plane running beneath them emit the minimum amount of electromagnetic field strength. Discontinuities in the ground plane increase the return path inductance and must be avoided.

12.1.6 Decoupling

Each power or ground lead of a high-speed device must be connected to the PCB through a low inductance path. For best results, one or more vias are used to connect a power or ground pin to the nearby plane. Ideally, via placement is immediately adjacent to the pin to avoid adding trace inductance. Placing a power plane closer to the top of the board reduces the effective via length and its associated inductance.

Figure 47. Low Inductance, High-Capacitance Power Connection

Figure 47. Low Inductance, High-Capacitance Power Connection

Bypass capacitors must be placed close to VDD pins. They can be placed conveniently near the corners or underneath the package to minimize the loop area. This extends the useful frequency range of the added capacitance. Small-physical-size capacitors, such as 0402 or even 0201, or X7R surface-mount capacitors must be used to minimize body inductance of capacitors. Each bypass capacitor is connected to the power and ground plane through vias tangent to the pads of the capacitor as shown in Figure 48(a).

An X7R surface-mount capacitor of size 0402 has about 0.5 nH of body inductance. At frequencies above 30 MHz or so, X7R capacitors behave as low-impedance inductors. To extend the operating frequency range to a few hundred MHz, an array of different capacitor values like 100 pF, 1 nF, 0.03 μF, and 0.1 μF are commonly used in parallel. The most effective bypass capacitor can be built using sandwiched layers of power and ground at a separation of 2 to 3 mils. With a 2-mil FR4 dielectric, there is approximately 500 pF per square inch of PCB. Refer back to Figure 5-1 for some examples. Many high-speed devices provide a low-inductance GND connection on the backside of the package. This center dap must be connected to a ground plane through an array of vias. The via array reduces the effective inductance to ground and enhances the thermal performance of the small Surface Mount Technology (SMT) package. Placing vias around the perimeter of the dap connection ensures proper heat spreading and the lowest possible die temperature. Placing high-performance devices on opposing sides of the PCB using two GND planes (as shown in Figure 46) creates multiple paths for heat transfer. Often thermal PCB issues are the result of one device adding heat to another, resulting in a very high local temperature. Multiple paths for heat transfer minimize this possibility. In many cases the GND dap that is so important for heat dissipation makes the optimal decoupling layout impossible to achieve due to insufficient padto- dap spacing as shown in Figure 48(b). When this occurs, placing the decoupling capacitor on the backside of the board keeps the extra inductance to a minimum. It is important to place the VDD via as close to the device pin as possible while still allowing for sufficient solder mask coverage. If the via is left open, solder may flow from the pad and into the via barrel. This will result in a poor solder connection.

Figure 48. Typical Decoupling Capacitor Layouts

Figure 48. Typical Decoupling Capacitor Layouts

12.2 Layout Example

At least two or three times the width of an individual trace must separate single-ended traces and differential pairs to minimize the potential for crosstalk. Single-ended traces that run in parallel for less than the wavelength of the rise or fall times usually have negligible crosstalk. Increase the spacing between signal paths for long parallel runs to reduce crosstalk. Boards with limited real estate can benefit from the staggered trace layout, as shown in Figure 49.

Figure 49. Staggered Trace Layout

Figure 49. Staggered Trace Layout

This configuration lays out alternating signal traces on different layers; thus, the horizontal separation between traces can be less than 2 or 3 times the width of individual traces. To ensure continuity in the ground signal path, TI recommends having an adjacent ground via for every signal via, as shown in Figure 50. Note that vias create additional capacitance. For example, a typical via has a lumped capacitance effect of 1/2 pF to 1 pF in FR4.

Figure 50. Ground Via Location

Figure 50. Ground Via Location

Short and low-impedance connection of the device ground pins to the PCB ground plane reduces ground bounce. Holes and cutouts in the ground planes can adversely affect current return paths if they create discontinuities that increase returning current loop areas.

To minimize EMI problems, TI recommends avoiding discontinuities below a trace (for example, holes, slits, and so on) and keeping traces as short as possible. Zoning the board wisely by placing all similar functions in the same area, as opposed to mixing them together, helps reduce susceptibility issues.