JAJSQM4C July 2003 – April 2024 SN74AHC125-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 デバイスおよびドキュメントのサポート

- 9 メカニカル、パッケージ、および注文情報

- 10改訂履歴

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|14

- PW|14

- BQA|14

サーマルパッド・メカニカル・データ

- BQA|14

発注情報

3 概要

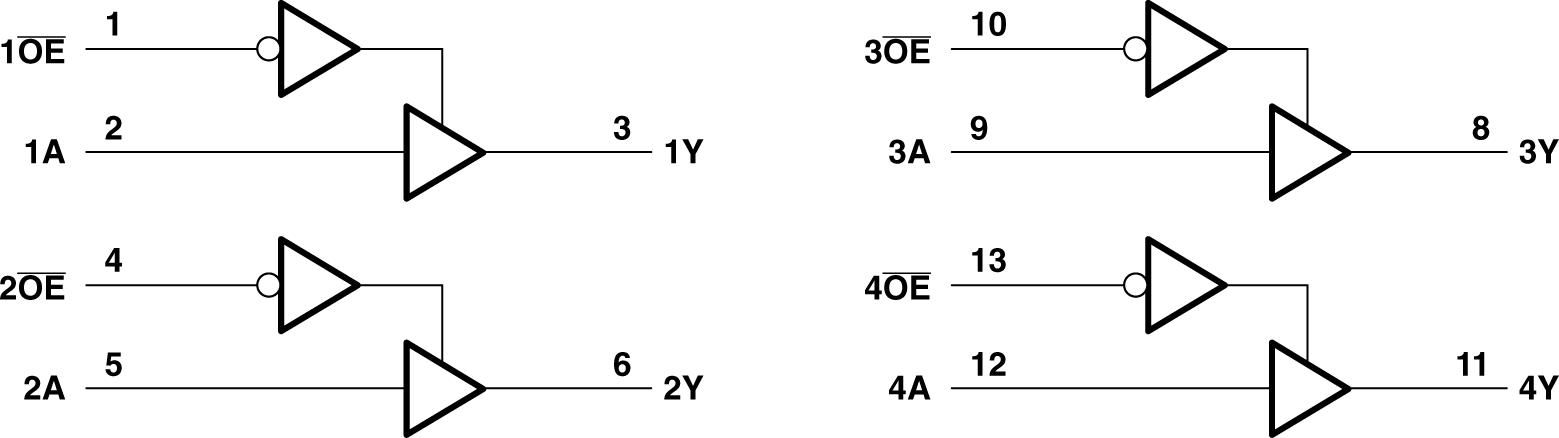

SN74AHC125-Q1 はクワッド バス バッファ ゲートで、3 ステート出力の独立したライン ドライバを備えています。各出力は、対応する出力イネーブル (OE) 入力が High のときディセーブルになります。OE が Low の場合、該当するゲートは A 入力からのデータをその Y 出力に渡します。

電源投入または電源オフの間にデバイスを高インピーダンス状態にするには、OE をプルアップ抵抗を介して VCC に接続します。この抵抗の最小値は、ドライバの電流シンク能力によって決まります。

パッケージ情報

| 部品番号 | パッケージ1 | パッケージ サイズ 2 |

|---|---|---|

| SN74AHC125-Q1 | D (SOIC、14) | 8.65mm × 6mm |

| PW (TSSOP、14) | 5mm × 6.4mm | |

| BQA (WQFN、14) | 3mm × 2.5mm |

(1) 詳細については、セクション 9 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

論理図 (正論理)

論理図 (正論理)