JAJSRG2F October 2004 – October 2024 SN74AHC1G08-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DBV|5

- DCK|5

サーマルパッド・メカニカル・データ

発注情報

3 概要

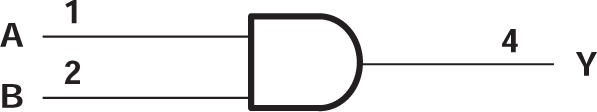

SN74AHC1G08 はシングル 2 入力正論理 AND ゲートです。本デバイスはブール関数 Y = A • B を正論理で実行します。

パッケージ情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| SN74AHC1G08-Q1 | DBV (SOT-23、5) | 2.9mm × 2.8 mm | 2.9mm × 1.6 mm |

| DCK (SOT-SC70、5) | 2.00mm × 1.25 mm | 2mm × 1.25 mm | |

| DTX (X2SON、5) | 1.1 mm × 0.85mm | 1.1 mm × 0.85mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

論理図 (正論理)

論理図 (正論理)