-

SNx4AHCT373 3 ステート出力、オクタル・トランスペアレント D タイプ・ラッチ JAJSQW1O October 1995 – August 2024 SN54AHCT373 , SN74AHCT373

PRODMIX

-

SNx4AHCT373 3 ステート出力、オクタル・トランスペアレント D タイプ・ラッチ

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DB|20

- NS|20

- N|20

- DW|20

- PW|20

サーマルパッド・メカニカル・データ

発注情報

Data Sheet

SNx4AHCT373 3 ステート出力、オクタル・トランスペアレント D タイプ・ラッチ

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- 入力は TTL 電圧互換

- JESD 17 準拠で 250mA 超のラッチアップ性能

2 概要

’AHCT373 デバイスはオクタル トランスペアレント D タイプ ラッチです。ラッチ イネーブル (LE) 入力が HIGH の場合、Q 出力はデータ (D) 入力に従います。LE を LOW にすると、D 入力のロジック レベルで Q 出力がラッチされます。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| SN54AHCT373 | J (CDIP、20) | 24.2mm × 7.62mm | 24.2mm × 6.92mm |

| W (CFP、20) | 13.09mm × 8.13mm | 13.09mm × 6.92mm | |

| FK (LCCC、20) | 8.89 mm × 8.89 mm | 8.89mm × 8.89mm | |

| SN74AHCT373 | DB (SSOP、20) | 7.2mm × 7.8mm | 7.50mm × 5.30mm |

| DW (SOIC、20) | 12.80mm × 10.3mm | 12.8mm × 7.5mm | |

| NS (SOP、20) | 12.60mm × 7.8mm | 12.6mm × 5.30mm | |

| N (PDIP、20) | 24.33mm × 9.4mm | 25.40mm × 6.35 mm | |

| PW (TSSOP、20) | 6.50mm × 6.4mm | 6.50mm × 4.40mm |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

論理図 (正論理)

論理図 (正論理)3 Pin Configuration and Functions

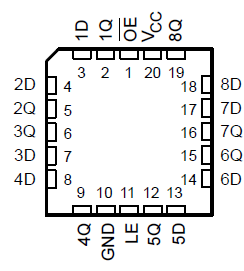

Figure 3-1 SN54AHCT373 J or W

Package; SN74AHCT373 DB, DGV, DW, N, NS, or PW Package (Top View)

Figure 3-1 SN54AHCT373 J or W

Package; SN74AHCT373 DB, DGV, DW, N, NS, or PW Package (Top View) Figure 3-2 SN54AHCT373 FK Package (Top View)

Figure 3-2 SN54AHCT373 FK Package (Top View)Table 3-1 Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NO. | NAME | ||

| 1 | OE | I | Output Enable |

| 2 | 1Q | O | 1Q Output |

| 3 | 1D | I | 1D Input |

| 4 | 2D | I | 2D Input |

| 5 | 2Q | O | 2Q Output |

| 6 | 3Q | O | 3Q Output |

| 7 | 3D | I | 3D Input |

| 8 | 4D | I | 4D Input |

| 9 | 4Q | O | 4Q Output |

| 10 | GND | — | Ground |

| 11 | LE | I | Latch Enable |

| 12 | 5Q | O | 5Q Output |

| 13 | 5D | I | 5D Input |

| 14 | 6D | I | 6D Input |

| 15 | 6Q | O | 6Q Output |

| 16 | 7Q | O | 7Q Output |

| 17 | 7D | I | 7D Input |

| 18 | 8D | I | 8D Input |

| 19 | 8Q | O | 8Q Output |

| 20 | VCC | — | Power Pin |