JAJSNX0I December 1982 – September 2024 SN54HC112 , SN74HC112

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 アプリケーションと実装

- 9 デバイスおよびドキュメントのサポート

- 10改訂履歴

- 11メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- N|16

- D|16

サーマルパッド・メカニカル・データ

発注情報

3 概要

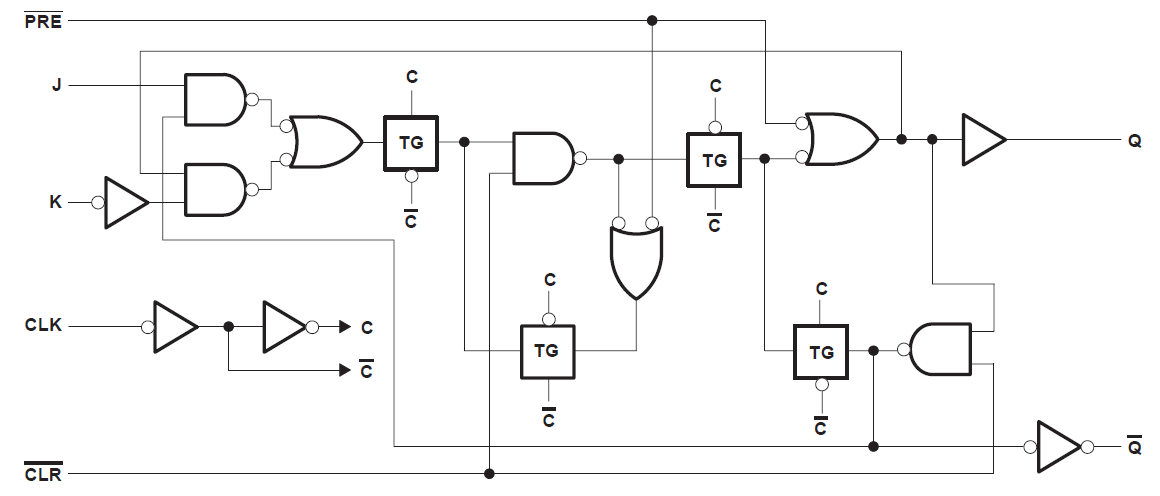

SNx4HC112 デバイスには、2 つの独立した J-K ネガティブ エッジ トリガ フリップ フロップが含まれています。その他の入力のレベルに関係なく、プリセット (PRE) 入力を Low レベルにすると出力は High になり、クリア (CLR) 入力を Low レベルにすると出力は Low になります。PRE と CLR が非アクティブ (HIGH) の場合、セットアップ時間の要件を満たす J 入力と K 入力のデータは、クロック (CLK) パルスの負方向エッジで出力に転送されます。クロックのトリガは電圧レベルで発生し、CLK パルスの立ち下がり時間とは直接関係しません。ホールド時間が経過した後、J 入力と K 入力のデータは、出力のレベルに影響を及ぼさずに変化させることができます。これらの汎用フリップ フロップは、J と K を HIGH に接続することで、トグル フリップ フロップとしての動作を実行します。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (公称)(3) |

|---|---|---|---|

| SNx4HC112 | J (CDIP、16) | 19.56mm × 6.92 mm | 19.56mm × 6.92 mm |

| D (SOIC、16) | 9.9mm × 6 mm | 9.9mm × 3.9 mm | |

| N (PDIP、16) | 19.3mm × 9.4 mm | 19.3mm × 6.35 mm | |

| FK (LCCC、20) | 8.89mm × 8.89 mm | 8.89mm × 8.89 mm | |

| W (CFP、16) | 10.3mm × 6.73 mm | 10.3mm × 6.73 mm |

(1) 詳細については、セクション 11 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

機能ブロック図

機能ブロック図