JAJSNY2H March 1984 – August 2024 SN54HCT240 , SN74HCT240

PRODUCTION DATA

- 1

- 1 特長

- 2 概要

- 3 ピン構成および機能

- 4 仕様

- 5 パラメータ測定情報

- 6 詳細説明

- 7 アプリケーションと実装

- 8 デバイスおよびドキュメントのサポート

- 9 改訂履歴

- 10メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- NS|20

- N|20

- DGS|20

- DW|20

- PW|20

サーマルパッド・メカニカル・データ

発注情報

2 概要

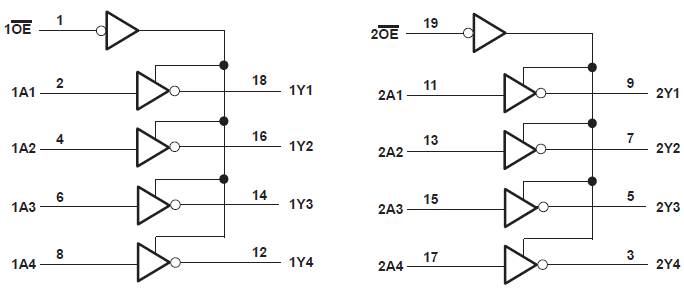

これらの 8 進バッファ / ライン ドライバは、3 ステート メモリ アドレス ドライバ、クロック ドライバ、バス用レシーバ / トランスミッタの性能と密度の両方を向上することに特化して設計されています。’HCT240 デバイスは、独立した出力イネーブル (OE) 入力を備えた 2 つの 4 ビット バッファ / ドライバで構成されています。OE が Low の場合、デバイスは A 入力の反転データを Y 出力に渡します。OE が High の場合、出力は高インピーダンス状態になります。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| SN74HCT240 | DGS (VSSOP、20) | 5.1mm × 4.9 mm | 5.1 mm × 3mm |

| DW (SOIC、20) | 12.80mm × 10.3mm | 12.80mm × 7.50mm | |

| PDIP (20) | 24.33mm × 9.4 mm | 24.33 mm × 6.35mm | |

| NS (SOP、20) | 12.6mm × 7.8mm | 12.6mm × 5.3mm | |

| PW (TSSOP、20) | 6.50mm × 6.4mm | 6.50mm × 4.40mm | |

| SN54HCT240 | J (CDIP、20) | 24.2mm × 7.62mm | 24.2 mm × 6.92mm |

| FK (LCCC、20) | 8.9mm × 8.9mm | 8.9mm × 8.9mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

機能ブロック図

機能ブロック図