JAJSVF5 October 2024 SN74LV4040B-EP

PRODUCTION DATA

3 概要

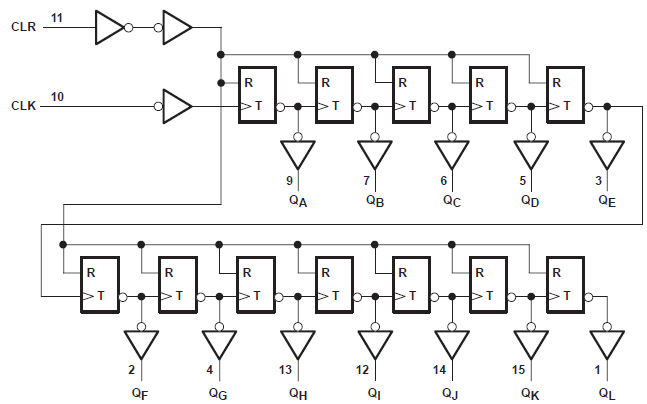

SN74LV4040B-EP は 12 ビット非同期バイナリカウンタで、すべての段の出力を外部で使用できます。クリア (CLR) 入力が HIGH レベルになると、非同期でカウンタをクリアし、すべての出力を LOW にリセットします。クロック (CLK) 入力が HIGH から LOW へ遷移するときに、カウントが進みます。アプリケーションとしては、時間遅延回路、カウンタ制御、周波数分割回路があります。

SN74LV4040B-EP は、Ioff を使用する部分的パワーダウン アプリケーション用に完全に動作が規定されています。Ioff 回路が出力をディセーブルにするため、電源切断時にデバイスに電流が逆流して損傷に至ることを回避できます。

- 詳細については、セクション 12 を参照してください。

- パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

- 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

図 3-1 概略論理図 (正論理)

図 3-1 概略論理図 (正論理)