JAJSPD6K april 1998 – february 2023 SN74LV574A

PRODMIX

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements, VCC = 2.5 V ± 0.2 V

- 6.7 Timing Requirements, VCC = 3.3 V ± 0.3 V

- 6.8 Timing Requirements, VCC = 5 V ± 0.5 V

- 6.9 Switching Characteristics, VCC = 2.5 V ± 0.2 V

- 6.10 Switching Characteristics, VCC = 3.3 V ± 0.3 V

- 6.11 Switching Characteristics, VCC = 5 V ± 0.5 V

- 6.12 Noise Characteristics

- 6.13 Operating Characteristics

- 6.14 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DGV|20

- DB|20

- NS|20

- PW|20

- DW|20

- RGY|20

サーマルパッド・メカニカル・データ

- RGY|20

発注情報

3 概要

'LV574A デバイスは、2V~5.5V の VCC で動作するように設計された、オクタル・エッジ・トリガ型 D タイプ・フリップ・フロップです。

これらのデバイスは、大きな容量性負荷または比較的低いインピーダンスの負荷の駆動用に設計された 3 ステート出力を備えています。本デバイスは、バッファ・レジスタ、I/O ポート、双方向バス・ドライバ、およびワーキング・レジスタの実装に特に適しています。

クロック (CLK) 入力の立ち上がり遷移時に、Q 出力がデータ (D) 入力で設定されたロジック・レベルに設定されます。

パッケージ情報(1)

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| SN74LV574A | DB (SSOP、16) | 6.2 × 5.3mm |

| DGV (TVSOP、16) | 3.6 × 4.4mm | |

| DW (SOIC、16) | 10.3 × 7.5mm | |

| NS (SOP、16) | 10.3 × 5.3mm | |

| PW (TSSOP、16) | 5 × 4.4mm | |

| RGY (VQFN、16) | 4 × 3.5mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

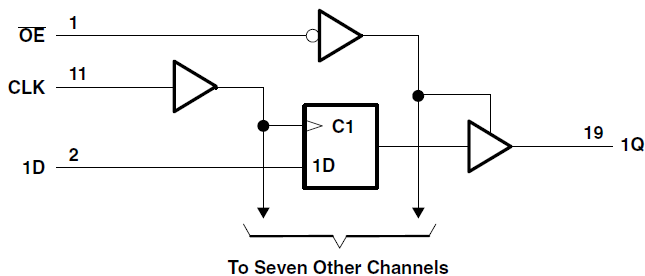

論理図 (正論理)

論理図 (正論理)