JAJSPD6K april 1998 – february 2023 SN74LV574A

PRODMIX

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements, VCC = 2.5 V ± 0.2 V

- 6.7 Timing Requirements, VCC = 3.3 V ± 0.3 V

- 6.8 Timing Requirements, VCC = 5 V ± 0.5 V

- 6.9 Switching Characteristics, VCC = 2.5 V ± 0.2 V

- 6.10 Switching Characteristics, VCC = 3.3 V ± 0.3 V

- 6.11 Switching Characteristics, VCC = 5 V ± 0.5 V

- 6.12 Noise Characteristics

- 6.13 Operating Characteristics

- 6.14 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DGV|20

- DB|20

- NS|20

- PW|20

- DW|20

- RGY|20

サーマルパッド・メカニカル・データ

- RGY|20

発注情報

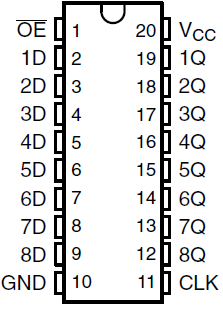

5 Pin Configuration and Functions

Figure 5-1 DB, DGV, DW, NS, or PW

Package (Top View)

Figure 5-1 DB, DGV, DW, NS, or PW

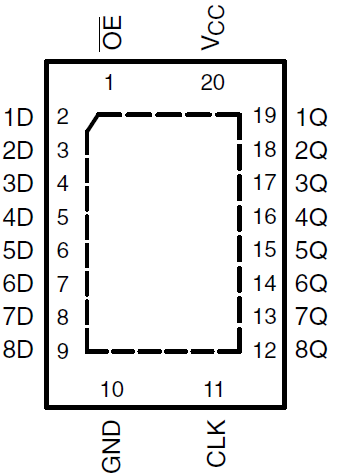

Package (Top View) Figure 5-2 RGY Package (Top

View)

Figure 5-2 RGY Package (Top

View)Table 5-1 Pin Functions

| PIN | TYPE | Description | ||

|---|---|---|---|---|

| NO. | NAME | |||

| 1 | OE | I | Clear all channels, active low | |

| 2 | 1D | I | Channel 1, D input | |

| 3 | 2D | I | Channel 2, D input | |

| 4 | 3D | I | Channel 3, D input | |

| 5 | 4D | I | Channel 4, D input | |

| 6 | 5D | I | Channel 5, D input | |

| 7 | 6D | I | Channel 6, D input | |

| 8 | 7D | I | Channel 7, D input | |

| 9 | 8D | I | Channel 8, D input | |

| 10 | GND | — | Ground | |

| 11 | CLK | I | Clock Pin | |

| 12 | 8Q | O | Channel 8, Q output | |

| 13 | 7Q | O | Channel 7, Q output | |

| 14 | 6Q | O | Channel 6, Q output | |

| 15 | 5Q | O | Channel 5, Q output | |

| 16 | 4Q | O | Channel 4, Q output | |

| 17 | 3Q | O | Channel 3, Q output | |

| 18 | 2Q | O | Channel 2, Q output | |

| 19 | 1Q | O | Channel 1, Q output | |

| 20 | VCC | — | Power Pin | |