JAJST35W January 1993 – December 2024 SN54LVC74A , SN74LVC74A

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 アプリケーションと実装

- 9 デバイスおよびドキュメントのサポート

- 10改訂履歴

- 11メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|14

- RGY|14

- DB|14

- PW|14

- BQA|14

- NS|14

サーマルパッド・メカニカル・データ

発注情報

4 ピン構成および機能

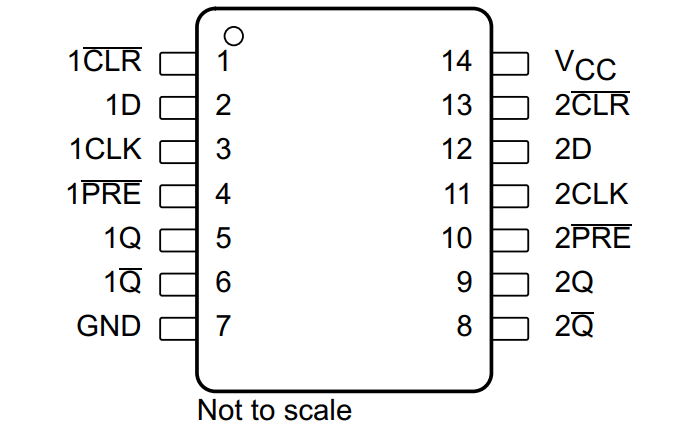

図 4-1

D、DB、J、PW、NS、または W パッケージ

14 ピン SOIC、SSOP、CDIP、TSSOP、SO または CFP

(上面図)

図 4-1

D、DB、J、PW、NS、または W パッケージ

14 ピン SOIC、SSOP、CDIP、TSSOP、SO または CFP

(上面図)

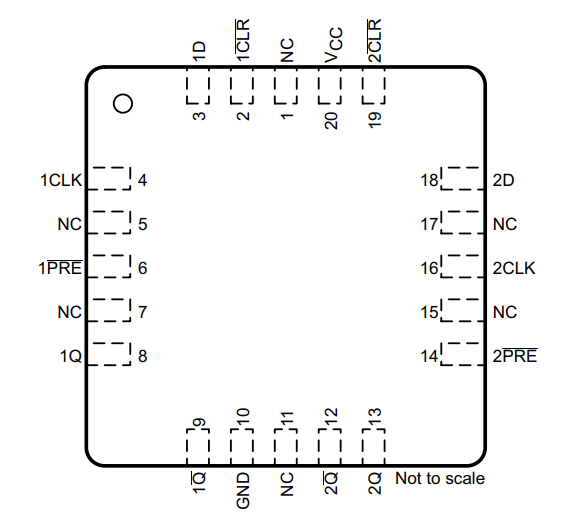

図 4-3

FK パッケージ

20 ピン LCCC

(上面図)

図 4-3

FK パッケージ

20 ピン LCCC

(上面図)

図 4-2

BQA または RGY パッケージ、

14 ピン WQFN または VQFN (露出サーマル パッド付き)

(上面図)

図 4-2

BQA または RGY パッケージ、

14 ピン WQFN または VQFN (露出サーマル パッド付き)

(上面図)

表 4-1 ピンの機能

| ピン | I/O | 説明 | ||

|---|---|---|---|---|

| 名称 | CDIP、CFP、PDIP、SO、SOIC、SSOP、TSSOP、VQFN | LCCC | ||

| 1CLK | 3 | 4 | I | チャネル 1 クロック入力 |

| 1 CLR | 1 | 2 | I | チャネル 1 クリア入力。Low にすると、Q 出力 が Low になります。 |

| 1D | 2 | 3 | I | チャネル 1 データ入力 |

| 1 PRE | 4 | 6 | I | チャネル 1 プリセット入力。Low にすると、Q 出力が High になります。 |

| 1Q | 5 | 8 | O | チャネル 1 出力 |

| 1 Q | 6 | 9 | O | チャネル 1 反転出力 |

| 2CLK | 11 | 16 | I | チャネル 2 クロック入力 |

| 2 CLR | 13 | 19 | I | チャネル 2 クリア入力。Low にすると、Q 出力 が Low になります。 |

| 2D | 12 | 18 | I | チャネル 2 データ入力 |

| 2 PRE | 10 | 14 | I | チャネル 2 プリセット入力。Low にすると、Q 出力が High になります。 |

| 2Q | 9 | 13 | O | チャネル 2 出力 |

| 2 Q | 8 | 12 | O | チャネル 2 反転出力 |

| GND | 7 | 10 | — | グランド |

| NC | — | 1、5、7、11、15、17 | — | 無接続 |

| VCC | 14 | 20 | — | 電源 |