JAJSUB2E August 1990 – April 2024 SN75ALS172A

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- N|16

- DW|20

サーマルパッド・メカニカル・データ

発注情報

3 概要

SN75ALS172A は、トライステート差動出力を備えた 4 つのライン ドライバで構成されています。これらのドライバは ANSI 標準 EIA/TIA-422-B、RS-485、ITU 勧告 V.11 の要件を満たすように設計されています。本デバイスは、最高 20Mbaud の速度で、平衡マルチポイント バス伝送を行うように最適化されています。各ドライバには、広い正および負の同相出力電圧範囲があり、ノイズの多い環境でのパーティライン アプリケーションに適しています。

SN75ALS172A には、正および負の電流制限とサーマル シャットダウンがあり、伝送バス ラインのライン フォルト状況から保護します。シャットダウンは、接合部温度が約 150℃で発生します。

SN75ALS172A は、0℃~70℃で動作特性が規定されています。

パッケージ情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) |

|---|---|---|

| SN75ALS172A | SOIC (DW、20) | 12.8mm × 10.3mm |

| PDIP (N、16) | 19.3mm × 9.4mm |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

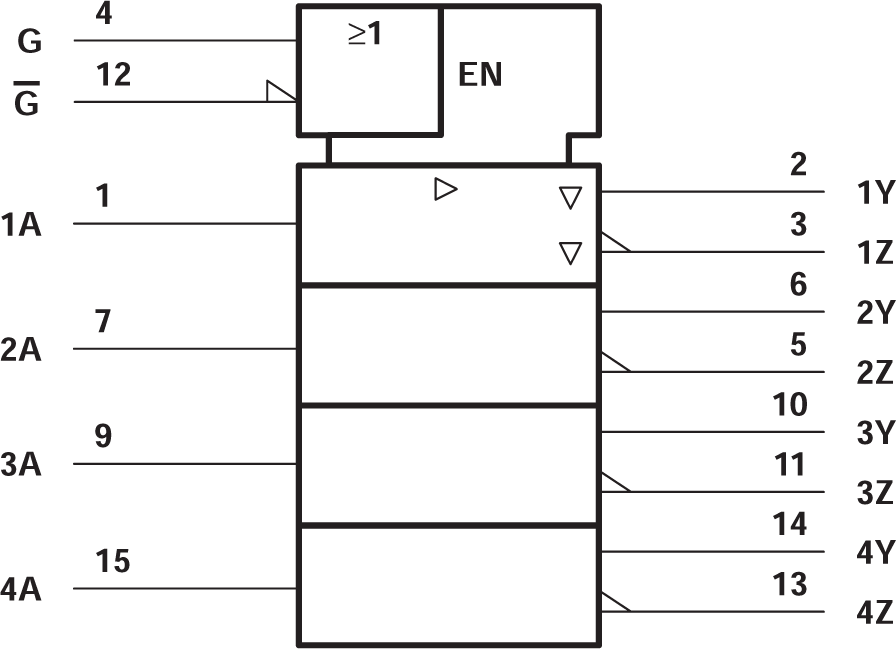

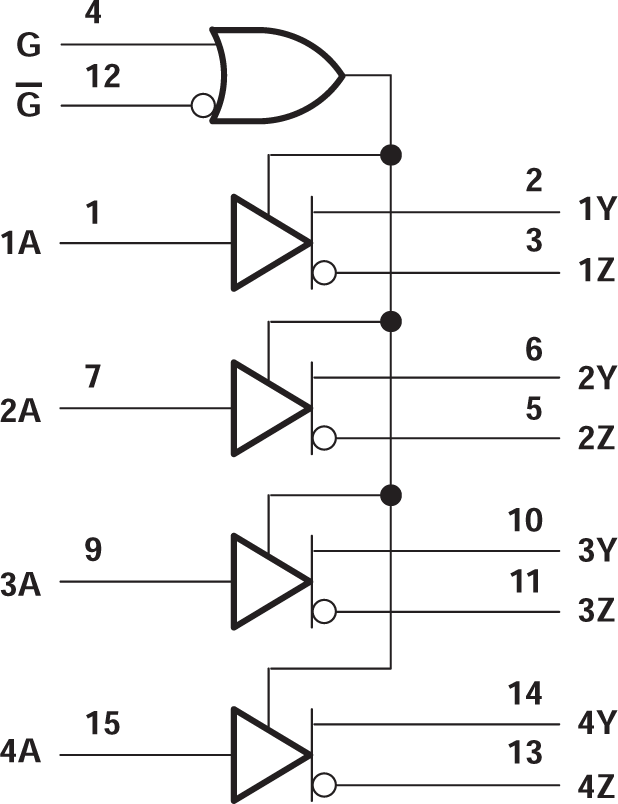

論理記号(1)

論理記号(1)

A. ここに示すピン番号は、N パッケージのものです。

論理図 (正論理)†. この記号は ANSI/IEEE 規格 91-1984 と IEC Publication 617-12 に準拠しています。