JAJSP37B july 2022 – july 2023 TAS2781

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

- 7 パラメータ測定情報

-

8 詳細説明

- 8.1 概要

- 8.2 機能ブロック図

- 8.3 機能説明

- 8.4 デバイスの機能モード

- 8.5 動作モード

- 8.6 TAS2781 のフォルトとステータス

- 8.7 電源シーケンス要件

- 8.8 デジタル入力プルダウン

- 8.9

レジスタ・マップ

- 8.9.1 ページ=0x00 アドレス=0x00 [リセット=00h]

- 8.9.2 ページ=0x00 アドレス=0x01 [リセット=00h]

- 8.9.3 ページ=0x00 アドレス=0x02 [リセット=1Ah]

- 8.9.4 ページ=0x00 アドレス=0x03 [リセット=28h]

- 8.9.5 ページ=0x00 アドレス=0x04 [リセット=21h]

- 8.9.6 ページ=0x00 アドレス=0x05 [リセット=41h]

- 8.9.7 ページ=0x00 アドレス=0x06 [リセット=00h]

- 8.9.8 ページ=0x00 アドレス=0x07 [リセット=20h]

- 8.9.9 ページ=0x00 アドレス=0x08 [リセット=09h]

- 8.9.10 ページ=0x00 アドレス=0x09 [リセット=02h]

- 8.9.11 ページ=0x00 アドレス=0x0A [リセット=0Ah]

- 8.9.12 ページ=0x00 アドレス=0x0C [リセット=10h]

- 8.9.13 ページ=0x00 アドレス=0x0D [リセット=13h]

- 8.9.14 ページ=0x00 アドレス=0x0E [リセット=C2h]

- 8.9.15 ページ=0x00 アドレス=0x0F [リセット=40h]

- 8.9.16 ページ=0x00 アドレス=0x10 [リセット=04h]

- 8.9.17 ページ=0x00 アドレス=0x13 [リセット=08h]

- 8.9.18 ページ=0x00 アドレス=0x15 [リセット=00h]

- 8.9.19 ページ=0x00 アドレス=0x16 [リセット=12h]

- 8.9.20 ページ=0x00 アドレス=0x17 [リセット=80h]

- 8.9.21 ページ=0x00 アドレス=0x1A [リセット=00h]

- 8.9.22 ページ=0x00 アドレス=0x1B [リセット=62h]

- 8.9.23 ページ=0x00 アドレス=0x1C [リセット=36h]

- 8.9.24 ページ=0x00 アドレス=0x1D [リセット=00h]

- 8.9.25 ページ=0x00 アドレス=0x1F [リセット=01h]

- 8.9.26 ページ=0x00 アドレス=0x20 [リセット=2Eh]

- 8.9.27 ページ=0x00 アドレス=0x34 [リセット=06h]

- 8.9.28 ページ=0x00 アドレス=0x35 [リセット=BDh]

- 8.9.29 ページ=0x00 アドレス=0x36 [リセット=ADh]

- 8.9.30 ページ=0x00 アドレス=0x37 [リセット=A8h]

- 8.9.31 ページ=0x00 アドレス=0x38 [リセット=00h]

- 8.9.32 ページ=0x00 アドレス=0x3B [リセット=FCh]

- 8.9.33 ページ=0x00 アドレス=0x3C [リセット=BBh]

- 8.9.34 ページ=0x00 アドレス=0x3D [リセット=DDh]

- 8.9.35 ページ=0x00 アドレス=0x40 [リセット=F6h]

- 8.9.36 ページ=0x00 アドレス=0x41 [リセット=14h]

- 8.9.37 ページ=0x00 アドレス=0x42 [リセット=00h]

- 8.9.38 ページ=0x00 アドレス=0x43 [リセット=00h]

- 8.9.39 ページ=0x00 アドレス=0x44 [リセット=00h]

- 8.9.40 ページ=0x00 アドレス=0x47 [リセット=00h]

- 8.9.41 ページ=0x00 アドレス=0x48 [リセット=00h]

- 8.9.42 ページ=0x00 アドレス=0x49 [リセット=00h]

- 8.9.43 ページ=0x00 アドレス=0x4A [リセット=00h]

- 8.9.44 ページ=0x00 アドレス=0x4B [リセット=00h]

- 8.9.45 ページ=0x00 アドレス=0x4F [リセット=00h]

- 8.9.46 ページ=0x00 アドレス=0x50 [リセット=00h]

- 8.9.47 ページ=0x00 アドレス=0x51 [リセット=00h]

- 8.9.48 ページ=0x00 アドレス=0x52 [リセット=00h]

- 8.9.49 ページ=0x00 アドレス=0x53 [リセット=00h]

- 8.9.50 ページ=0x00 アドレス=0x54 [リセット=00h]

- 8.9.51 ページ=0x00 アドレス=0x55 [リセット=00h]

- 8.9.52 ページ=0x00 アドレス=0x56 [リセット=00h]

- 8.9.53 ページ=0x00 アドレス=0x5C [リセット=19h]

- 8.9.54 ページ=0x00 アドレス=0x5D [リセット=80h]

- 8.9.55 ページ=0x00 アドレス=0x60 [リセット=0Dh]

- 8.9.56 ページ=0x00 アドレス=0x63 [リセット=48]

- 8.9.57 ページ=0x00 アドレス=0x65 [リセット=08]

- 8.9.58 ページ=0x00 アドレス=0x67 [リセット=00h]

- 8.9.59 ページ=0x00 アドレス=0x68 [リセット=30h]

- 8.9.60 ページ=0x00 アドレス=0x6A [リセット=12h]

- 8.9.61 ページ=0x00 アドレス=0x6B [リセット=7Bh]

- 8.9.62 ページ=0x00 アドレス=0x6C~0x6E [リセット=00001Ah]

- 8.9.63 ページ=0x00 アドレス=0x6F [リセット=00h]

- 8.9.64 ページ=0x00 アドレス=0x70 [リセット=96h]

- 8.9.65 ページ=0x00 アドレス=0x71 [リセット=02h]

- 8.9.66 ページ=0x00 アドレス=0x73 [リセット=08h]

- 8.9.67 ページ=0x00 アドレス=0x77 [リセット=00h]

- 8.9.68 ページ=0x00 アドレス=0x7A [リセット=60h]

- 8.9.69 ページ=0x00 アドレス=0x7E [リセット=00h]

- 8.9.70 ページ=0x00 アドレス=0x7F [リセット=00h]

- 8.9.71 ページ=0x01 アドレス=0x17 [リセット=D0h]

- 8.9.72 ページ=0x01 アドレス=0x19 [リセット=60h]

- 8.9.73 ページ = 0x01 アドレス = 0x28 [リセット = 00h]

- 8.9.74 ページ = 0x01 アドレス = 0x35 [リセット = 75h]

- 8.9.75 ページ=0x01 アドレス=0x36 [リセット=08h]

- 8.9.76 ページ=0x01 アドレス=0x3D [リセット=00h]

- 8.9.77 ページ=0x01 アドレス=0x3E [リセット=00h]

- 8.9.78 ページ=0x01 アドレス=0x3F [リセット=00h]

- 8.9.79 ページ=0x01 アドレス=0x40 [リセット=00h]

- 8.9.80 ページ=0x01 アドレス=0x41 [リセット=00h]

- 8.9.81 ページ=0x01 アドレス=0x42 [リセット=00h]

- 8.9.82 ページ=0x01 アドレス=0x43 [リセット=00h]

- 8.9.83 ページ=0x01 アドレス=0x44 [リセット=00h]

- 8.9.84 ページ=0x01 アドレス=0x45 [リセット=00h]

- 8.9.85 ページ=0x01 アドレス=0x47 [リセット=AB]

- 8.9.86 ページ=0x01 アドレス=0x4C [リセット=00h]

- 8.9.87 ページ=0x04 アドレス=0x08~0x0B [リセット=034A516Ch]

- 8.9.88 ページ=0x04 アドレス=0x10~0x13 [リセット=34000000h]

- 8.9.89 ページ=0x04 アドレス=0x14~0x17 [リセット=14000000h]

- 8.9.90 ページ=0x04 アドレス=0x18~0x1B [リセット=0D333333h]

- 8.9.91 ページ=0x04 アドレス=0x1C~0x1F [リセット=10000000h]

- 8.9.92 ページ=0x04 アドレス=0x20~0x23 [リセット=0B999999h]

- 8.9.93 ページ=0x04 アドレス=0x24~0x27 [リセット=0ACCCCCDh]

- 8.9.94 ページ=0x04 アドレス=0x40~0x43 [リセット=721482C0h]

- 8.9.95 ページ=0x04 アドレス=0x44~0x47 [リセット=00000258h]

- 8.9.96 ページ=0x04 アドレス=0x48~0x4B [リセット=40BDB7C0h]

- 8.9.97 ページ=0x04 アドレス=0x4C~0x4F [リセット=3982607Fh]

- 8.9.98 ページ=0x04 アドレス=0x50~0x53 [リセット=2D6A866Fh]

- 8.9.99 ページ=0x04 アドレス=0x54~0x57 [リセット=7C5E4E02h]

- 8.9.100 ページ=0x05 アドレス=0x14~0x17 [リセット=6CCCCCCCh]

- 8.9.101 ページ=0x05 アドレス=0x1C~0x1F [リセット=4CCCCCCh]

- 8.9.102 ページ=0x05 アドレス=0x20~0x23 [リセット=00000180h]

- 8.9.103 ページ=0x05 アドレス=0x24~0x27 [リセット=00000000h]

- 8.9.104 ページ=0x05 アドレス=0x28~0x2B [リセット=79999999h]

- 8.9.105 ページ=0x05 アドレス=0x2C~0x2F [リセット=0538EF34h]

- 8.9.106 ページ=0x05 アドレス=0x30~0x33 [リセット=40000000h]

- 8.9.107 ページ=0x05 アドレス=0x34~0x37 [リセット=65AC8C2Fh]

- 8.9.108 ページ=0x05 アドレス=0x38~0x3B [リセット=50C335D3h]

- 8.9.109 ページ=0x05 アドレス=0x3C~0x3F [リセット=4026E73Ch]

- 8.9.110 ページ=0x05 アドレス=0x40~0x43 [リセット=32F52CFEh]

- 8.9.111 ページ=0x05 アドレス=0x44~0x47 [リセット=287A26C4h]

- 8.9.112 ページ=0x05 アドレス=0x48~0x4B [リセット=2026F30Fh]

- 8.9.113 ページ=0x05 アドレス=0x4C~0x4F [リセット=198A1357h]

- 8.9.114 ページ=0x05 アドレス=0x50~0x53 [リセット=144960C5h]

- 8.9.115 ページ=0x05 アドレス=0x54~0x57 [リセット=101D3F2Dh]

- 8.9.116 ページ=0x05 アドレス=0x58~0x5B [リセット=0CCCCCCCh]

- 8.9.117 ページ=0x05 アドレス=0x5C~0x5F [リセット=0A2AADD1h]

- 8.9.118 ページ=0x05 アドレス=0x60~0x63 [リセット=08138561h]

- 8.9.119 ページ=0x05 アドレス=0x64~0x67 [リセット=081385615h]

- 8.9.120 ページ=0x05 アドレス=0x68~0x6B [リセット=08138561h]

- 8.9.121 ページ=0x05 アドレス=0x6C~0x6F [リセット=08138561h]

- 8.9.122 ページ=0x05 アドレス=0x70~0x73 [リセット=08138561h]

- 8.9.123 ページ=0x05 アドレス=0x74~0x77 [リセット=000000BFh]

- 8.9.124 ページ=0x05 アドレス=0x78~0x7B [リセット=0000000Eh]

- 8.9.125 ページ=0x05 アドレス=0x7C~0x7F [リセット=66676869h]

- 8.9.126 ページ=0x06 アドレス=0x08~0x0B [リセット=00000000h]

- 8.9.127 ページ=0x06 アドレス=0x0C~0x0F [リセット=80800000h]

- 8.9.128 ページ=0x06 アドレス=0x10~0x13 [リセット=C0C00000h]

- 8.9.129 ページ=0x06 アドレス=0x14~0x17 [リセット=E0E00000h]

- 8.9.130 ページ=0x06 アドレス=0x18~0x1B [リセット=F0F00000h]

- 8.9.131 ページ=0x06 アドレス=0x1C~0x1F [リセット=F8F80000h]

- 8.9.132 ページ=0x06 アドレス=0x20~0x23 [リセット=FCFC0000h]

- 8.9.133 ページ=0x06 アドレス=0x24~0x27 [リセット=FCFC0000h]

- 8.9.134 ページ=0x06 アドレス=0x28~0x2B [リセット=FCFC0000h]

- 8.9.135 ページ=0x06 アドレス=0x2C~0x2F [リセット=00000000h]

- 8.9.136 ページ=0x06 アドレス=0x30~0x33 [リセット=80000000h]

- 8.9.137 ページ=0x06 アドレス=0x34~0x37 [リセット=C0000000h]

- 8.9.138 ページ=0x06 アドレス=0x38~0x3B [リセット=E0000000h]

- 8.9.139 ページ=0x06 アドレス=0x3C~0x3F [リセット=F0000000h]

- 8.9.140 ページ=0x06 アドレス=0x40~0x43 [リセット=F8000000h]

- 8.9.141 ページ=0x06 アドレス=0x44~0x47 [リセット=FC000000h]

- 8.9.142 ページ=0x06 アドレス=0x48~0x4B [リセット=FE000000h]

- 8.9.143 ページ=0x06 アドレス=0x4C~0x4F [リセット=FF000000h]

- 8.9.144 ページ=0x06 アドレス=0x50~0x53 [リセット=FF800000h]

- 8.9.145 ページ=0x06 アドレス=0x54~0x57 [リセット=FFC00000h]

- 8.9.146 ページ=0x06 アドレス=0x58~0x5B [リセット=FFE00000h]

- 8.9.147 ページ=0x06 アドレス=0x5C~0x5F [リセット=FFF00000h]

- 8.9.148 ページ=0x06 アドレス=0x60~0x63 [リセット=FFF00000h]

- 8.9.149 ページ=0x06 アドレス=0x64~0x67 [リセット=FFF00000h]

- 8.9.150 ページ=0x06 アドレス=0x68~0x6B [リセット=FFF00000h]

- 8.9.151 ページ=0x06 アドレス=0x6C~0x6F [リセット=FFF00000h]

- 8.9.152 ページ=0x08 アドレス=0x18~0x1B [リセット=9C000000h]

- 8.9.153 ページ=0x08 アドレス=0x28~0x2B [リセット=00000000h]

- 8.9.154 ページ=0x0A アドレス=0x48~0x4B [リセット=9C000000h]

- 8.9.155 ページ=0x0A アドレス=0x58~0x5B [リセット=00000000h]

- 8.9.156 ページ=0xFD アドレス=0x3E [リセット=4Dh]

- 8.10 SDOUT の式

- 9 アプリケーションと実装

- 10初期化セットアップ

- 11電源に関する推奨事項

- 12レイアウト

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

8.4.2.4 デジタル・ボリューム制御およびアンプ出力レベル

オーディオ入力からスピーカ端子へのゲインは、アンプ出力レベルとデジタル・ボリューム制御 (DVC) の設定で制御します。

アンプ出力レベルの設定は、AMP_LVL[4:0] レジスタ・ビットを使用してプログラムします。アンプのレベルは、のレジスタに示されています。デジタル・ボリューム制御 (DVC) は、デフォルトで 0dB に設定されています。このレベルは、アンプのアナログ・クリッピングにより必ずしも実現できるとは限らないため、ゲインの伝達にのみ使用してください。

式 (1) で、アンプ出力電圧を計算します:

ここで

- VAMP は、アンプ出力電圧 (dBV) です

- INPUT は、0dBFS を基準とした場合のデジタル入力振幅を表す dB 数です

- ADVC は、デジタル・ボリューム制御の設定を表す dB 数です

- AAMP は、アンプ出力レベルの設定を表す dBV 数です

DVC は DVC_LVL[7:0] レジスタ・ビットの設定によって、0dB~-100dB の間で 0.5dB きざみで構成することができます。C8h より大きい設定は、ミュートと解釈されます。デジタル・ボリューム制御が変更されると、デバイスはの DVC_SLEW[31:0] レジスタ・ビットのステータスに基づいて、ボリュームを新しい設定にランプします。のレジスタの DVC_RMP_RT[1:0] ビットを使用して、ボリュームのランプ制御のイネーブルとディセーブルを切り替えます。

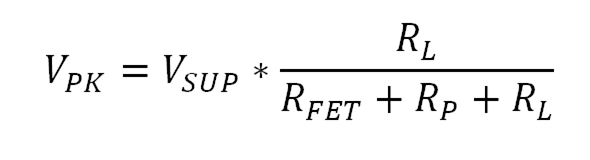

Class-D アンプは、閉ループ・アーキテクチャを搭載しています。出力信号クリッピングのスレッショルドの近似値を求めるには、式 (2) を使用します。

ここで:

- VPK は、クリッピングされていない出力電圧の最大ピーク値 (V) です

- VSUP は、Class-D 出力段の電源です

- RL は、スピーカ負荷 (Ω) です

- RP は、PCB (配線、フィルタ) の寄生抵抗 (Ω) です

- RFET は、電力段の合計抵抗 (HS FET、LS FET、検出抵抗、ボンディング、パッケージング) (Ω) です

PVDDL が Class-D 出力段を供給する場合、RFET の標準値は 0.5Ω です。PVDDH が供給する場合、RFET の標準値は 0.25Ω です。