JAJSFK6H October 2019 – January 2023 TAS5825M

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Programming and Control

- 9.6 Register Maps

-

10Application and Implementation

- 10.1 Application Information

- 10.2 Typical Applications

- 10.3 Power Supply Recommendations

- 10.4 Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RHB|32

サーマルパッド・メカニカル・データ

- RHB|32

発注情報

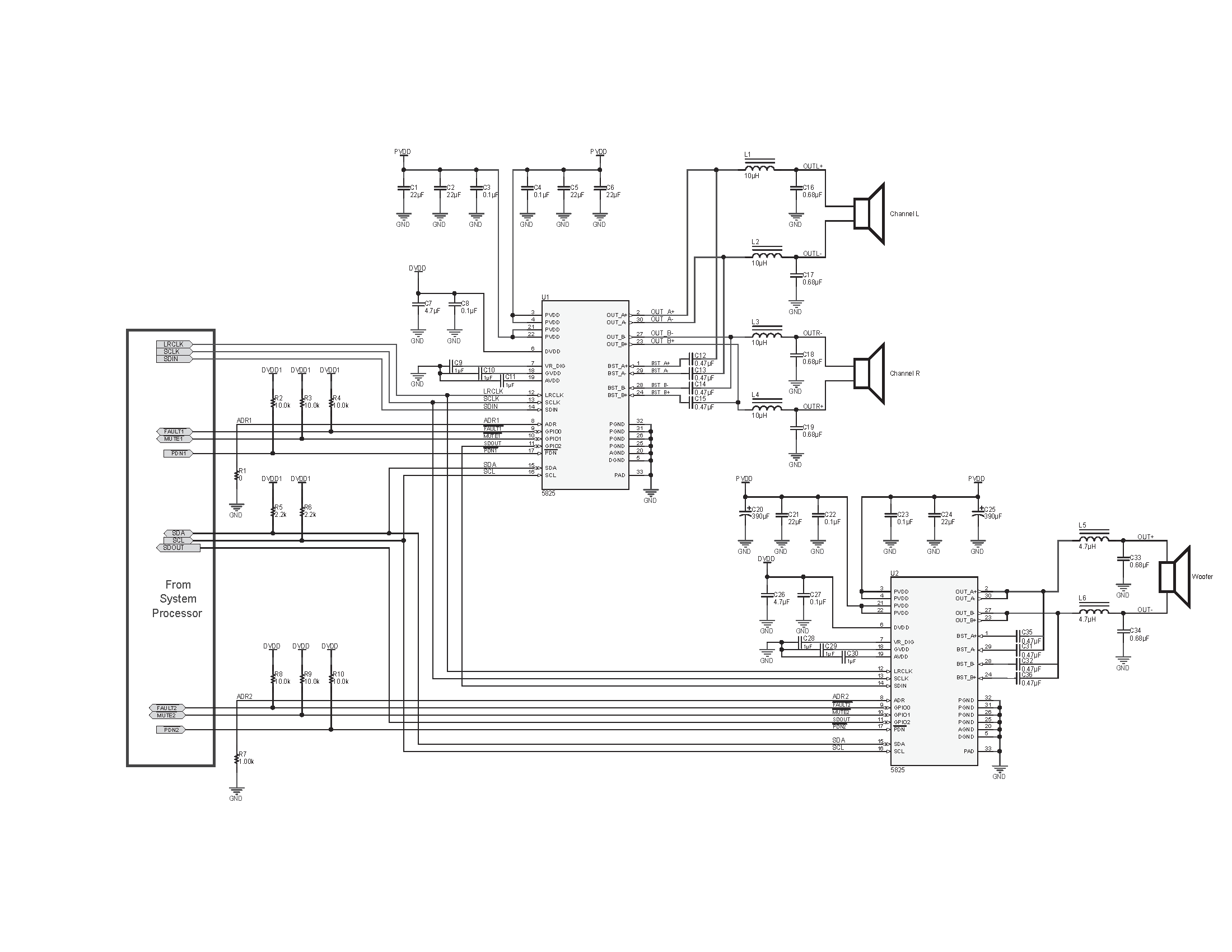

10.2.5 MONO (PBTL) Systems

In MONO mode, TAS5825M can be used as PBTL mode to drive sub-woofer with more output power.

Figure 10-8 Sub-woofer (PBTL) Application

Schematic

Figure 10-8 Sub-woofer (PBTL) Application

SchematicTable 10-3 Supporting Component

Requirements for Sub-woofer (PBTL) Systems

| REFERENCE DESIGNATOR | VALUE | SIZE | DETAILED DESCRIPTION |

|---|---|---|---|

| C1, C2 | 390uF | 10mmx10mm | CAP, AL, 390 μF, 35 V, +/- 20%, 0.08 ohm, SMD |

| C4, C5 | 0.1 µF | 0402 | CAP, CERM, 0.1 µF, 50 V, ±10%, X7R, 0402 |

| C3, C6 | 22 µF | 0805 | CAP, CERM, 22 µF, 35 V, ±20%, JB, 0805 |

| C7 | 4.7 µF | 0603 | CAP, CERM, 4.7 µF, 10 V, ±10%, X5R, 0603 |

| C8 | 0.1 µF | 0603 | CAP, CERM, 0.1 µF, 16 V, ±10%, X7R, 0603 |

| C9,C10,C11 | 1 µF | 0603 | CAP, CERM, 1 µF, 16 V, ±10%, X5R, 0603 |

| C12,C13,C16,C17 | 0.47 µF | 0603 | CAP, CERM, 0.47 µF, 16 V, ±10%, X7R, 0603 |

| C14,C15 | 0.68 µF | 0805 | CAP, CERM, 0.68 µF, 50 V, ±10%, X7R, 0805 |

| L1,L2 | 4.7 µH | Inductor, Shielded, 4.7 μH, 8.7 A | |

| R2 | 1 kΩ | 0402 | RES, 0, 5%, 0.063 W, 0402 |

| R3,R4,R5,R6 | 10 kΩ | 0402 | RES, 10.0 k, 1%, 0.063 W, 0402 |