JAJSO92B November 2012 – March 2022 TFP401A-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 DC Digital I/O Electrical Characteristics

- 6.6 DC Electrical Characteristics

- 6.7 AC Electrical Characteristics

- 6.8 Timing Requirements

- 6.9 Switching Characteristics

- 6.10 Typical Characteristics

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- PZP|100

サーマルパッド・メカニカル・データ

- PZP|100

発注情報

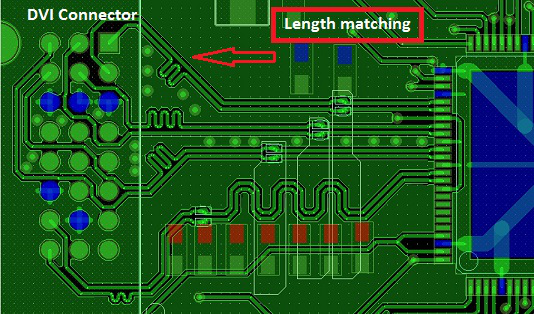

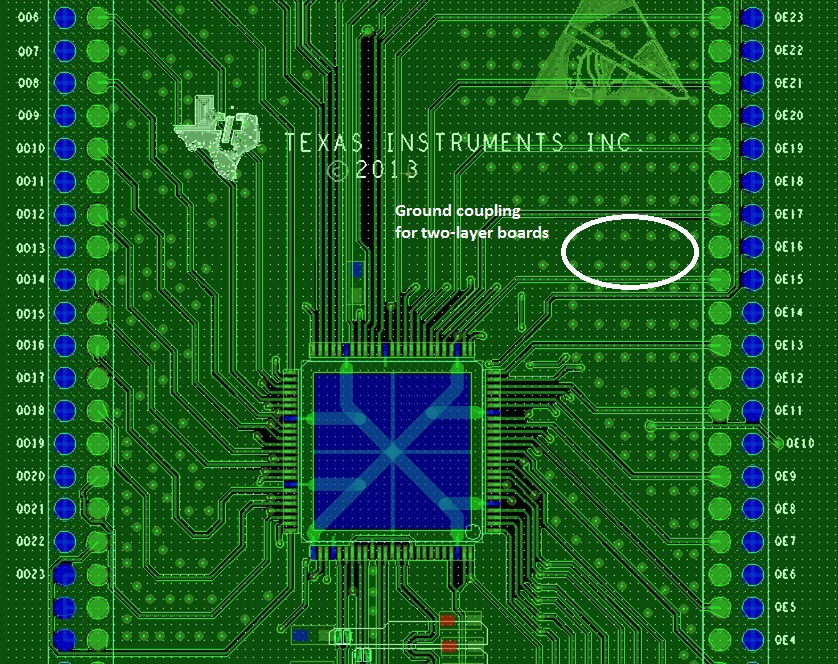

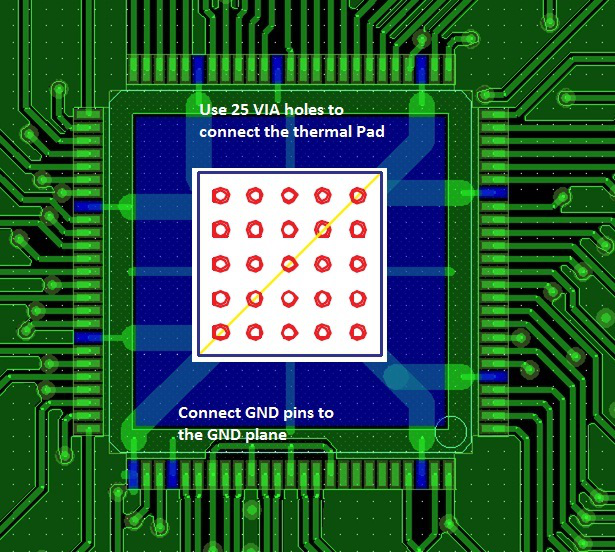

8.3.2 Layout Example

- DVI connector trace matching

Figure 8-8 DVI Connector

Figure 8-8 DVI Connector - Keep data lines as far as possible from each other

Figure 8-9 Data Route

Figure 8-9 Data Route - Connect the thermal pad to ground

Figure 8-10 GND Route

Figure 8-10 GND Route