SLOS776A September 2012 – December 2015 THS789

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- PFD|100

サーマルパッド・メカニカル・データ

- PFD|100

発注情報

10 Layout

10.1 Layout Guidelines

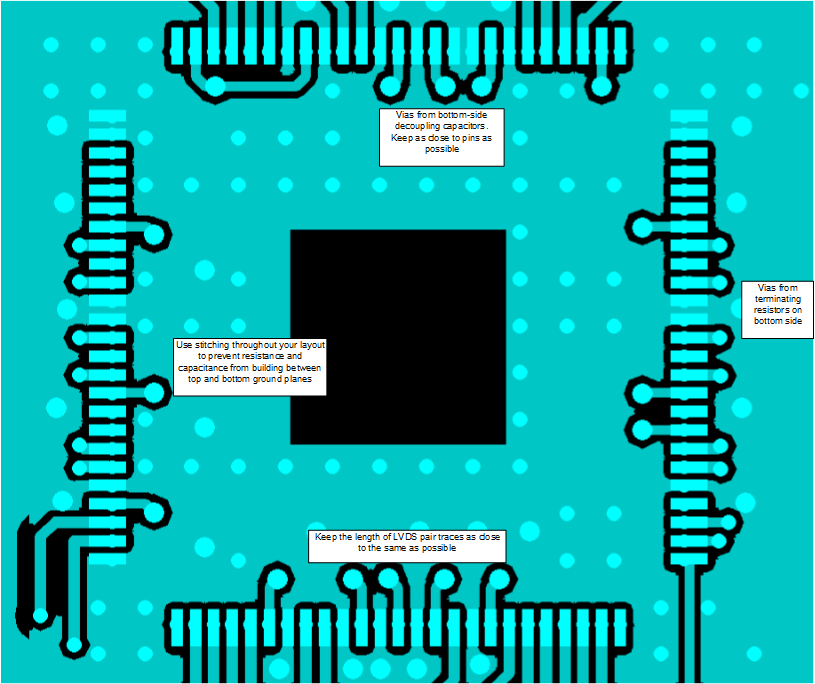

Figure 15 and Figure 16 show typical layout examples for this device.

Use 100-Ω terminating resistors for all LVDS inputs. TI recommends placing all the LVDS input resistors as close as possible to the device (the six pairs of pads are shown in Figure 16 on the left and right sides). The other pads found on the bottom side image are the pairs of decoupling capacitors (0.1 µF and 0.01 µF) for the multiple VDD pins. As noted before, keep the distance between these caps, VDD, and Ground as short as possible.

Keep all differential signals as close as possible to the same length to reduce inaccuracies in timestamp measurement.

10.2 Layout Example

Figure 15. Top (Device-Side) Layer Example

Figure 15. Top (Device-Side) Layer Example

10.3 Thermal Considerations

The TMU package provides a thermally conductive heat slug at the top for connection to an additional heatsink. The TMU can be placed into many different modes for optimization of performance versus power dissipation, and a table has been provided to help determine the power required. The heat sink should be carefully considered in order to keep the TMU temperature within required limits and to promote the best temperature stability. The TMU time measurement drift with temperature is an excellent 0.1 ps/°C. A good heat sink design takes advantage of the low temperature drift of the TMU.