JAJSQA4I march 1994 – march 2021 TL16C550C

PRODUCTION DATA

- 1

- 1 特長

- 2 概要

- 3 Revision History

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions (Low Voltage - 3.3 nominal)

- 5.3 Recommended Operating Conditions (Standard Voltage - 5 V nominal)

- 5.4 Thermal Information

- 5.5 Electrical Characteristics (Low Voltage - 3.3 V nominal)

- 5.6 Electrical Characteristics (Standard Voltage - 5 V nominal)

- 5.7 System Timing Requirements

- 5.8 System Switching Characteristics

- 5.9 Baud Generator Switching Characteristics

- 5.10 Receiver Switching Characteristics

- 5.11 Transmitter Switching Characteristics

- 5.12 Modem Control Switching Characteristics

- 6 Parameter Measurement Information

-

7 Detailed Description

- 7.1 Autoflow Control (see )

- 7.2 Auto-RTS (see )

- 7.3 Auto-CTS (see )

- 7.4 Enabling Autoflow Control and Auto-CTS

- 7.5 Auto-CTS and Auto-RTS Functional Timing

- 7.6 Functional Block Diagram

- 7.7

Principles of Operation

- 7.7.1 Accessible Registers

- 7.7.2 FIFO Control Register (FCR)

- 7.7.3 FIFO Interrupt Mode Operation

- 7.7.4 FIFO Polled Mode Operation

- 7.7.5 Interrupt Enable Register (IER)

- 7.7.6 Interrupt Identification Register (IIR)

- 7.7.7 Line Control Register (LCR)

- 7.7.8 Line Status Register (LSR)

- 7.7.9 Modem Control Register (MCR)

- 7.7.10 Modem Status Register (MSR)

- 7.7.11 Programming Baud Generator

- 7.7.12 Receiver Buffet Register (RBR)

- 7.7.13 Scratch Register

- 7.7.14 Transmitter Holding Register (THR)

- 8 Application Information

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

6 Parameter Measurement Information

Figure 6-1 Baud Generator Timing

Waveforms

Figure 6-1 Baud Generator Timing

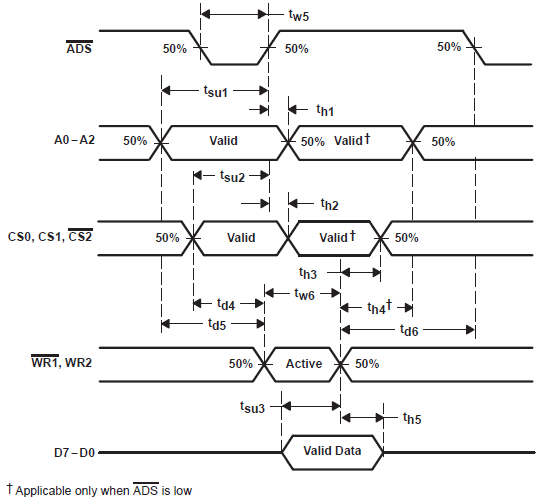

Waveforms Figure 6-2 Write Cycle Timing

Waveforms

Figure 6-2 Write Cycle Timing

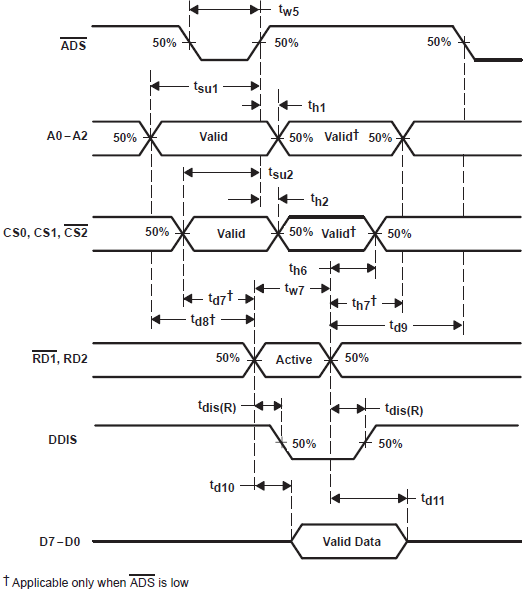

Waveforms Figure 6-3 Read Cycle Timing

Waveforms

Figure 6-3 Read Cycle Timing

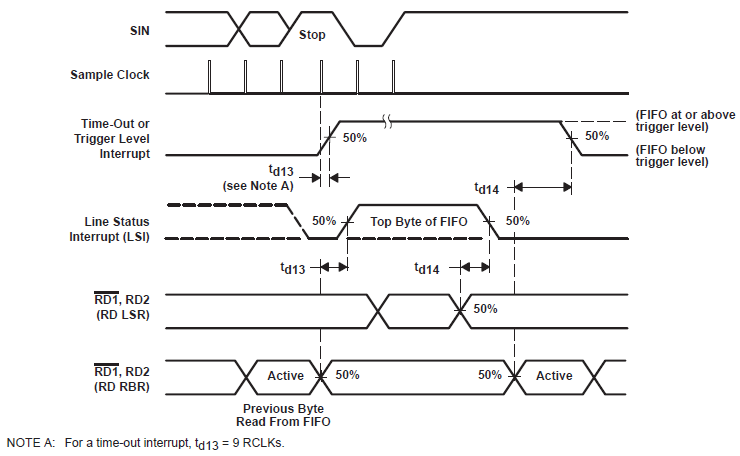

Waveforms Figure 6-4 Receiver Timing

Waveforms

Figure 6-4 Receiver Timing

Waveforms Figure 6-5 Receive FIFO First Byte (Sets

DR Bit) Waveforms

Figure 6-5 Receive FIFO First Byte (Sets

DR Bit) Waveforms Figure 6-6 Receive FIFO Bytes Other Than

the First Byte (DR Internal Bit Already Set) Waveforms

Figure 6-6 Receive FIFO Bytes Other Than

the First Byte (DR Internal Bit Already Set) Waveforms Figure 6-7 Receiver Ready

(RXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0

(Mode 0)

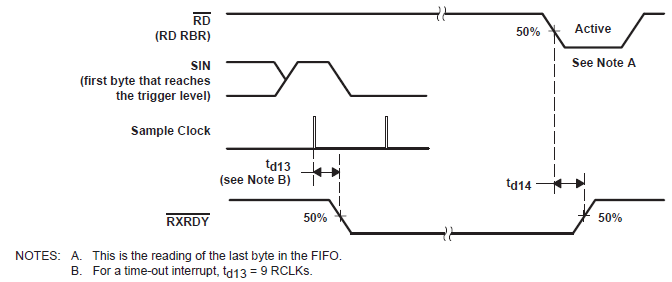

Figure 6-7 Receiver Ready

(RXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0

(Mode 0) Figure 6-8 Receiver Ready (RXRDY)

Waveforms, FCR0 = 1 and FCR3 = 1 (Mode 1)

Figure 6-8 Receiver Ready (RXRDY)

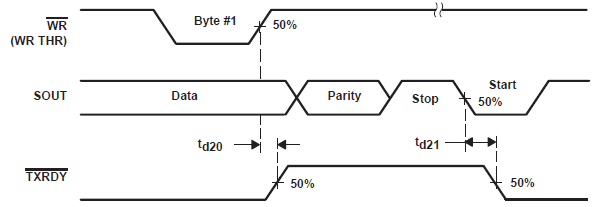

Waveforms, FCR0 = 1 and FCR3 = 1 (Mode 1) Figure 6-9 Transmitter Timing

Waveforms

Figure 6-9 Transmitter Timing

Waveforms Figure 6-10 Transmitter Ready

(TXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0

(Mode 0)

Figure 6-10 Transmitter Ready

(TXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0

(Mode 0) Figure 6-11 Transmitter Ready

(TXRDY) Waveforms, FCR0 = 1 and FCR3 = 1 (Mode

1)

Figure 6-11 Transmitter Ready

(TXRDY) Waveforms, FCR0 = 1 and FCR3 = 1 (Mode

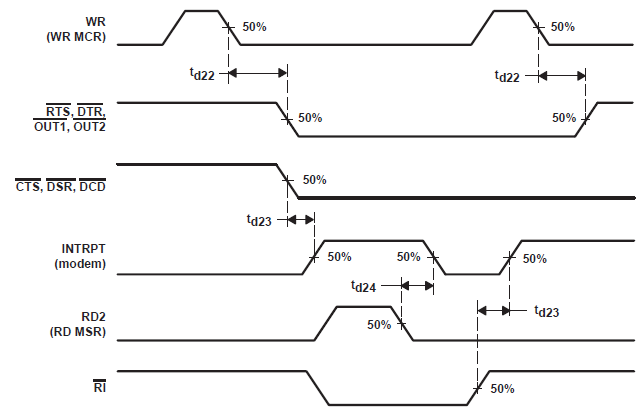

1) Figure 6-12 Modem Control Timing

Waveforms

Figure 6-12 Modem Control Timing

Waveforms Figure 6-13 CTS and

SOUT Autoflow Control Timing (Start and Stop) Waveforms

Figure 6-13 CTS and

SOUT Autoflow Control Timing (Start and Stop) Waveforms Figure 6-14 Auto-RTS

Timing for RCV Threshold of 1, 4, or 8 Waveforms

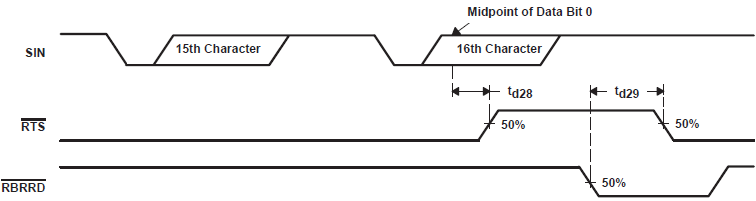

Figure 6-14 Auto-RTS

Timing for RCV Threshold of 1, 4, or 8 Waveforms Figure 6-15 Auto-RTS

Timing for RCV Threshold of 14 Waveforms

Figure 6-15 Auto-RTS

Timing for RCV Threshold of 14 Waveforms