-

TLV320AIC3212 Ultra-Low Power Stereo Audio Codec With Receiver Driver, DirectPath Headphone, and Stereo Class-D Speaker Amplifier

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information

- 8.5 Electrical Characteristics, SAR ADC

- 8.6 Electrical Characteristics, ADC

- 8.7 Electrical Characteristics, Bypass Outputs

- 8.8 Electrical Characteristics, Microphone Interface

- 8.9 Electrical Characteristics, Audio DAC Outputs

- 8.10 Electrical Characteristics, Class-D Outputs

- 8.11 Electrical Characteristics, Miscellaneous

- 8.12 Electrical Characteristics, Logic Levels

- 8.13 Audio Data Serial Interface Timing (I2S): I2S/LJF/RJF Timing in Master Mode

- 8.14 Audio Data Serial Interface Timing (I2S): I2S/LJF/RJF Timing in Slave Mode

- 8.15 Typical DSP Timing: DSP/Mono PCM Timing in Master Mode

- 8.16 Typical DSP Timing: DSP/Mono PCM Timing in Slave Mode

- 8.17 I2C Interface Timing

- 8.18 SPI Timing

- 8.19 Typical Characteristics

- 9 Parameter Measurement Information

-

10Detailed Description

- 10.1 Overview

- 10.2 Functional Block Diagram

- 10.3

Feature Description

- 10.3.1 Device Connections

- 10.3.2

Analog Audio I/O

- 10.3.2.1 Analog Low Power Bypass

- 10.3.2.2

Headphone Outputs

- 10.3.2.2.1 Using the Headphone Amplifier

- 10.3.2.2.2 Ground-Centered Headphone Amplifier Configuration

- 10.3.2.2.3 Stereo Unipolar Configuration

- 10.3.2.2.4 Mono Differential DAC to Mono Differential Headphone Output

- 10.3.2.3 Stereo Line Outputs

- 10.3.2.4 Differential Receiver Output

- 10.3.2.5 Stereo Class-D Speaker Outputs

- 10.3.3 ADC / Digital Microphone Interface

- 10.3.4 DAC

- 10.3.5 Device Power Consumption

- 10.3.6 Powertune

- 10.3.7 Clock Generation and PLL

- 10.3.8 Interfaces

- 10.3.9 Device Special Functions

- 10.4 Device Functional Modes

- 10.5 Register Maps

- 11Application and Implementation

- 12Power Supply Recommendations

- 13Layout

- 14Device and Documentation Support

- 15Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

TLV320AIC3212 Ultra-Low Power Stereo Audio Codec With Receiver Driver, DirectPath Headphone, and Stereo Class-D Speaker Amplifier

1 Features

- Stereo Audio DAC With 101=dB SNR

- 2.7-mW Stereo 48-kHz DAC Playback

- Stereo Audio ADC With 93-dB SNR

- 5.6-mW Stereo 48-kHz ADC Record

- 8 kHz to 192 kHz Playback and Record

- 30-mW DirectPath™ Headphone Driver Eliminates Large Output DC-Blocking Capacitors

- 128-mW Differential Receiver Output Driver

- Stereo Class-D Speaker Drivers

- 1.7 W (8 Ω, 5.5 V, 10% THDN)

- 1.4 W (8 Ω, 5.5 V, 1% THDN)

- Stereo Line Outputs

- PowerTune™ - Adjusts Power vs SNR

- Extensive Signal Processing Options

- Eight Single-Ended or 4 Fully-Differential Analog Inputs

- Stereo Digital and Analog Microphone Inputs

- Low Power Analog Bypass Mode

- Programmable PLL, Plus Low-Frequency Clocking

- Programmable 12-Bit SAR ADC

- SPI and I2C Control Interfaces

- Three Independent Digital Audio Serial Interfaces

- 4.81 mm × 4.81 mm × 0.625 mm 81-Ball WCSP (YZF) Package

2 Applications

- Mobile Handsets

- Tablets and eBooks

- Portable Navigation Devices (PND)

- Portable Media Players (PMP)

- Portable Gaming Systems

- Portable Computing

3 Description

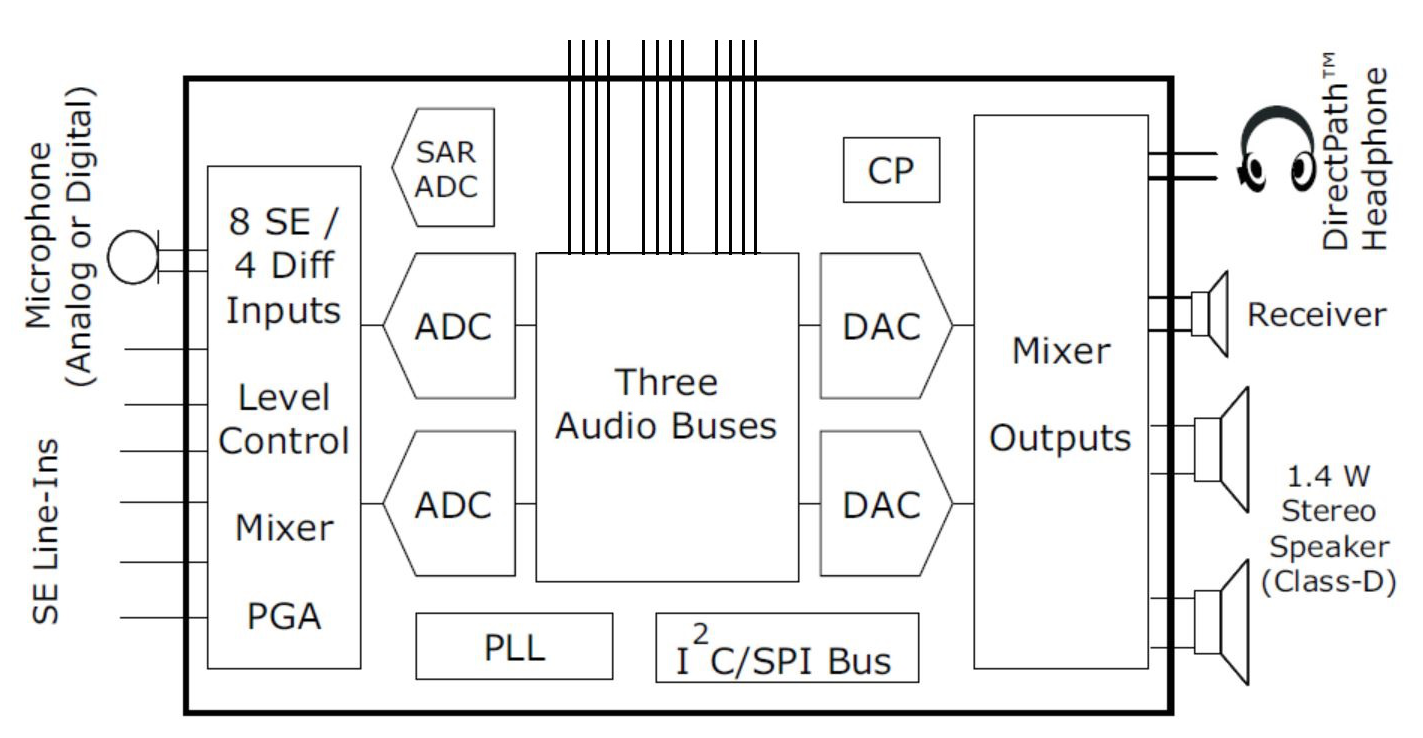

The TLV320AIC3212 (also referred to as the AIC3212) device is a flexible, highly-integrated, low-power, low-voltage stereo audio codec. The AIC3212 features digital microphone inputs and programmable outputs, PowerTune capabilities, selectable audio-processing blocks, predefined and parameterizable signal processing blocks, integrated PLL, and flexible audio interfaces. Extensive register-based control of power, input and output channel configuration, gains, effects, pin-multiplexing and clocks are included, allowing the device to be precisely targeted to its application.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TLV320AIC3212 | DSBGA (81) | 4.81 mm × 4.81 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Simplified Block Diagram

4 Revision History

Changes from * Revision (March 2012) to A Revision

- Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section Go

5 Description (continued)

Combined with the advanced PowerTune technology, the device can execute operations from 8-kHz mono voice playback to stereo 192-kHz DAC playback, making it ideal for portable battery-powered audio and telephony applications.

The record path of the TLV320AIC3212 covers operations from 8-kHz mono to 192-kHz stereo recording, and contains programmable input channel configurations which cover single-ended and differential setups, as well as floating or mixing input signals. It also provides a digitally-controlled stereo microphone preamplifier and integrated microphone bias. One application of the digital signal processing blocks is removable of audible noise that may be introduced by mechanical coupling, for example, optical zooming in a digital camera. The record path can also be configured as a stereo digital microphone Pulse Density Modulation (PDM) interface typically used at 64 Fs or 128 Fs.

The playback path offers signal processing blocks for filtering and effects; headphone, line, receiver, and Class-D speaker outputs; flexible mixing of DAC; and analog input signals as well as programmable volume controls. The playback path contains two high-power DirectPath headphone output drivers which eliminate the need for ac coupling capacitors. A built in charge pump generates the negative supply for the ground centered headphone drivers. These headphone output drivers can be configured in multiple ways, including stereo, and mono BTL. In addition, playback audio can be routed to integrated stereo Class-D speaker drivers or a differential receiver amplifier.

The integrated PowerTune technology allows the device to be tuned to just the right power-performance trade-off. Mobile applications frequently have multiple use cases requiring very low-power operation while being used in a mobile environment. When used in a docked environment power consumption typically is less of a concern while lowest possible noise is important. With PowerTune the TLV320AIC3212 can address both cases.

The required internal clock of the TLV320AIC3212 can be derived from multiple sources, including the MCLK1 pin, the MCLK2 pin, the BCLK1 pin, the BCLK2 pin, several general purpose I/O pins or the output of the internal PLL, where the input to the PLL again can be derived from similar pins. Although using the internal fractional PLL ensures the availability of a suitable clock signal, TI does not recommend this for the lowest power settings. The PLL is highly programmable and can accept available input clocks in the range of 512 kHz to 50 MHz. To enable even lower clock frequencies, an integrated low-frequency clock multiplier can also be used as an input to the PLL.

The TLV320AIC3212 has a 12-bit SAR ADC converter that supports system voltage measurements. These system voltage measurements can be sourced from three dedicated analog inputs (IN1L/AUX1, IN1R/AUX2, or VBAT pins), or, alternatively, an on-chip temperature sensor that can be read by the SAR ADC.

The TLV320AIC3212 also features three full Digital Audio Serial Interfaces, each supporting I2S, DSP/TDM, RJF, LJF, and mono PCM formats. This enables the digital playback (DAC) and record (ADC) paths to select from three independent digital audio buses or chips.

The device is available in the 4.81 mm × 4.81 mm × 0.625 mm 81-Ball WCSP (YZF) package.

6 Device Comparison Table

| PARAMETRICS | TLV320AIC3212 | TLV320AIC3262 | TLV320AIC3268 | TLV320AIC3204 | TLV320AIC3254 |

|---|---|---|---|---|---|

| DACs (number) | 2 | 2 | 2 | 2 | 2 |

| ADCs (number) | 2 | 2 | 2 | 2 | 2 |

| Number of Inputs / Number of Outputs | 8/7 | 8/7 | 8/7 | 6/4 | 6/4 |

| Resolution (Bits) | 16, 20, 24, 32 | 16, 20, 24, 32 | 16, 20, 24, 32 | 16, 20, 24, 32 | 16, 20, 24, 32 |

| Control Interface | I2C, SPI | I2C, SPI | I2C, SPI | I2C, SPI | I2C, SPI |

| Digital Audio Interface | I2S, TDM, DSP, L&R, PCM | I2S, TDM, DSP, L&R, PCM | I2S, TDM, DSP, L&R, PCM | I2S, TDM, DSP, L&R | I2S, TDM, DSP, L&R |

| Number of of Digital Audio Interfaces | 3 | 3 | 3 | 1 | 1 |

| Speaker Amplifier Type | Class-D | Class-D | Class-D | — | — |

| Configurable miniDSP | No | Yes | Yes | No | Yes |

| Headphone Driver | Yes | Yes | Yes | Yes | Yes |

7 Pin Configuration and Functions

Pin Functions

| PIN | TYPE | DESCRIPTION | ||

|---|---|---|---|---|

| NO. | NAME | |||

| A1 | AVDD3_33 | P | 3.3-V Power Supply for Micbias | |

| A2 | RECVSS | P | Receiver Driver Ground | |

| A3 | RECVDD_33 | P | 3.3-V Power Supply for Receiver Driver | |

| A4 | HPR | O | Right Headphone Output | |

| A5 | VNEG | I/O | Charge Pump Negative Supply | |

| A6 | CPFCM | I/O | Charge Pump Flying Capacitor M terminal | |

| A7 | CPVDD_18 | P | Power Supply Input for Charge Pump | |

| A8 | AVSS4 | P | Analog Ground for Class-D | |

| A9 | SPKLP | O | Left Channel P side Class-D Output | |

| B1 | MICDET | I/O | Headset Detection Pin | |

| B2 | RECP | O | Receiver Driver P side Output | |

| B3 | RECM | O | Receiver Driver M side Output | |

| B4 | HVDD_18 | P | Headphone Amp Power Supply | |

| B5 | HPL | O | Left Headphone Output | |

| B6 | CPVSS | P | Charge Pump Ground | |

| B7 | CPFCP | I/O | Charge Pump Flying Capacitor P Terminal | |

| B8 | SLVDD | P | Left Channel Class-D Output Stage Power Supply | |

| B9 | SLVSS | P | Left Channel Class-D Output Stage Ground | |

| C1 | IN4L | I | Analog Input 4 Left | |

| C2 | AVDD1_18 | P | 1.8-V Analog Power Supply | |

| C3 | MICBIAS_EXT | O | Output Bias Voltage for Headset Microphone. | |

| C4 | MICBIAS | O | Output Bias Voltage for Microphone to be used for on-board Microphones | |

| C5 | AVDD2_18 | P | 1.8-V Analog Power Supply | |

| C6 | LOL | O | Left Line Output | |

| C7 | AVDD4_18 | P | 1.8-V Analog Power Supply for Class-D | |

| C8 | SPKLM | O | Left Channel M side Class-D Output | |

| C9 | SPKRM | O | Right Channel M side Class-D Output | |

| D1 | VREF_AUDIO | O | Analog Reference Filter Output | |

| D2 | VREF_SAR | I/O | SAR ADC Voltage Reference Input or Internal SAR ADC Voltage Reference Bypass Capacitor Pin | |

| D3 | IN1L/AUX1 | I | Analog Input 1 Left, Auxiliary 1 Input to SAR ADC (Special Function: Left Channel High Impedance Input for Capacitive Sensor Measurement) |

|

| D4 | IN1R/AUX2 | I | Analog Input 1 Right, Auxiliary 2 Input to SAR ADC (Special Function: Right Channel High Impedance Input for Capacitive Sensor Measurement) |

|

| D5 | IN4R | I | Analog Input 4 Right | |

| D6 | HPVSS_SENSE | I | Headphone Ground Sense Terminal | |

| D7 | LOR | O | Right Line Output | |

| D8 | SRVSS | P | Right Channel Class-D Output Stage Ground | |

| D9 | SRVDD | P | Right Channel Class-D Output Stage Power Supply | |

| E1 | IN3R | I | Analog Input 3 Right | |

| E2 | IN3L | I | Analog Input 3 Left | |

| E3 | AVSS | P | Analog Ground | |

| E4 | AVSS1 | P | Analog Ground | |

| E5 | AVSS3 | P | Analog Ground | |

| E6 | AVSS2 | P | Analog Ground | |

| E7 | DVSS | P | Digital Ground | |

| E8 | SPK_V | P | Class-D Output Stage Power Supply (Connect to SRVDD through a Resistor) | |

| E9 | SPKRP | O | Right Channel P side Class-D Output | |

| F1 | IN2L | I | Analog Input 2 Left | |

| F2 | IN2R | I | Analog Input 2 Right | |

| F3 | AVDD_18 | P | 1.8-V Analog Power Supply | |

| F4 | DVSS | P | Digital Ground | |

| F5 | GPI3 | I | Multi Function Digital Input 3 | |

| Primary: (SPI_SELECT = 1) | ||||

| ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| Secondary: (SPI_SELECT = 0) | ||||

| I2C Address Bit 1 (I2C_ADDR0, LSB) | ||||

| F6 | GPI2 | I | Multi Function Digital Input 2 | |

| Primary: | ||||

| General Purpose Input | ||||

| Secondary: | ||||

| Audio Serial Data Bus 1 Data Input Digital Microphone Data Input General Clock Input Low-Frequency Clock Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| F7 | GPI4 | I | Multi Function Digital Input 4 | |

| Primary: (SPI_SELECT = 1) | ||||

| ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| Secondary: (SPI_SELECT = 0) | ||||

| I2C Address Bit 2 (I2C_ADDR1, MSB) | ||||

| F8 | IOVSS | P | Digital I/O Buffer Ground | |

| F9 | VBAT | I | Battery Monitor Voltage Input | |

| G1 | MCLK1 | I | Master Clock Input 1 | |

| G2 | BCLK2 | I/O | Primary: | |

| Audio Serial Data Bus 2 Bit Clock | ||||

| Secondary: | ||||

| General Purpose Input General Purpose Output General CLKOUT Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output General Clock Input Low-Frequency Clock Input |

||||

| G3 | DIN2 | I | Primary: | |

| Audio Serial Data Bus 2 Data Input | ||||

| Secondary: | ||||

| Digital Microphone Data Input General Purpose Input Low-Frequency Clock Input |

||||

| G4 | WCLK2 | I/O | Primary: | |

| Audio Serial Data Bus 2 Word Clock | ||||

| Secondary: | ||||

| General Purpose Input General Purpose Output CLKOUT Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output Low-Frequency Clock Input |

||||

| G5 | WCLK3 | I/O | Primary: | |

| Audio Serial Data Bus 3 Word Clock | ||||

| Secondary: | ||||

| General Purpose Output General Purpose Input Low-Frequency Clock Input |

||||

| G6 | DIN3 | I | Audio Serial Data Bus 3 Data Input | |

| G7 | SPI_SELECT | I | Control Interface Select SPI_SELECT = 1: SPI Interface selected SPI_SELECT = 0: I2C Interface selected |

|

| G8 | RESET | I | Active Low Reset | |

| G9 | MCLK2 | I | Master Clock 2 | |

| Primary: | ||||

| Clock Input | ||||

| Secondary: | ||||

| Digital Microphone Data Input Low-Frequency Clock Input |

||||

| H1 | BCLK1 | I/O | Primary: | |

| Audio Serial Data Bus 1 Bit Clock | ||||

| Secondary: | ||||

| General Clock Input | ||||

| H2 | DOUT1 | O | Primary: | |

| Audio Serial Data Bus 1 Data Output | ||||

| Secondary: | ||||

| General Purpose Output CLKOUT Output SAR ADC Interrupt INT1 Output INT2 Output |

||||

| H3 | IOVDD | P | Digital I/O Buffer Supply | |

| H4 | SCL | I/O | I2C Interface Serial Clock (SPI_SELECT = 0) SPI interface mode chip-select signal (SPI_SELECT = 1) |

|

| H5 | SDA | I/O | I2C interface mode serial data input (SPI_SELECT = 0) SPI interface mode serial data input (SPI_SELECT = 1) |

|

| H6 | GPO1 | O | Multifunction Digital Output 1 | |

| Primary: (SPI_SELECT = 1) | ||||

| Serial Data Output | ||||

| Secondary: (SPI_SELECT = 0) | ||||

| General Purpose Output CLKOUT Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output |

||||

| H7 | BCLK3 | I/O | Primary: | |

| Audio Serial Data Bus 3 Bit Clock | ||||

| Secondary: | ||||

| General Purpose Input General Purpose Output Low-Frequency Clock Input |

||||

| H8 | GPIO2 | I/O | Multi Function Digital IO 2 | |

| Outputs: | ||||

| General Purpose Output ADC MOD Clock Output For Digital Microphone CLKOUT Output SAR ADC Interrupt INT1 Output INT2 Output Audio Serial Data Bus 1 Bit Clock Output ADC Word Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| Inputs: | ||||

| General Purpose Input Digital Microphone Data Input Audio Serial Data Bus 1 Bit Clock Input General Clock Input Low-Frequency Clock Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| H9 | IOVDD | P | Digital I/O Buffer Supply | |

| J1 | DIN1 | I | Primary: | |

| Audio Serial Data Bus 1 Data Input | ||||

| Secondary: | ||||

| General Clock Input Digital Microphone Data Input |

||||

| J2 | WCLK1 | I/O | Primary: | |

| Audio Serial Data Bus 1 Word Clock | ||||

| Secondary: | ||||

| Low-Frequency Clock Input General CLKOUT Output |

||||

| J3 | DVDD | P | 1.8V Digital Power Supply | |

| J4 | IOVSS | P | Digital I/O Buffer Ground | |

| J5 | GPI1 | I | Multifunction Digital Input 1 | |

| Primary: (SPI_SELECT = 1) | ||||

| SPI Serial Clock | ||||

| Secondary: (SPI_SELECT = 0) | ||||

| Digital Microphone Data Input General Clock Input Low-Frequency Clock Input General Purpose Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| J6 | DOUT2 | O | Primary: | |

| Audio Serial Data Bus 2 Data Output | ||||

| Secondary: | ||||

| General Purpose Output ADC MOD Clock Output SAR ADC Interrupt INT1 Output INT2 Output |

||||

| J7 | DOUT3 | O | Primary: | |

| Audio Serial Data Bus 3 Data Output | ||||

| Secondary: | ||||

| General Purpose Output Audio Serial Data Bus 1 Word Clock Output |

||||

| J8 | GPIO1 | I/O | Multi Function Digital IO 1 | |

| Outputs: | ||||

| General Purpose Output ADC MOD Clock Output CLKOUT Output SAR ADC Interrupt INT1 Output INT2 Output Audio Serial Data Bus 1 Word Clock Output ADC Word Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Output for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| Inputs: | ||||

| General Purpose Input Digital Microphone Data Input Audio Serial Data Bus 1 Word Clock Input General Clock Input Low-Frequency Clock Input ADC Word Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) ADC Bit Clock Input for Audio Serial Data Bus 1, 2, or 3 (Six-Wire Audio Interface) |

||||

| J9 | DVDD | P | 1.8V Digital Power Supply | |