JAJSM93B june 2022 – may 2023 TPS1641

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Enable and Shutdown Input (EN/SHDN)

- 8.3.2 Overvoltage Protection (OVP)

- 8.3.3 Output Slew Rate and Inrush Current Control (dVdt)

- 8.3.4 Active Current Limiting (ILIM) With the TPS16412, TPS16413, TPS16416, and TPS16417

- 8.3.5 Active Power Limiting (PLIM) With the TPS16410, TPS16411, TPS16414, and TPS16415

- 8.3.6 Overcurrent Protection (IOCP) and Blanking Time (IDLY or PDLY) for Transient Loads

- 8.3.7 Fast-Trip and Short-Circuit Protection

- 8.3.8 Analog Load Current Monitor (IMON) on the IOCP Pin

- 8.3.9 IN to OUT Short Detection (TPS16410, TPS16411, TPS16412, and TPS16413)

- 8.3.10 Thermal Shutdown and Overtemperature Protection

- 8.3.11 Fault Response and Indication (FLT)

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DRC|10

サーマルパッド・メカニカル・データ

- DRC|10

発注情報

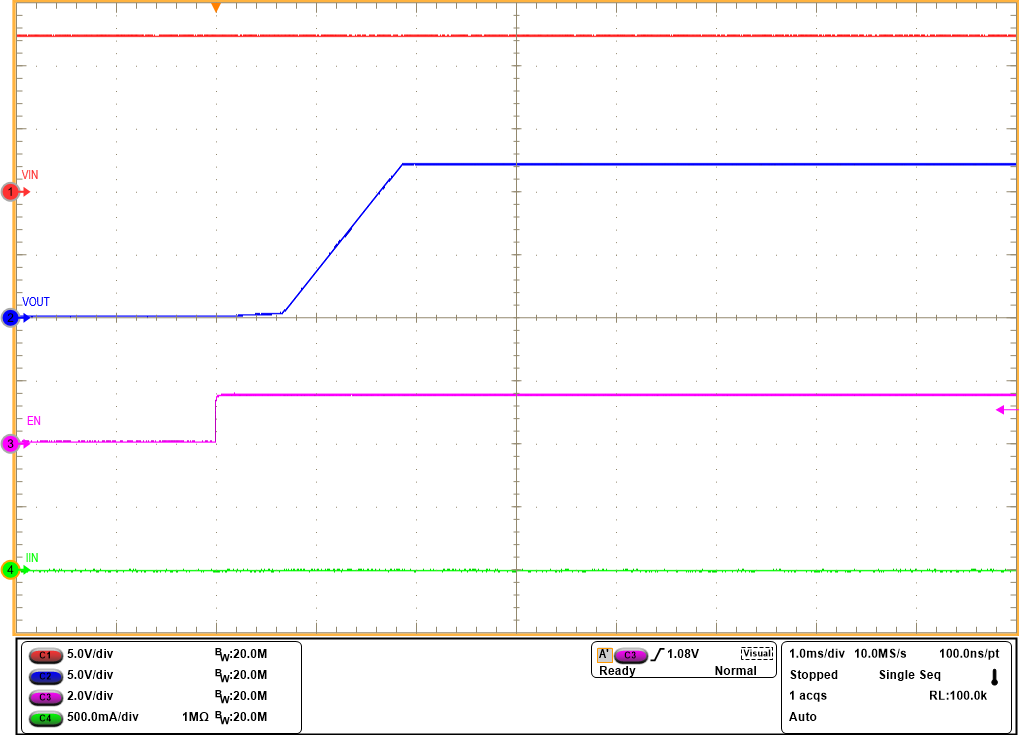

8.3.1 Enable and Shutdown Input (EN/SHDN)

The TPS1641x devices include a enable and shutdown input. Keeping EN/SHDN low for a duration more than tLow_SHDN brings the device into low power shutdown mode, internal blocks of device are turned off, and the quiescent current of the device is reduced to IQSD from Vcc supply.

While keeping EN/SHDN low for a duration less than tLow_SHDN, the device turns off the internal FET only and FET can be turned back on quickly. The device turns off the internal FET with a delay of tEN_OFF_dly as the enable pin is brought low. The internal FET can be enabled quickly with a delay of tEN_ON_dly when the device is not in shutdown. See the SLVSGF4-TPS1641-TPS1641x:40V、1.8A 電力および電流制限 eFuse、入力と出力の間の短絡検出機能付き TPS1641x 40V、1.8A 電力および電流制限 eFuse、入力と出力の間の短絡検出機能付き TPS1641x 40V、1.8A 電力および電流制限 eFuse、入力と出力の間の短絡検出機能付き 特長 特長 アプリケーション アプリケーション 概要 概要 Table of Contents Table of Contents Revision History Revision History Revision History Revision History Device Comparison Table Device Comparison Table Pin Configuration and Functions Pin Configuration and Functions Specifications Specifications Absolute Maximum Ratings Absolute Maximum Ratings ESD Ratings ESD Ratings Recommended Operating Conditions Recommended Operating Conditions Thermal Information Thermal Information Electrical Characteristics Electrical Characteristics Timing Requirements Timing Requirements Typical Characteristics Typical Characteristics Detailed Description Detailed Description Overview Overview Functional Block Diagram Functional Block Diagram Feature Description Feature Description Enable and Shutdown Input (EN/SHDN) Enable and Shutdown Input (EN/SHDN) Overvoltage Protection (OVP) Overvoltage Protection (OVP) Output Slew Rate and Inrush Current Control (dVdt) Output Slew Rate and Inrush Current Control (dVdt) Active Current Limiting (ILIM) With the TPS16412, TPS16413, TPS16416, and TPS16417 Active Current Limiting (ILIM) With the TPS16412, TPS16413, TPS16416, and TPS16417 Active Power Limiting (PLIM) With the TPS16410, TPS16411, TPS16414, and TPS16415 Active Power Limiting (PLIM) With the TPS16410, TPS16411, TPS16414, and TPS16415 Internal Current Limit for the TPS16410 and TPS16411 Internal Current Limit for the TPS16410 and TPS16411 Overcurrent Protection (IOCP) and Blanking Time (IDLY or PDLY) for Transient Loads Overcurrent Protection (IOCP) and Blanking Time (IDLY or PDLY) for Transient Loads Fast-Trip and Short-Circuit Protection Fast-Trip and Short-Circuit Protection Analog Load Current Monitor (IMON) on the IOCP Pin Analog Load Current Monitor (IMON) on the IOCP Pin IN to OUT Short Detection (TPS16410, TPS16411, TPS16412, and TPS16413) IN to OUT Short Detection (TPS16410, TPS16411, TPS16412, and TPS16413) Thermal Shutdown and Overtemperature Protection Thermal Shutdown and Overtemperature Protection Fault Response and Indication (FLT) Fault Response and Indication (FLT) Device Functional Modes Device Functional Modes Application and Implementation Application and Implementation Application Information Application Information Typical Application: 15-W Power Limiting for Low Power Circuits (LPCs) Typical Application: 15-W Power Limiting for Low Power Circuits (LPCs) Design Requirements Design Requirements Detailed Design Procedure Detailed Design Procedure Setting Overvoltage Setpoints Setting Overvoltage Setpoints Setting the Output Overcurrent Setpoint (IOCP) Setting the Output Overcurrent Setpoint (IOCP) Setting the Output Power Limit Setting the Output Power Limit Monitoring the Output Current Monitoring the Output Current Limiting the Inrush Current and Setting the Output Slew Rate Limiting the Inrush Current and Setting the Output Slew Rate Application Curves Application Curves System Examples System Examples Accurate Power or Current Limiting at the Output of DC/DC or Flyback Converter Accurate Power or Current Limiting at the Output of DC/DC or Flyback Converter Best Design Practices Best Design Practices Power Supply Recommendations Power Supply Recommendations Transient Protection Transient Protection Layout Layout Layout Guidelines Layout Guidelines Layout Example Layout Example Device and Documentation Support Device and Documentation Support ドキュメントの更新通知を受け取る方法 ドキュメントの更新通知を受け取る方法 サポート・リソース サポート・リソース Trademarks Trademarks 静電気放電に関する注意事項 静電気放電に関する注意事項 用語集 用語集 Mechanical, Packaging, and Orderable Information Mechanical, Packaging, and Orderable Information 重要なお知らせと免責事項 重要なお知らせと免責事項 TPS1641x 40V、1.8A 電力および電流制限 eFuse、入力と出力の間の短絡検出機能付き TPS1641x 40V、1.8A 電力および電流制限 eFuse、