SLUSC25A February 2015 – August 2017 TPS2388

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 Complete Register Set

- 8.6.2 INTERRUPT Register

- 8.6.3 INTERRUPT MASK Register

- 8.6.4 POWER EVENT Register

- 8.6.5 DETECTION EVENT Register

- 8.6.6 FAULT EVENT Register

- 8.6.7 START/ILIM EVENT Register

- 8.6.8 SUPPLY EVENT Register

- 8.6.9 PORT 1 STATUS Register

- 8.6.10 PORT 2 STATUS Register

- 8.6.11 PORT 3 STATUS Register

- 8.6.12 PORT 4 STATUS Register

- 8.6.13 POWER STATUS Register

- 8.6.14 Pin Status Register

- 8.6.15 OPERATING MODE Register

- 8.6.16 DISCONNECT ENABLE Register

- 8.6.17 DETECT/CLASS ENABLE Register

- 8.6.18 Port Power Priority/ICUT Disable Register Name

- 8.6.19 TIMING CONFIGURATION Register

- 8.6.20 GENERAL MASK Register

- 8.6.21 DETECT/CLASS RESTART Register

- 8.6.22 POWER ENABLE Register

- 8.6.23 RESET Register

- 8.6.24 ID Register

- 8.6.25 Police 21 Configuration Register

- 8.6.26 Police 43 Configuration Register

- 8.6.27 IEEE Power Enable Register

- 8.6.28 Power-on Fault Register

- 8.6.29 PORT RE-MAPPING Register

- 8.6.30 Port 21 Multi Bit Priority Register

- 8.6.31 Port 43 Multi Bit Priority Register

- 8.6.32 TEMPERATURE Register

- 8.6.33 INPUT VOLTAGE Register

- 8.6.34 PORT 1 CURRENT Register

- 8.6.35 PORT 2 CURRENT Register

- 8.6.36 PORT 3 CURRENT Register

- 8.6.37 PORT 4 CURRENT Register

- 8.6.38 PORT 1 VOLTAGE Register

- 8.6.39 PORT 2 VOLTAGE Register

- 8.6.40 PORT 3 VOLTAGE Register

- 8.6.41 PORT 4 VOLTAGE Register

- 8.6.42 PoE Plus Register

- 8.6.43 FIRMWARE REVISION

- 8.6.44 I2C WATCHDOG Register

- 8.6.45 DEVICE ID Register

- 8.6.46 PORT 1 DETECT RESISTANCE Register

- 8.6.47 PORT 2 DETECT RESISTANCE Register

- 8.6.48 PORT 3 DETECT RESISTANCE Register

- 8.6.49 PORT 4 DETECT RESISTANCE Register

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTQ|56

サーマルパッド・メカニカル・データ

- RTQ|56

発注情報

9.2.3 Application Curves

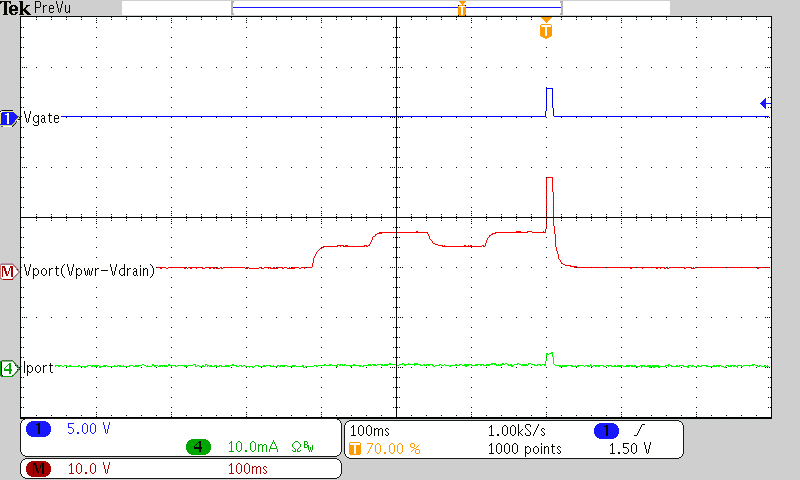

Figure 74. Detection With Invalid PD (15 kΩ and 0.1 μF)

Figure 76. Detection With Invalid PD (25 kΩ and 10 μF)

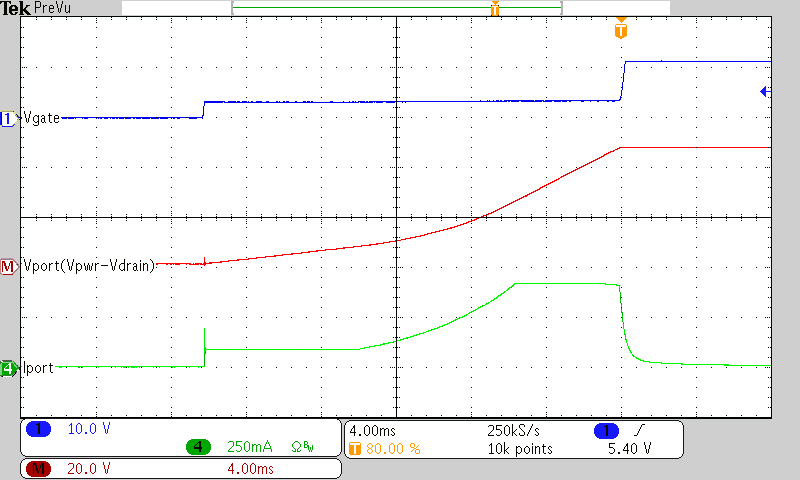

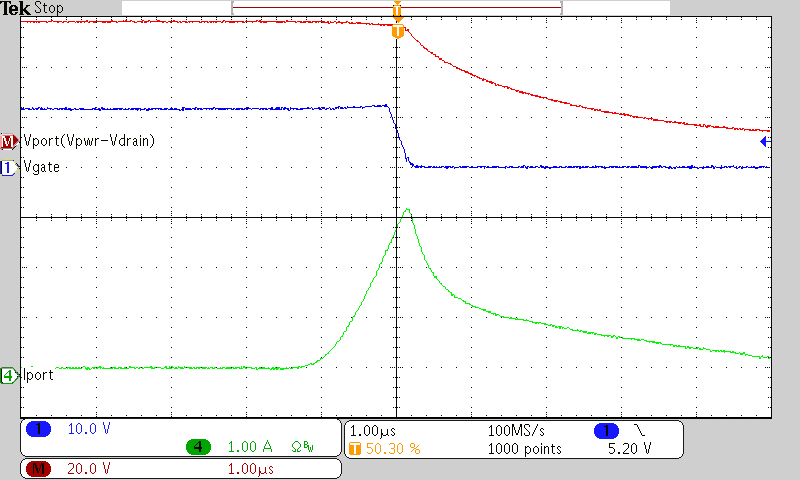

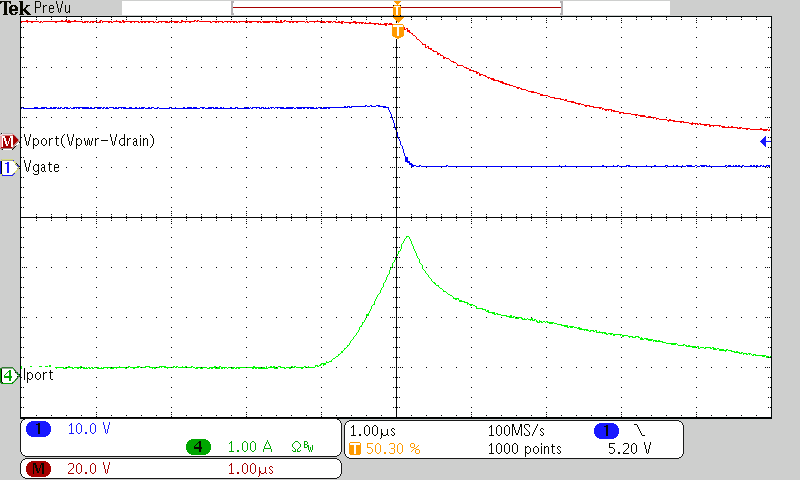

Figure 78. Powering Up into a 100-μF Load

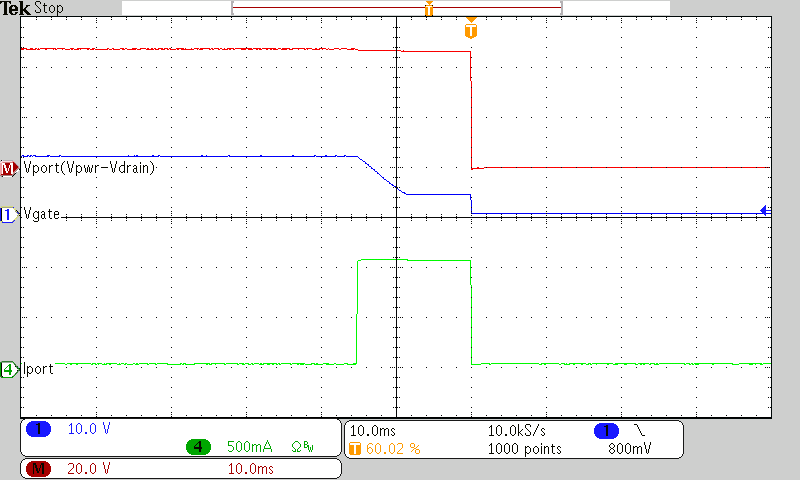

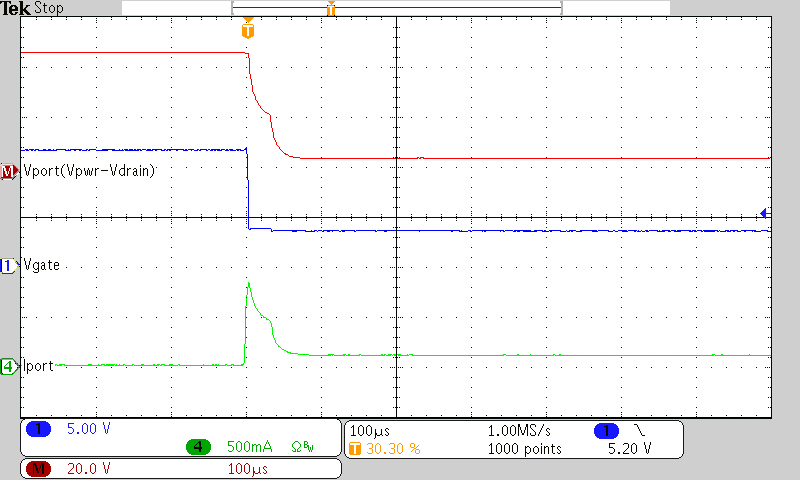

Figure 80. All Ports Fast Shutdown from OSS Input

Figure 82. Overcurrent (ICUT) Timeout

Figure 84. Rapid Response to a 1-Ω Short - PoE+ Mode

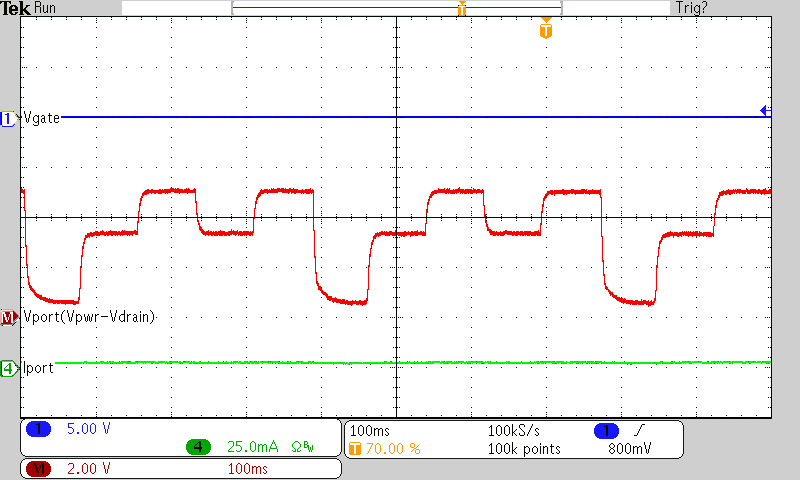

Figure 86. Response to a 25-Ω Load - PoE+ Mode

Figure 88. Current Limit 15-ms Timeout - PoE+ Mode, 45-Ω Load

Figure 90. Current Limit Timeout Restart Delay

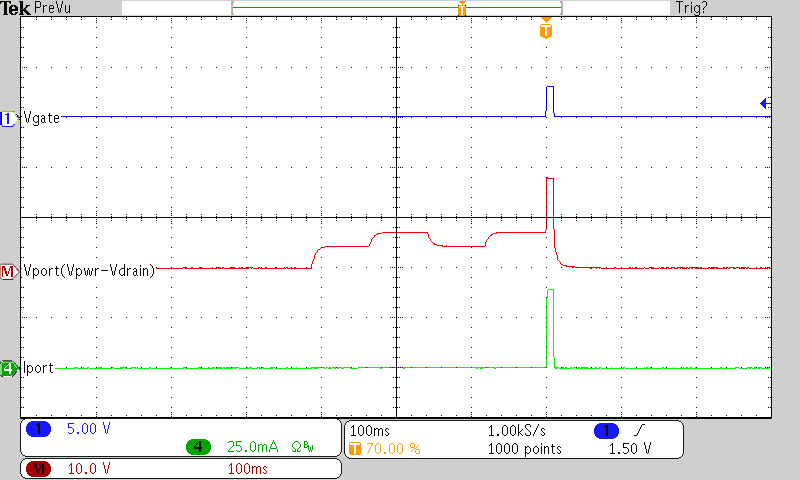

Figure 92. Detection With Open Circuit

Figure 92. Detection With Open Circuit Figure 94. 2-Event Class and Port Turn On

Figure 94. 2-Event Class and Port Turn On

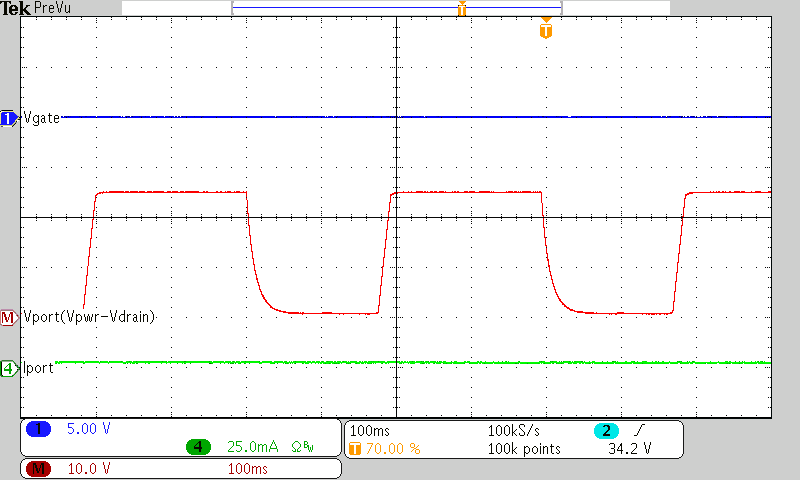

Figure 73. Startup With Valid PD (25 kΩ and 0.1 μF), Class 3

Figure 75. Detection With Invalid PD (Open Circuit)

Figure 77. 2-Event Class and Startup With Valid PD

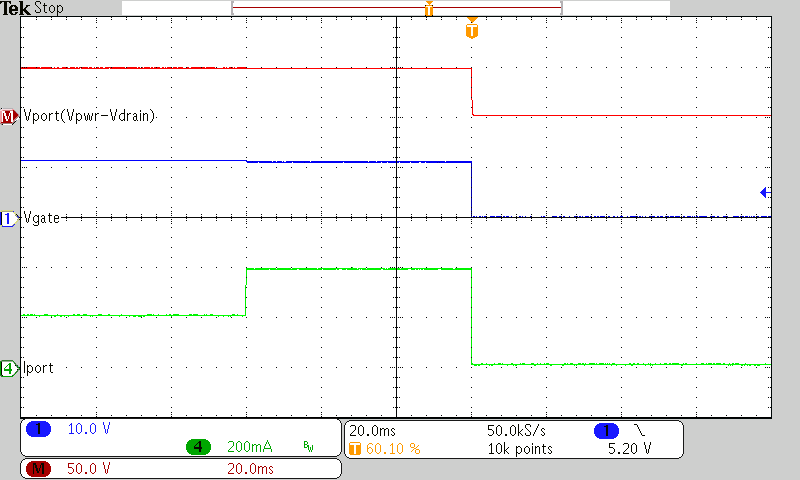

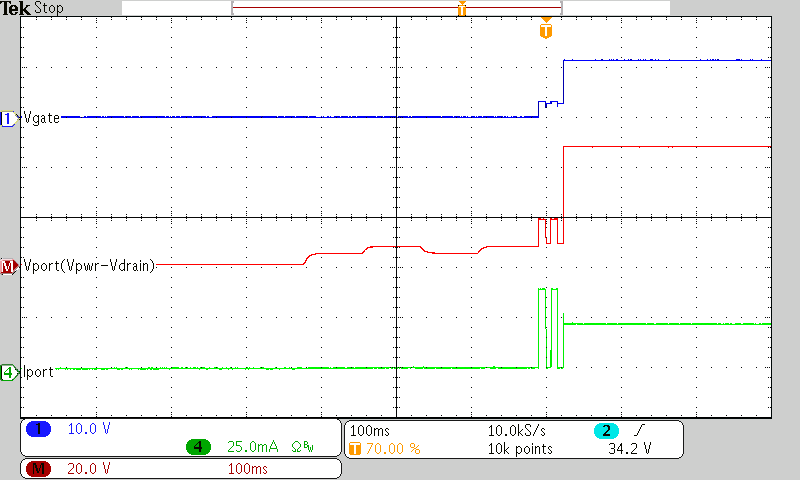

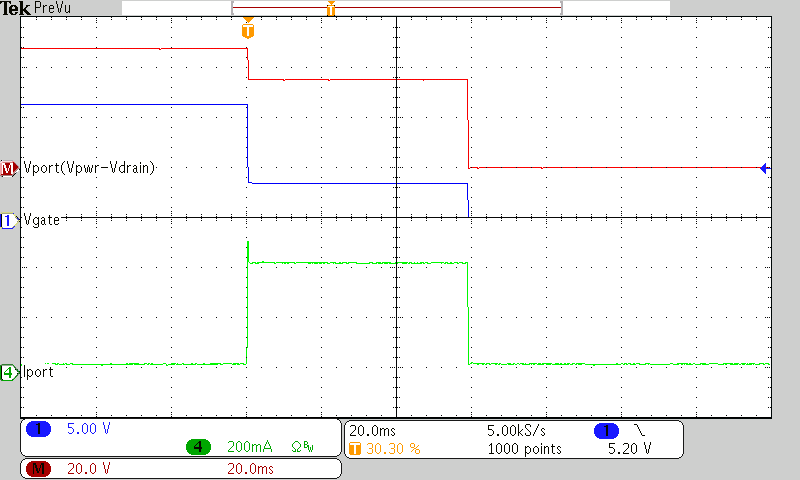

Figure 79. All Ports Power-On With TPON Bit Set

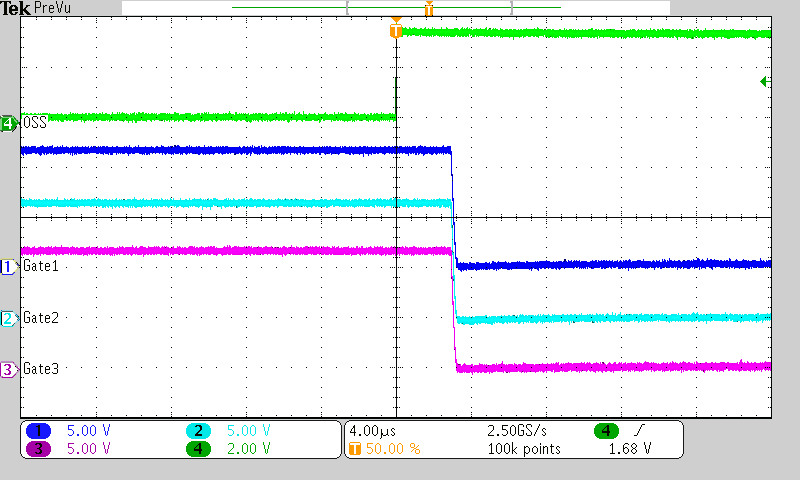

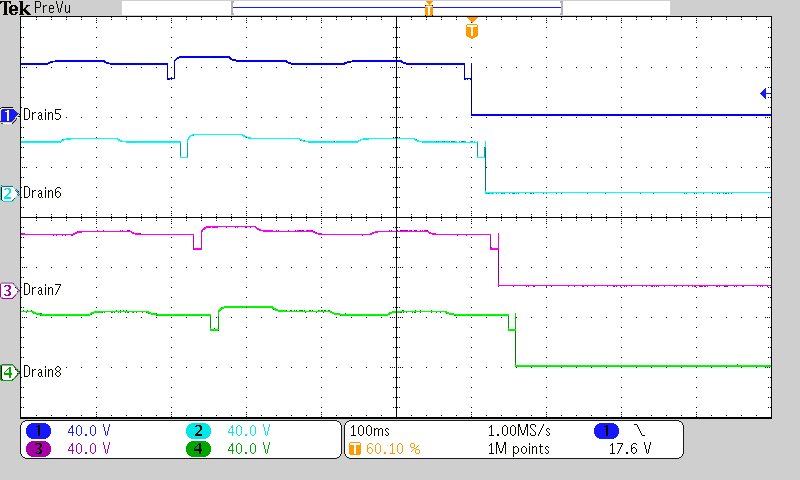

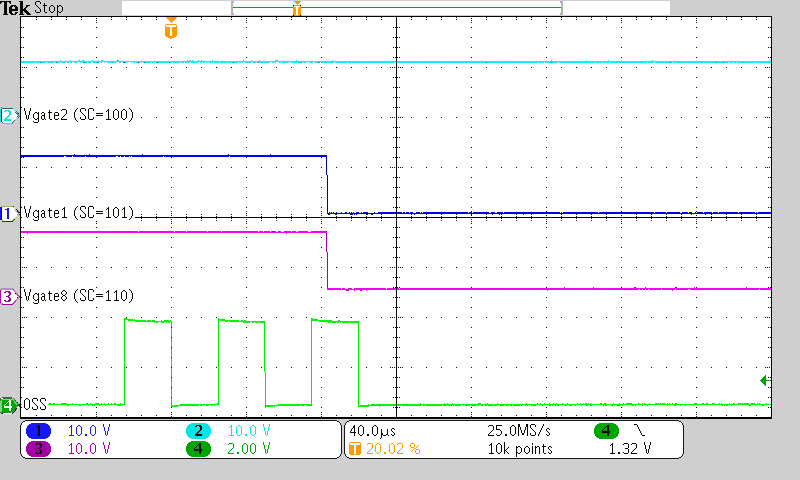

Figure 81. Ports Fast Shutdown from 3-Bit OSS Input

Figure 83. Rapid Response to a 1-Ω Short - 802.3af Mode

Figure 85. Response to a 50-Ω Load - 802.3af Mode

Figure 87. Current Limit Timeout - 802.3af Mode, 85-Ω Load

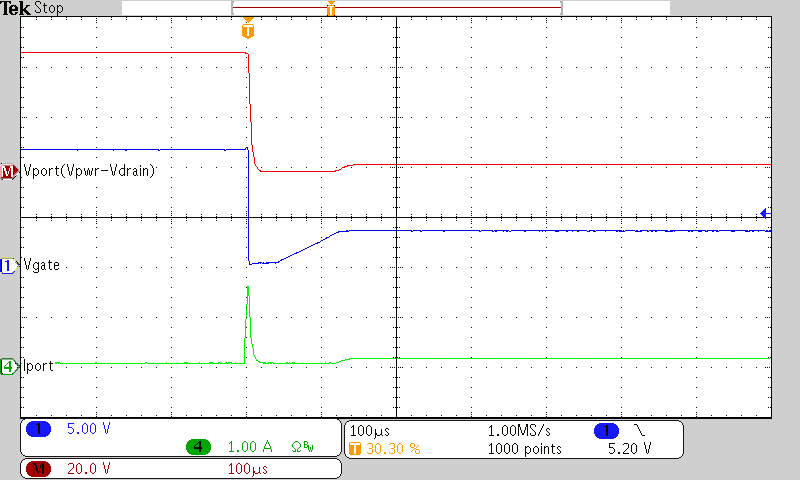

Figure 89. Inrush Fault Timeout - 100-Ω Load

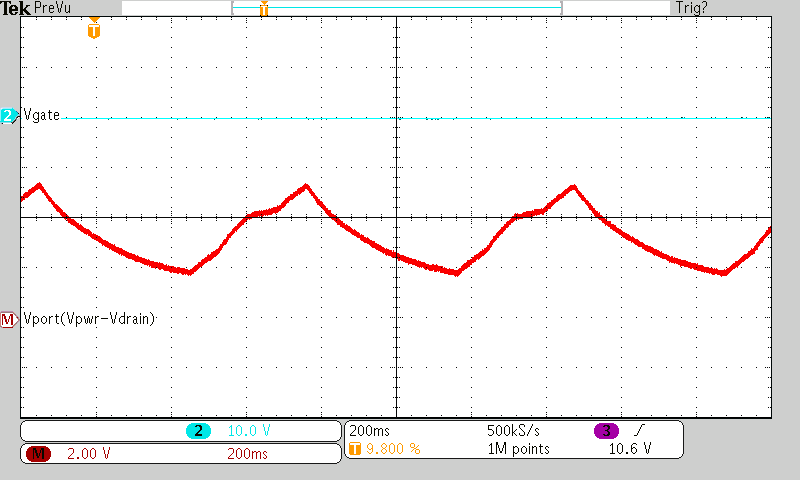

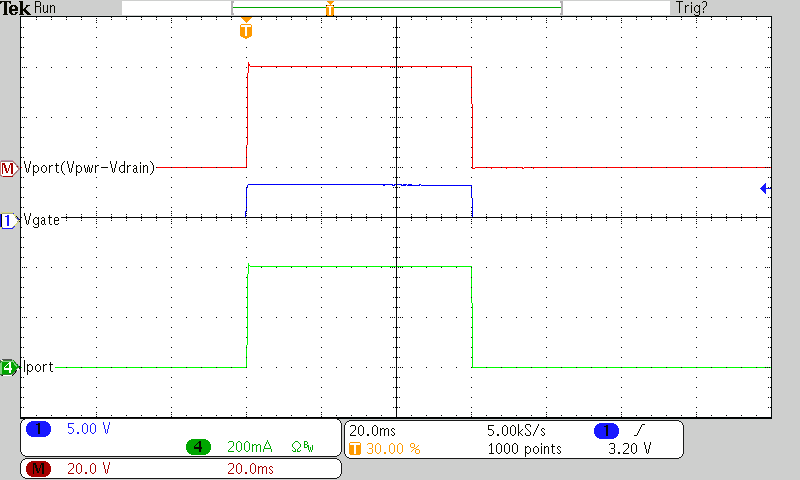

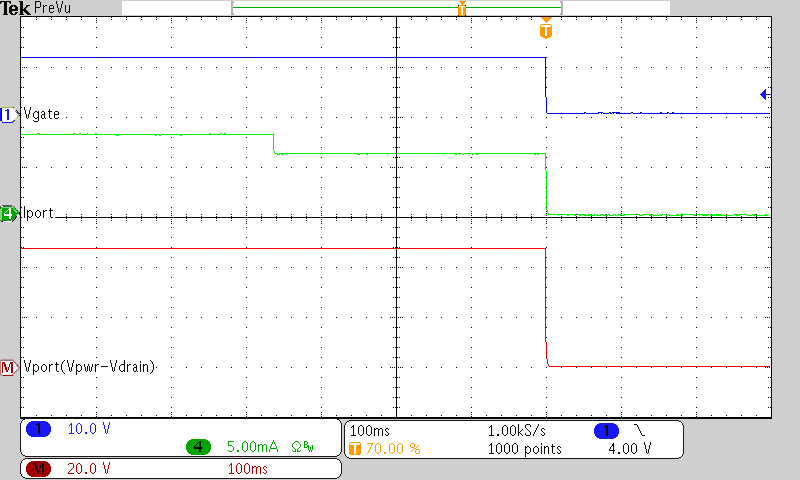

Figure 91. Response to 8-mA to 6-mA Load, DC Disconnect Enabled

Figure 93. Detection, 2-Event Class and Port Turn On

Figure 93. Detection, 2-Event Class and Port Turn On Figure 95. 2-Event Class and Port Turn On

Figure 95. 2-Event Class and Port Turn On