SLVSCU9B August 2015 – September 2016

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

Simple 3.7-A eFuse Protection for Set Top Boxes

- 9.2.1.1 Design Requirements

- 9.2.1.2 Detailed Design Procedure

- 9.2.1.3 Application Curves

- 9.2.2 Inrush and Reverse Current Protection for Hold-Up Capacitor Application (for example, SSD)

- 9.2.3 Controlled Power Down using TPS25924x

- 9.2.1

Simple 3.7-A eFuse Protection for Set Top Boxes

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DRC|10

サーマルパッド・メカニカル・データ

- DRC|10

発注情報

9 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

The TPS25924x is a smart eFuse. It is typically used for Hot-Swap and Power rail protection applications. It operates from 4.5 V to 18 V with programmable current limit and undervoltage protection. The device aids in controlling the in-rush current and provides precise current limiting during overload conditions for systems such as Set-Top-Box, DTVs, Gaming Consoles, SSDs/HDDs and Smart Meters. The device also provides robust protection for multiple faults on the sub-system rail.

The following design procedure can be used to select component values for the device. Alternatively, the WEBENCH® software may be used to generate a complete design. The WEBENCH® software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. Additionally, a spreadsheet design tool TPS2592xx Design Calculator (SLUC570) is available on web folder. This section presents a simplified discussion of the design process.

9.2 Typical Applications

9.2.1 Simple 3.7-A eFuse Protection for Set Top Boxes

Figure 39. Typical Application Schematic: Simple 3.7-A e-Fuse for STBs

Figure 39. Typical Application Schematic: Simple 3.7-A e-Fuse for STBs

9.2.1.1 Design Requirements

Table 2 shows the design parameters for this application.

Table 2. Design Parameters

| DESIGN PARAMETER | EXAMPLE VALUE | |

|---|---|---|

| VIN | Input voltage | 12 V |

| V(UV) | Undervoltage lockout set point | Default: VUVR = 4.3 V |

| V(OV) | Overvoltage protection set point | Default: VOVC = 15 V |

| RL(SU) | Load at start-up | 4 Ω |

| IOL = IILIM | Current limit | 3.7 A |

| COUT | Load capacitance | 1 µF |

| TA | Maximum ambient temperature | 85°C |

9.2.1.2 Detailed Design Procedure

The following design procedure can be used to select component values for the TPS25924x.

9.2.1.2.1 Step by Step Design Procedure

This design procedure below seeks to control the junction temperature of device under both static and transient conditions by proper selection of output ramp-up time and associated support components. The designer can adjust this procedure to fit the application and design criteria.

9.2.1.2.2 Programming the Current-Limit Threshold: RILIM Selection

The RILIM resistor at the ILIM pin sets the over load current limit, this can be set using Equation 4.

For IOL= IILIM = 3.7 A, from Equation 4, RILIM = 100 kΩ, choose closest standard value resistor with 1% tolerance.

9.2.1.2.3 Undervoltage Lockout Set Point

The undervoltage lockout (UVLO) trip point is adjusted using the external voltage divider network of R1 and R2 as connected between IN, EN/UVLO and GND pins of the device. The values required for setting the undervoltage are calculated solving Equation 5.

Where VENR = 1.4 V is enable voltage rising threshold.

Since R1 and R2 leak the current from input supply (VIN), these resistors must be selected based on the acceptable leakage current from input power supply (VIN). The current drawnby R1 and R2 from the power supply {IR12 = VIN/(R1 + R2)}.

However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current, IR12 must be chosen to be 20x greater than the leakage current expected.

For default UVLO of VUVR = 4.3 V, select R2 = OPEN, and R1 = 1 MΩ. Since EN/UVLO pin is rated only to 7 V, it cannot be connected directly to VIN= 12 V. It has to be connected through R1 = 1 MΩ only, so that the pull-up current for EN/UVLO pin is limited to < 20 µA.

The power failure threshold is detected on the falling edge of supply. This threshold voltage is 4% lower than the rising threshold, VUVR. This is calculated using Equation 6.

Where VUVR is 4.3 V, Power fail threshold set is 4.1 V.

9.2.1.2.4 Setting Output Voltage Ramp Time (TdVdT)

For a successful design, the junction temperature of device must be kept below the absolute-maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

The ramp-up capacitor CdVdT needed is calculated considering the two possible cases:

9.2.1.2.4.1 Case 1: Start-Up without Load: Only Output Capacitance COUT Draws Current During Start-Up

During start-up, as the output capacitor charges, the voltage difference as well as the power dissipated across the internal FET decreases. The average power dissipated in the device during start-up is calculated using Equation 8.

For TPS25924x, the inrush current is determined as shown in Equation 7:

Power dissipation during start-up is given by Equation 8:

Equation 8 assumes that load does not draw any current until the output voltage has reached its final value.

9.2.1.2.4.2 Case 2: Start-Up with Load: Output Capacitance COUT and Load Draws Current During Start-Up

When load draws current during the turnon sequence, there is additional power dissipated. Considering a resistive load during start-up (RL(SU)), load current ramps up proportionally with increase in output voltage during TdVdT time. The average power dissipation in the internal FET during charging time due to resistive load is given by Equation 9:

Total power dissipated in the device during startup is given by Equation 10:

Total current during startup is given by Equation 11:

If I(STARTUP) > IOL, the device limits the current to IOL and the current limited charging time is determined by Equation 12:

The power dissipation, with and without load, for selected start-up time must not exceed the shutdown limits as shown in Figure 40:

For the design example under discussion, select ramp-up capacitor CdVdT = OPEN. Then, using Equation 2, we get Equation 13:

The inrush current drawn by the load capacitance (COUT) during ramp-up using Equation 7 is given by Equation 14:

The inrush Power dissipation is calculated, using Equation 8 as shown in Equation 15:

For 90 mW of power loss, the thermal shut down time of the device must not be less than the ramp-up time TdVdT to avoid the false trip at maximum operating temperature. From thermal shutdown limit graph Figure 40 at TA = 85°C, for 90 mW of power, the shutdown time is infinite. So it is safe to use 0.79 ms as start-up time without any load on output.

Considering the start-up with load 4 Ω, the additional power dissipation, when load is present during start up is calculated by Equation 16, using Equation 9:

The total device power dissipation during start up, using Equation 10 is given by Equation 17:

From thermal shutdown limit graph at TA = 85°C, the thermal shutdown time for 6.09 W is more than 10 ms. So it is well within acceptable limits to not use an external capacitor (CdV/dT) with start-up load of 4 Ω.

If, due to large COUT, there is a need to decrease the power loss during start-up, it can be done with increase of CdVdT capacitor.

9.2.1.2.5 Support Component Selection—CVIN

CVIN is a bypass capacitor to help control transient voltages, unit emissions, and local supply noise. Where acceptable, a value in the range of 0.001 μF to 0.1 μF is recommended for CVIN.

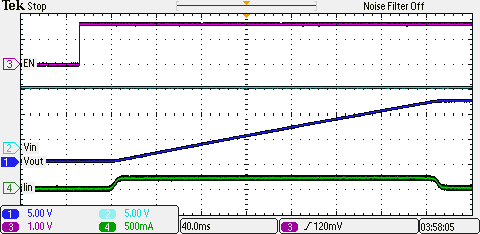

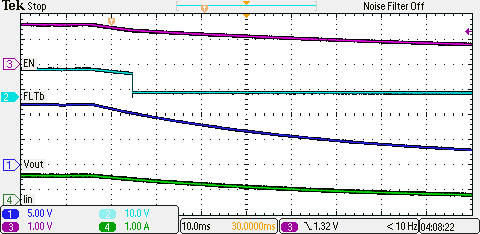

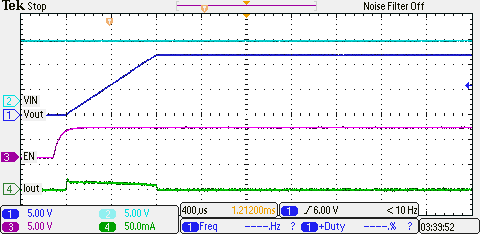

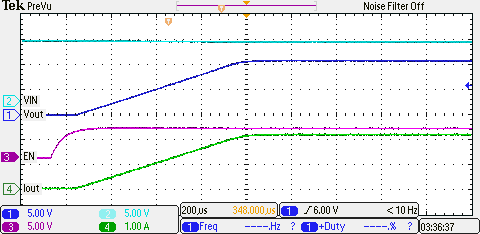

9.2.1.3 Application Curves

9.2.2 Inrush and Reverse Current Protection for Hold-Up Capacitor Application (for example, SSD)

Figure 43. Inrush and Reverse Current Protection for Hold-Up Capacitor Application (for example, SSD)

Figure 43. Inrush and Reverse Current Protection for Hold-Up Capacitor Application (for example, SSD) (TPS25924x UVLO is used as power fail comparator)

9.2.2.1 Design Requirements

The design parameters for this design example are shown in Table 3.

Table 3. Design Parameters

| DESIGN PARAMETER | EXAMPLE VALUE | |

|---|---|---|

| VIN | Input voltage | 12 V |

| V(UV) | Undervoltage lockout set point | 10.8 V |

| V(OV) | Overvoltage protection set point | Default: VOVC = 15 V |

| RL(SU) | Load at start-up | 1000 Ω |

| IOL= IILIM | Current limit | 3 A |

| COUT | Load capacitance | 4700 µF |

| TA | Maximum ambient temperature | 85°C |

9.2.2.2 Detailed Design Procedure

9.2.2.2.1 Programming the Current-Limit Threshold: RILIM Selection

The RILIM resistor at the ILIM pin sets the over load current limit, this can be set using Equation 4.

For IOL = IILIM = 3 A, from Equation 4, RILIM = 76.8 kΩ. Choose closest standard value resistor with 1% tolerance.

9.2.2.2.2 Undervoltage Lockout Set Point

The undervoltage lockout (UVLO) trip point is adjusted using the external voltage divider network of R1 and R2 as connected between IN, EN/UVLO and GND pins of the device. The values required for setting the undervoltage are calculated solving Equation 5.

For UVLO of V(UV) = 10.8 V, select R2 = 150 kΩ, and R1 = 1 MΩ.

The power failure threshold is detected on the falling edge of supply. This threshold voltage is 4% lower than the rising threshold, V(UV). This is calculated using Equation 6.

Where V(UV) = 10.73 V, Power fail threshold set is V(PFAIL) = 10.35 V.

9.2.2.2.3 Setting Output Voltage Ramp Time (TdVdT)

For a successful design, the junction temperature of device must be kept below the absolute-maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

For the design example under discussion, select ramp-up capacitor CdVdT = 22 nF. Then, using Equation 2 we get Equation 18:

The inrush current drawn by the load capacitance (COUT) during ramp-up using Equation 7 is given by Equation 19:

The inrush Power dissipation is calculated, using Equation 8 is given by Equation 20:

Considering the start-up with load 1000 Ω, the additional power dissipation, when load is present during start up is calculated, using Equation 9 is given by Equation 21:

The total device power dissipation during start up is given by Equation 22:

From thermal shutdown limit graph at TA = 85°C, the thermal shutdown time for 1.3 W is more than 300 ms. So the device starts safely.

If CdVdT = 4.7 nF was used, the device must have tried to charge the 4700-µF output cap with inrush current of 986 mA in 57.24 ms, dissipating power of 5.94 W. This is outside the safe starting condition of the device, and must have led the device to enter thermal shutdown during start-up.

9.2.3 Controlled Power Down using TPS25924x

When the device is disabled, the output voltage is left floating and power down profile is entirely dictated by the load. In some applications, this can lead to undesired activity as the load is not powered down to a defined state. Controlled output discharge can ensure the load is turned off completely and not in an undefined operational state. The BFET pin in TPS25924x family of eFuses facilitates Quick Output Discharge (QOD) function as illustrated in Figure 46. When the device is/gets disabled, the BFET pin pulls low which enables the external P-MOSFET Q1 for discharge feature to function. The output voltage discharge rate is dictated by the output capacitor COUT, the discharge resistance RDCHG and the load.

Figure 46. Circuit Implementation with Quick Output Discharge Function

Figure 46. Circuit Implementation with Quick Output Discharge Function