| POWER SUPPLY |

| VIN |

Input voltage range |

|

8 |

|

30 |

V |

| VVIN_UVLO |

Undervoltage lockout threshold |

VIN falling |

|

6.5 |

7 |

V |

| VVIN_HYS |

VIN UVLO hysteresis |

|

|

300 |

|

mV |

| Iq_VIN |

Operating quiescent current into VIN |

Device enabled, no switching, VIN = 30 V |

|

|

2 |

mA |

| ISD |

Shutdown current |

VIN = 12 V,

VIN = 30 V |

|

|

25

50 |

µA |

| VDD |

Regulation voltage for internal circuit |

0 mA < IDD < 15 mA |

5.7 |

6 |

6.3 |

V |

| EN and PWMx |

| VH |

Logic high input on EN,PWMx |

VIN = 8 V to 30 V |

1.8 |

|

|

V |

| VL |

Logic low input on EN, PWMx |

VIN = 8 V to 30 V |

|

|

0.8 |

V |

| RPD |

Pull-down resistance on EN, PWMx |

|

0.8 |

1.6 |

3 |

MΩ |

| UVLO |

| VUVLOTH |

Threshold voltage at UVLO pin |

|

1.204 |

1.229 |

1.253 |

V |

| IUVLO |

UVLO input bias current |

VUVLO = VUVLOTH – 50 mV

VUVLO = VUVLOTH + 50 mV |

–0.1

–4.3 |

-3.9 |

0.1

–3.3 |

µA |

| SOFT START |

| ISS |

Soft start charging current |

PWM ON, VREF< 2 V

PWM ON, VREF> 2 V |

|

200

10 |

|

µA |

| CURRENT REGULATION |

|

| VISET |

ISET pin voltage |

|

1.217 |

1.229 |

1.240 |

V |

| IISET_P |

ISET short-to-ground protection threshold |

|

120 |

150 |

180 |

µA |

| KISET |

Current multiple IIFB/IISET |

IISET = 32.56 µA, VIFB = 0.5 V |

3932 |

3992 |

4052 |

|

| IIFB(AVG) |

Current accuracy |

IISET = 32.56 µA, VIFB = 0.5 V |

127.4 |

130 |

132.6 |

mA |

| KIFB(M) |

Current matching; (IFB(MAX)-IFB(MIN))/2IFB(AVG) |

IISET = 32.56 µA, VIFB = 0.5 V |

|

0.5% |

1.5% |

|

| IIFB_LEAK |

IFB pin leakage current at dimming off |

IFB voltage < 40 V |

|

|

1 |

µA |

| IIFB_max |

Current sink max output current |

VIFBV = 350 mV |

130 |

|

|

mA |

| IFB REGULATION VOLTAGE |

| VIFB |

Regulation voltage at IFB |

Measured on VIFB(min), other IFB voltages are 0.5 V above VIFB(min).

IIFB = 130 mA, VIFBV = 0.5 V |

|

508 |

|

mV |

| IIFBV |

IFB Regulation voltage setting sourcing current at IFBV |

VIFBV = 0.5 V |

0.247 |

0.25 |

0.253 |

IISET |

| VIFBV |

IFBV voltage setting range |

|

0.3 |

|

1 |

V |

| BOOST REFERENCE VOLTAGE |

| VREF |

Reference voltage range for boost controller |

|

0 |

|

3.1 |

V |

| IREF_LEAK |

Leakage current at REF pin |

|

–25 |

|

25 |

nA |

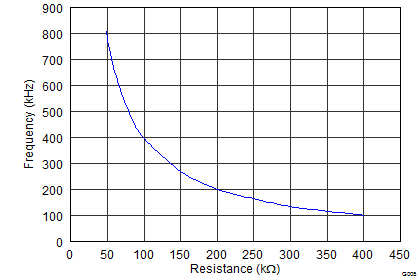

| OSCILLATOR |

| VFSW |

FSW pin reference voltage |

|

|

1.8 |

|

V |

| VFSW_H |

Logic high input voltage |

|

3.5 |

|

|

V |

| VFSW_L |

Logic low input voltage |

|

|

|

0.5 |

V |

| ERROR AMPLIFIER |

| ISINK |

Comp pin sink current |

VOVP = VREF + 200 mV, VCOMP = 1 V |

|

20 |

|

µA |

| ISOURCE |

Comp pin source current |

VOVP = VREF – 200 mV, VCOMP = 1 V |

|

20 |

|

µA |

| GmEA |

Error amplifier transconductance |

|

90 |

120 |

150 |

µS |

| REA |

Error amplifier output resistance |

|

|

20 |

|

MΩ |

|

|

|

|

|

|

|

| GATE DRIVER |

| RGDRV(SRC) |

Gate driver impedance when sourcing |

VDD = 6 V, IGDRV = –20 mA |

|

2 |

3 |

Ω |

| RGDRV(SNK) |

Gate driver impedance when sinking |

VDD = 6 V, IGDRV = 20 mA |

|

1 |

1.5 |

Ω |

| IGDRV(SRC) |

Gate driver source current |

VGDRV = 5 V |

200 |

|

|

mA |

| IGDRV(SNK) |

Gate driver sink current |

VGDRV = 1 V |

400 |

|

|

mA |

| VISNS(OC) |

Overcurrent detection threshold |

VIN = 8 V to 30 V, TJ = 25°C to 125°C |

376 |

400 |

424 |

mV |

| OVERVOLTAGE PROTECTION (OVP) |

| VOVPTH |

Output voltage OVP threshold |

|

2.95 |

3.02 |

3.09 |

V |

| IOVP |

Leakage current |

|

–100 |

0 |

100 |

nA |

| VIFB_OVP |

IFBx over voltage threshold |

PWM ON |

|

38 |

|

V |

| LED SHORT DETECTION |

| IFBP |

LED short detection sourcing current |

VFBP = 1 V |

0.247 |

0.25 |

0.253 |

IISET |

| FAULT INDICATOR |

| IFLT_H |

Leakage current in high impedance |

VFLT = 24 V |

|

1 |

|

nA |

| IFLT_L |

Sink current at low output |

VFLT = 1 V |

1 |

2 |

|

mA |

| THERMAL SHUTDOWN |

| Tshutdown |

Thermal shutdown threshold |

|

|

150 |

|

°C |

| Thys |

Thermal shutdown threshold hysteresis |

|

|

15 |

|

°C |