JAJSLY4B January 2023 – May 2024 TPS62870 , TPS62871 , TPS62872 , TPS62873

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 概要 (続き)

- 5 Device Options

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Fixed-Frequency DCS Control Topology

- 8.3.2 Forced PWM and Power Save Modes

- 8.3.3 Precise Enable

- 8.3.4 Start-Up

- 8.3.5 Switching Frequency Selection

- 8.3.6 Output Voltage Setting

- 8.3.7 Compensation (COMP)

- 8.3.8 Mode Selection and Clock Synchronization (MODE/SYNC)

- 8.3.9 Spread Spectrum Clocking (SSC)

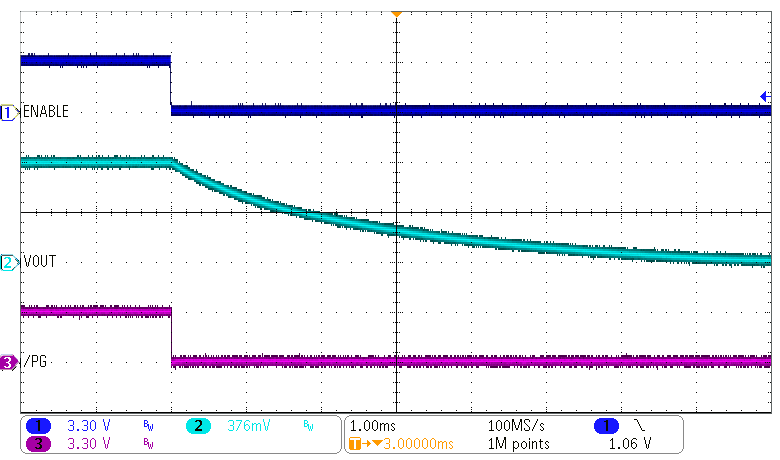

- 8.3.10 Output Discharge

- 8.3.11 Undervoltage Lockout (UVLO)

- 8.3.12 Overvoltage Lockout (OVLO)

- 8.3.13 Overcurrent Protection

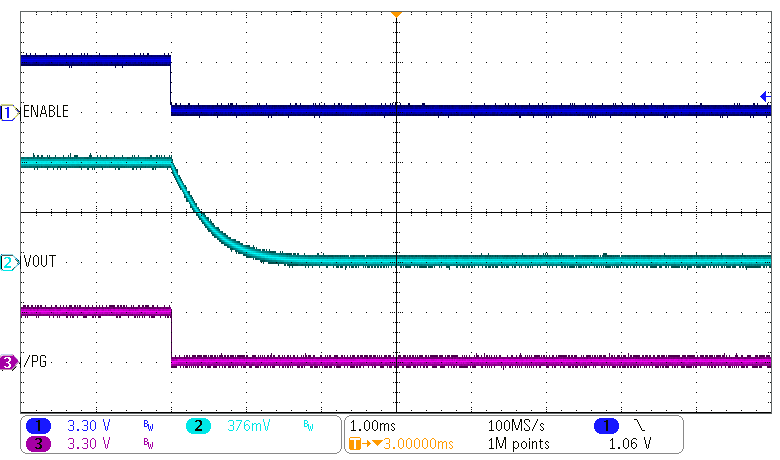

- 8.3.14 Power Good (PG)

- 8.3.15 Remote Sense

- 8.3.16 Thermal Warning and Shutdown

- 8.3.17 Stacked Operation

- 8.4 Device Functional Modes

- 8.5 Programming

- 9 Register Map

- 10Application and Implementation

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

10.2.3 Application Curves

| VOUT = 0.4V |

| VOUT = 0.5V |

| VOUT = 0.75V |

| VOUT = 0.875V |

| VOUT = 1.05V |

| IOUT = 10A |

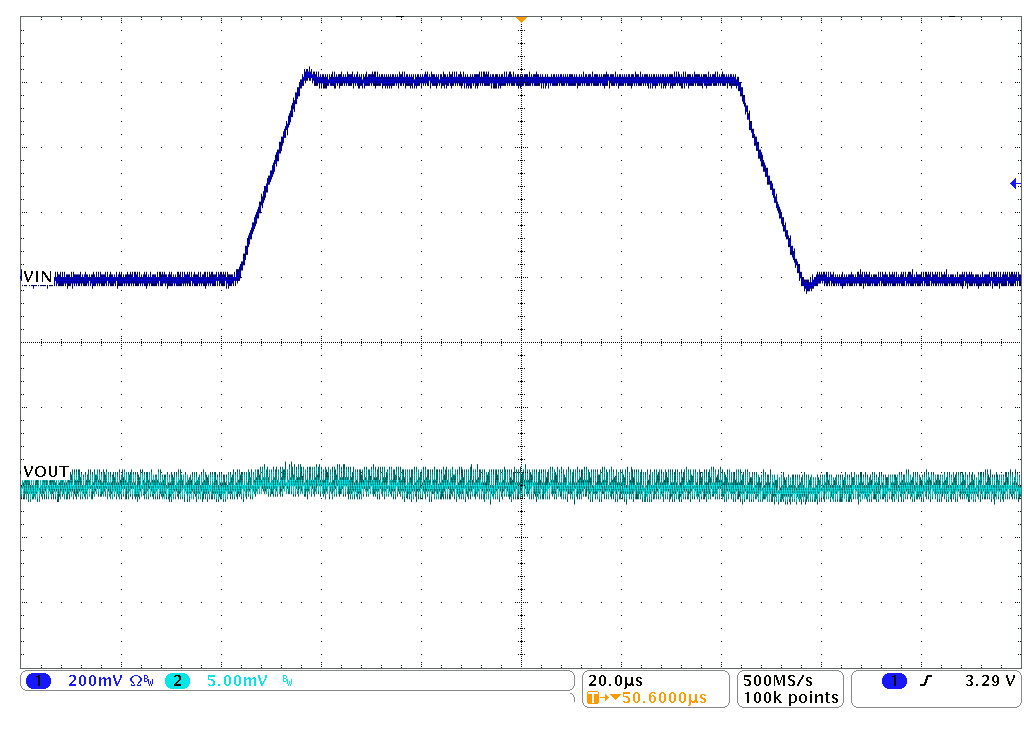

Figure 10-14 Line Transient Response

Figure 10-14 Line Transient Response

| IOUT = 2A |

| IOUT = 75mA |

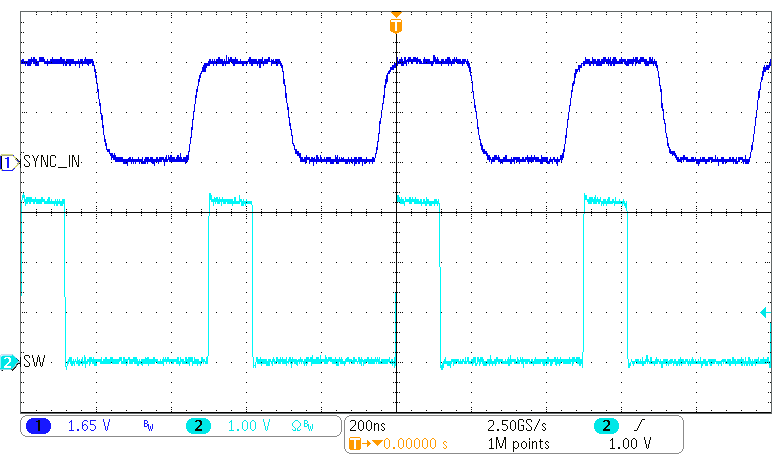

| Load = 0.75Ω | FSEL = 2.25MHz | f(SYNC) = 2MHz |

| Load = 7.5Ω |

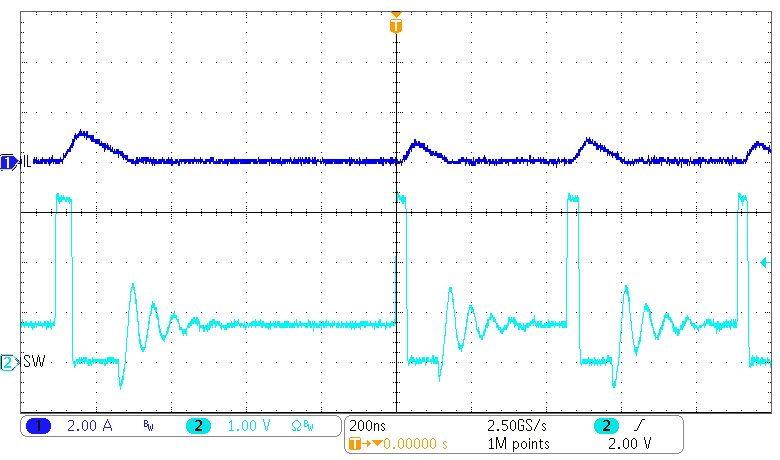

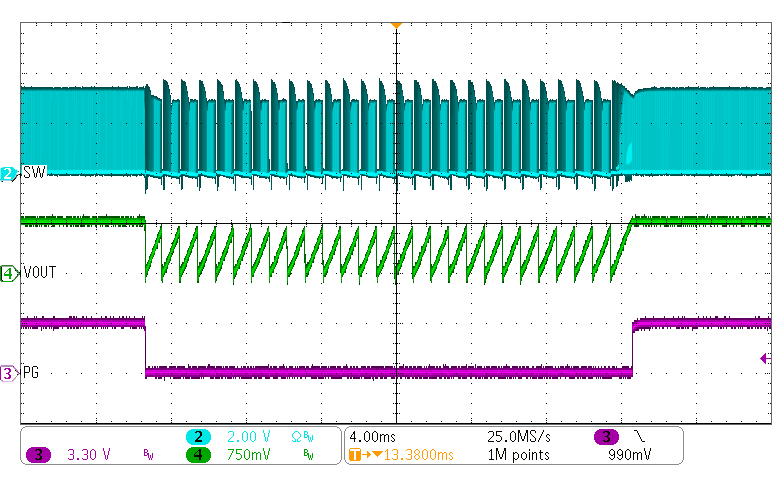

Figure 10-24 Current Limit (Hiccup)

Figure 10-24 Current Limit (Hiccup)

| VOUT = 0.4V |

| VOUT = 0.5V |

| VOUT = 0.75V |

| VOUT = 0.875V |

| VOUT = 1.05V |

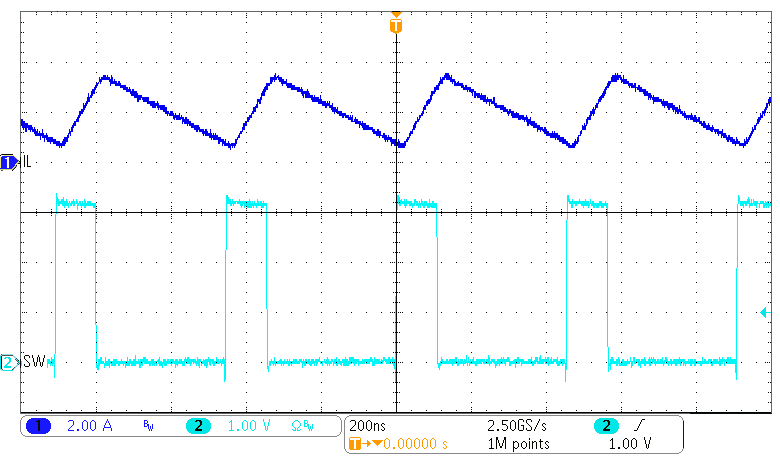

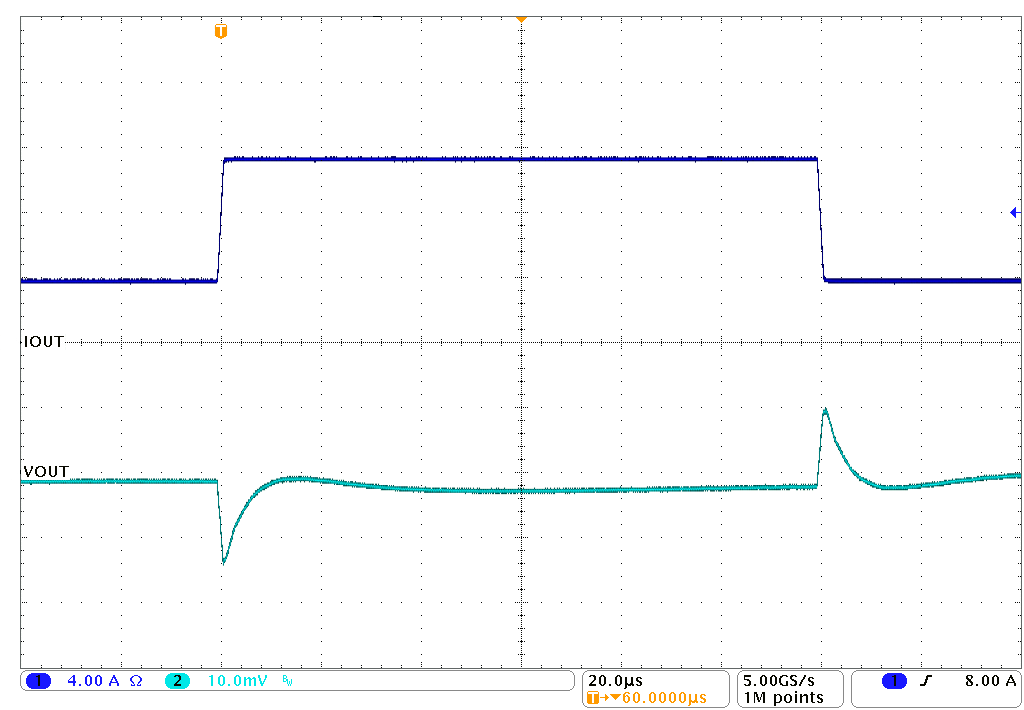

| IOUT = 15A | VOUT = 0.875V |

| ΔIOUT = 7.5A | CH1 = 50mV/A |

| IOUT = 750mA |

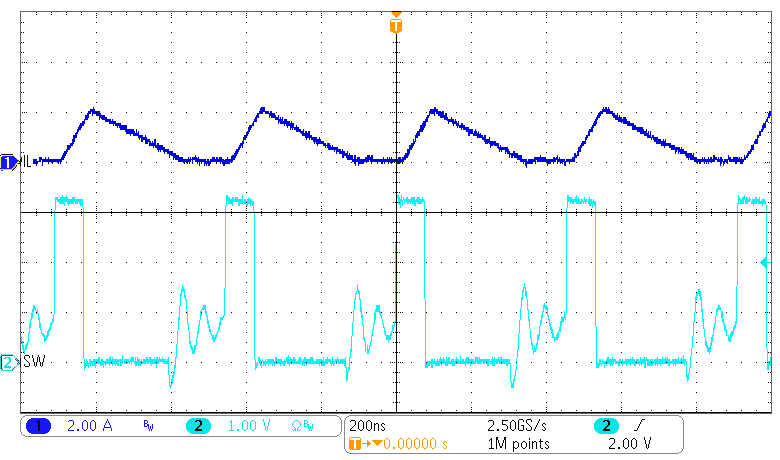

| VOUT = 0.75V | IOUT = 11.5A |

| Load = 0.75Ω |

| Load = 7.5Ω |