SNVS900B DECEMBER 2012 – December 2015 TPS92560

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DGQ|10

サーマルパッド・メカニカル・データ

- DGQ|10

発注情報

6 Specifications

6.1 Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| SRC, SEN, ADJ | –0.3 | 5 | V | |

| AC1, AC2 | –1 | 45 | V | |

| VP | –0.3 | 45 | V | |

| VCC | –0.3 | 12 | V | |

| TJ | Junction temperature | –40 | 125 | °C |

| Tstg | Storage temperature | –65 | 150 | °C |

(1) Absolute Maximum Ratings are limits which damage to the device may occur. Operating ratings are conditions under which operation of the device is intended to be functional. For specified specifications and test conditions, see the electrical characteristics.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±1500 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±1000 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VP | Supply voltage | 6.5 | 42 | V | |

| TJ | Junction temperature | –40 | 125 | °C | |

6.4 Thermal Information

| THERMAL METRIC(1) | TPS92560 | UNIT | |

|---|---|---|---|

| DGQ (HVSSOP) | |||

| 10 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 55.8 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 43.7 | °C/W |

| RθJB | Junction-to-board thermal resistance | 32.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 1.3 | °C/W |

| ψJB | Junction-to-board characterization parameter | 31.8 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 5.0 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

6.5 Electrical Characteristics

Over recommended operating conditions with -40°C ≤ TJ ≤ 125°C. Unless otherwise stated the following conditions apply: VVP = 12V| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SUPPLY | ||||||

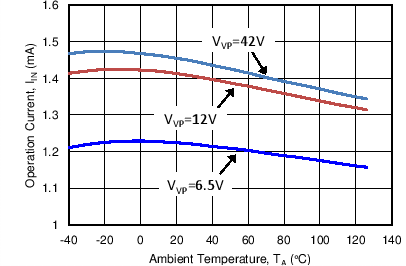

| IIN | VIN Operating current | 6.5 V < VVP < 42 V | 0.7 | 1.4 | 1.95 | mA |

| VCC REGULATOR | ||||||

| VCC | VCC Regulated voltage(1) | ICC ≤ 10 mA, CVCC =0.47 µF 12 V < VVP < 42 V |

7.82 | 8.45 | 9.08 | V |

| ICC = 10 mA, CVCC =0.47 µF VVP = 6.5 V | 5.22 | 5.8 | 6.18 | |||

| ICC = 0 mA, CVCC =0.47 µF VVP = 2 V | 1.96 | 2 | ||||

| ICC-LIM | VCC Current limit | VCC = 0 V 6.5 V < VVP < 42 V | 21 | 30 | 39 | mA |

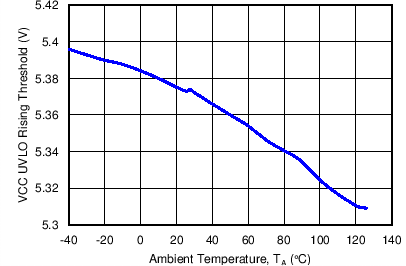

| VCC-UVLO-UPTH | VCC UVLO upper threshold | 5 | 5.38 | 5.76 | V | |

| VCC-UVLO-LOTH | VCC UVLO lower threshold | 4.63 | 4.98 | 5.33 | V | |

| VCC-UVLO-HYS | VCC UVLO hysteresis | 190 | 400 | 640 | mV | |

| MOSFET GATE DRIVER | ||||||

| VGATE-HIGH | Gate driver output high | w.r.t. SRC Sinking 100mA from GATE Force VCC = 8.5 V |

7.61 | 8.1 | 8.5 | V |

| VGATE-LOW | Gate driver output low | w.r.t. SRC Sourcing 100 mA to GATE |

100 | 180 | 290 | mV |

| tRISE | VGATE Rise time | CGATE = 1 nF across GATE and SRC | 22 | ns | ||

| tFALL | VGATE Fall time | CGATE = 1 nF across GATE and SRC | 14 | ns | ||

| tRISE-PG-DELAY | VGATE Low-to-high propagation delay | CGATE = 1 nF across GATE and SRC | 68 | ns | ||

| tFALL-PG-DELAY | VGATE High-to-low propagation delay | CGATE = 1 nF across GATE and SRC | 84 | ns | ||

| CURRENT SOURCE AT ADJ PIN | ||||||

| IADJ-STARTUP | Output current of ADJ pin at start-up | VADJ = 0 V | 16 | 20 | 24 | µA |

| IADJ-ELEC-XFR | Output current of ADJ pin for electronic transformers | An Electronic transformer is detected | 8 | 11.5 | 15 | µA |

| IADJ-MAG-XFR | Output current of ADJ pin for inductive transformers | A magnetic transformer is detected | 7 | 9.5 | 12 | µA |

| CURRENT SENSE COMPARATOR | ||||||

| VSEN-UPPER-TH | VSEN Upper threshold over VADJ | VSEN-VADJ, VADJ=0.2 V, VGATE at falling edge | 8.9 | 14.9 | 20.9 | mV |

| VSEN-LOWER-TH | VSEN Lower threshold over VADJ | VSEN-VADJ, VADJ=0.2 V VGATE at rising edge | -20.6 | –14.9 | -8.8 | mV |

| VSEN-HYS | VSEN Hysteresis | (VSEN-UPPER-TH - VSEN-LOWER-TH) | 22.5 | 29.8 | 37.5 | mV |

| VSEN-OFFSET | VSEN Offset w.r.t. VADJ | (VSEN-UPPER-TH + VSEN-LOWER-TH)/2 | -3.5 | 0.02 | 3.5 | mV |

| ACTIVE LOW-SIDE INPUT RECTIFIERS | ||||||

| RACn-ON | In resistance of AC1 and AC2 to GND | IACn = 200 mA | 300 | 570 | mΩ | |

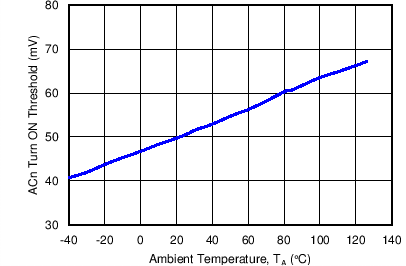

| VACn-ON-TH | Turn ON voltage threshold of AC1 and AC2 | VACn Decreasing, TJ = 25°C | 36 | 52 | 67 | mV |

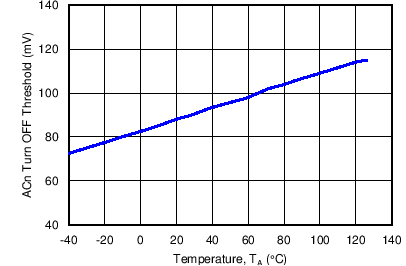

| VACn-OFF-TH | Turn OFF voltage threshold of AC1 and AC2 | VACn Increasing, TJ = 25°C | 77 | 90 | 104 | mV |

| VACn-TH-HYS | Hysteresis voltage of AC1 and AC2 | VACn-OFF-TH - VACn-ON-TH | 39 | mV | ||

| IACn-OFF | Off current of AC1 and AC2 | VACn = 45 V | 21 | 32 | µA | |

| OUTPUT OVERVOLTAGE-PROTECTION (OVP) | ||||||

| VADJ-OVP-UPTH | Output overvoltage-detection upper threshold | VADJ Increasing, VGATE at falling edge | 0.353 | 0.384 | 0.415 | V |

| VADJ-OVP-LOTH | Output overvoltage-detection lower threshold | VADJ Decreasing, VGATE at rising edge | 0.312 | 0.339 | 0.366 | V |

| VADJ-OVP-HYS | Output overvoltage-detection hysteresis | VADJ-OVP-UPTH - VADJ-OVP-LOTH | 25 | 46 | 67 | mV |

| THERMAL SHUTDOWN | ||||||

| TSD | Thermal shutdown temperature | TJ Rising | 165 | °C | ||

| TSD-HYS | Thermal shutdown temperature hysteresis | TJ Falling | 30 | °C | ||

(1) VCC provides self bias for the internal gate drive and control circuits. Device thermal limitations limit external loading.

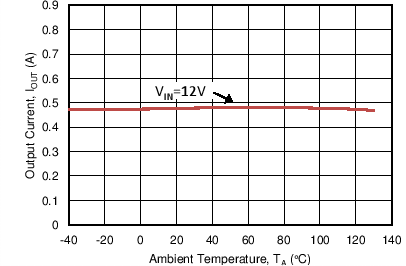

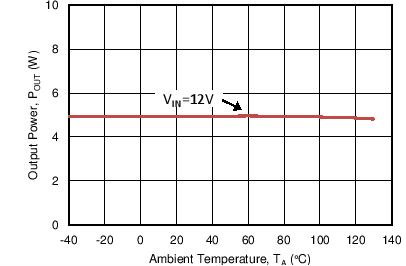

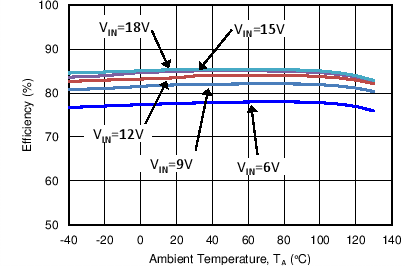

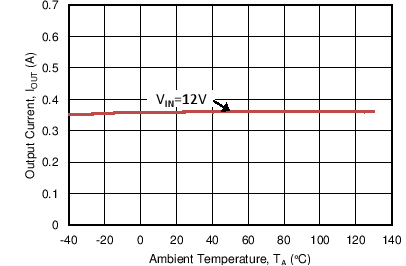

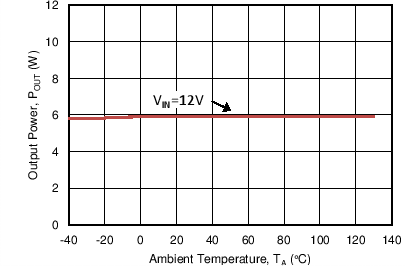

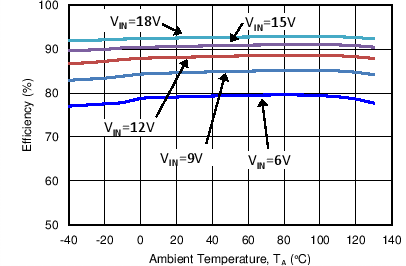

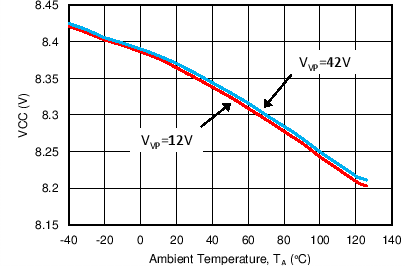

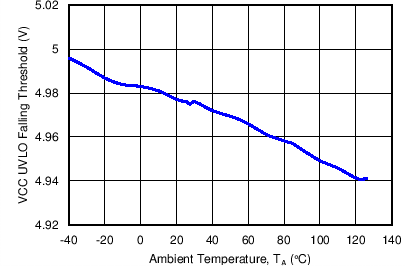

6.6 Typical Characteristics

All curves taken for the boost circuit are with 500-mA nominal input current and 6 serial LEDs. All curves taken for the SEPIC circuit are with 500-mA nominal input current and 3 serial LEDs.TA = –40°C to 125°C, unless otherwise specified.

VVP = 12 V, GATE = Hi

VVP = 12 V, GATE = Low