JAJSN49 January 2022 TPSM5D1806E

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Adjustable Output Voltage

- 7.3.2 Frequency Selection

- 7.3.3 Minimum and Maximum Input Voltage

- 7.3.4 Recommended Settings

- 7.3.5 Device Mode Configuration

- 7.3.6 Input Capacitors

- 7.3.7 Minimum Required Output Capacitance

- 7.3.8 Ambient Temperature Versus Total Power Dissipation

- 7.3.9 Remote Sense

- 7.3.10 Enable (EN) and Undervoltage Lockout (UVLO)

- 7.3.11 Soft Start

- 7.3.12 Power Good

- 7.3.13 Safe Start-Up into Pre-Biased Outputs

- 7.3.14 BP5

- 7.3.15 Overcurrent Protection

- 7.3.16 Thermal Shutdown

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

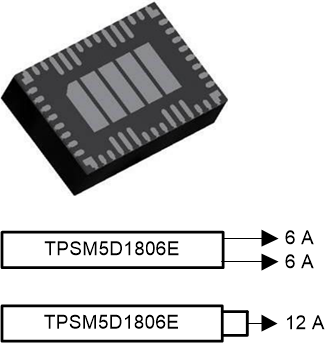

TPSM5D1806E デュアル 6A 出力パワー・モジュールは、小型 (8mm × 5.5mm × 1.8mm) の QFN パッケージに封止された柔軟な高集積 DC-DC 電源です。4.5V~15V の入力電圧範囲は、標準的な 5V および 12V レールだけでなく幅広い中間バスからの変換を可能にします。2 つの 6A 出力は、2 つの独立した電源レールとして別々に構成することも、1 つの 2 相 12A 出力として結合することもできます。

薄型 51 ピン QFN パッケージは、最適に配置することで高い熱性能を発揮します。–55℃に拡張された低温性能は、室外設置モジュールまたはフライト制御ユニットなどの環境の航空宇宙アプリケーションを可能にします。基板レイアウトを単純にし製造時の取り扱いを簡単にするため、本デバイスのすべての信号ピンは外周から接続できるように配置され、真下には大型サーマル・パッドが設けられています。

この統合型電源設計を使うと、ループ補償も磁気部品の選択も設計プロセスから取り除くことができます。本デバイスは、出力ごとに独立したイネーブル制御とパワー・グッド信号を備えています。スイッチング周波数と位相オフセットは、ピン・ストラップを使って設定できます。本デバイスは、過電流およびサーマル・シャットダウン保護機能も備えています。

製品情報

| デバイス番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| TPSM5D1806E | QFN | 8mm × 5.5mm × 1.8mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

デュアル出力の概略回路図

デュアル出力の概略回路図 出力構成

出力構成