JAJSUT1B June 2024 – November 2024 TUSB2E221

PRODMIX

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Device Variants

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parametric Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 9 Register Map

- 10Applications and Implementation

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

8.5.1 I2C Target Interface

I2C target interface enables access to internal registers by the system application processor. The primary function of the interface is to enable configuring various PHY parameters, controlling the GPIO pins, and enabling USB-BC functions. The TUSB2E221 repeater functions operates after power up without requiring I2C configuration.

The TUSB2E221 has I2C 7-bit target address of 0x4F. 8-bit address of Write: 0x9E and Read: 0x9F.

I2C default target address can be changed at the factory through one-time programming.

I2C drive strength can be changed through the I2C.

| I2C FM+ (1MHz Max) | I2C drive strength (IOL) selection | |||

|---|---|---|---|---|

| I2C bus pullup RPU | ||||

| C(bus) pF | 1kΩ | 2.2kΩ | 4kΩ | 7kΩ |

| 10-50 | ≅8mA | ≅4mA | N/A | N/A |

| 10-90 | ≅8mA | N/A | N/A | N/A |

| 10-150 | N/A | N/A | N/A | N/A |

| 10-200 | N/A | N/A | N/A | N/A |

| I2C FM (400kHz Max) | I2C drive strength (IOL) selection | |||

|---|---|---|---|---|

| I2C bus pullup RPU | ||||

| C(bus) pF | 1kΩ | 2.2kΩ | 4kΩ | 7kΩ |

| 10-50 | ≅8mA | ≅4mA | ≅2mA | N/A |

| 10-90 | ≅8mA | ≅4mA | N/A | N/A |

| 10-150 | ≅8mA | ≅8mA | N/A | N/A |

| 10-200 | ≅8mA | N/A | N/A | N/A |

| I2C STD (100kHz Max) | I2C drive strength (IOL) selection | |||

|---|---|---|---|---|

| I2C bus pullup RPU | ||||

| C(bus) pF | 1kΩ | 2.2kΩ | 4kΩ | 7kΩ |

| 10-50 | ≅8mA | ≅4mA | ≅2mA | ≅1mA |

| 10-90 | ≅8mA | ≅4mA | ≅2mA | ≅1mA |

| 10-150 | ≅8mA | ≅4mA | ≅2mA | ≅2mA |

| 10-200 | ≅8mA | ≅4mA | ≅2mA | ≅2mA |

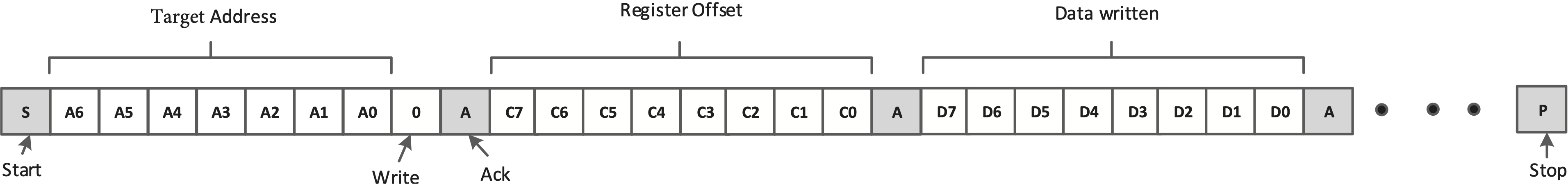

Figure 8-5 I2C Write with Data

Figure 8-5 I2C Write with DataUse this procedure to write data to TUSB2E221 I2C registers (refer to Figure 8-5):

- The host initiates a write operation by generating a start condition (S), followed by the TUSB2E221 7-bit address and a zero-value “W/R” bit to indicate a write cycle.

- The TUSB2E221 acknowledges the address cycle.

- The host presents the register offset within the TUSB2E221 to be written, consisting of one byte of data, MSB-first.

- The TUSB2E221 acknowledges the sub-address cycle.

- The host presents the first byte of data to be written to the I2C register.

- The TUSB2E221 acknowledges the byte transfer.

- The host may continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the TUSB2E221.

- The host terminates the write operation by generating a stop condition (P).

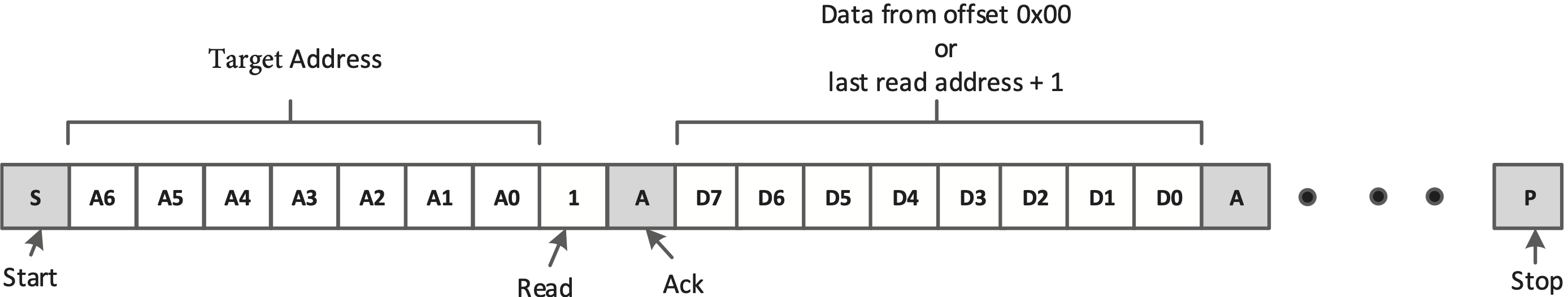

Figure 8-6 I2C Read Without Repeated Start

Figure 8-6 I2C Read Without Repeated StartUse this procedure to read the TUSB2E221 I2C registers without a repeated Start (refer Figure 8-6).

- The host initiates a read operation by generating a start condition (S), followed by the TUSB2E221 7-bit address and a zero-value “W/R” bit to indicate a read cycle.

- The TUSB2E221 acknowledges the 7-bit address cycle.

- Following the acknowledge the host continues sending clock.

- The TUSB2E221 transmit the contents of the memory registers MSB-first starting at register 00h or last read register offset+1. If a write to the I2C register occurred prior to the read, then the TUSB2E221 shall start at the register offset specified in the write.

- The TUSB2E221 waits for either an acknowledge (ACK) or a not-acknowledge (NACK) from the host after each byte transfer; the I2C host acknowledges reception of each data byte transfer.

- If an ACK is received, the TUSB2E221 transmits the next byte of data as long as host provides the clock. If a NAK is received, the TUSB2E221 stops providing data and waits for a stop condition (P).

- The host terminates the write operation by generating a stop condition (P).

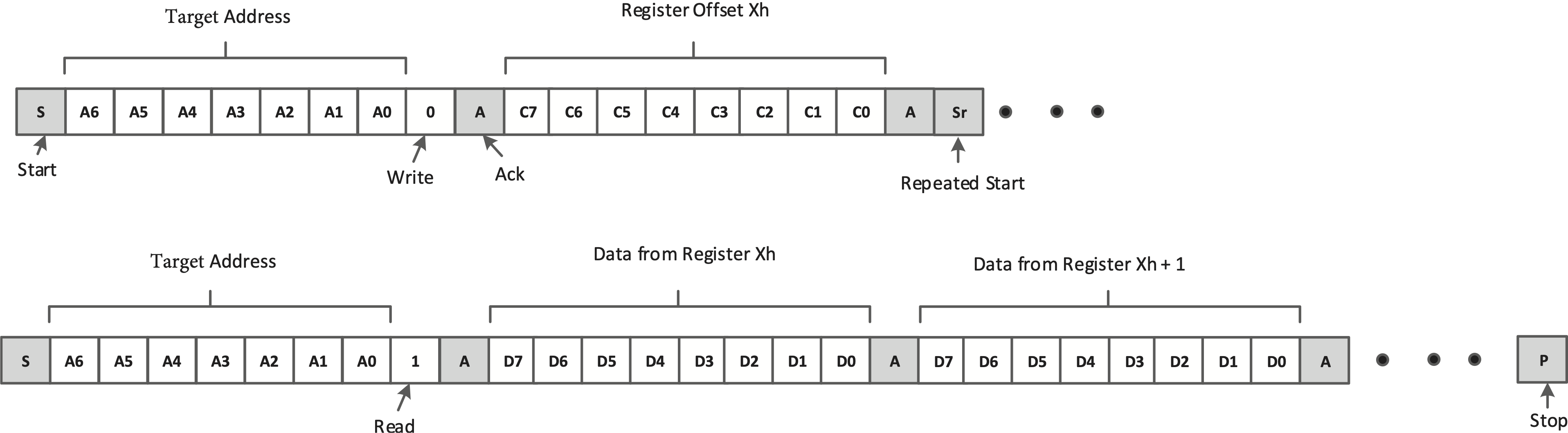

Figure 8-7 I2C Read with Repeated Start

Figure 8-7 I2C Read with Repeated StartUse this procedure to read the TUSB2E221 I2C registers with a repeated Start (refer Figure 8-7).

- The host initiates a read operation by generating a start condition (S), followed by the TUSB2E221 7-bit address and a zero-value “W/R” bit to indicate a write cycle.

- The TUSB2E221 acknowledges the 7-bit address cycle.

- The host presents the register offset within the TUSB2E221 to be written, consisting of one byte of data, MSB-first.

- The TUSB2E221 acknowledges the register offset cycle.

- The host presents a repeated start condition (Sr).

- The host initiates a read operation by generating a start condition (S), followed by the TUSB2E221 7-bit address and a one-value “W/R” bit to indicate a read cycle.

- The TUSB2E221 acknowledges the 7-bit address cycle.

- The TUSB2E221 transmit the contents of the memory registers MSB-first starting at the register offset.

- The TUSB2E221 shall wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the host after each byte transfer; the I2C host acknowledges reception of each data byte transfer.

- If an ACK is received, the TUSB2E221 transmits the next byte of data as long as host provides the clock. If a NAK is received, the TUSB2E221 stops providing data and waits for a stop condition (P).

- The host terminates the read operation by generating a stop condition (P).

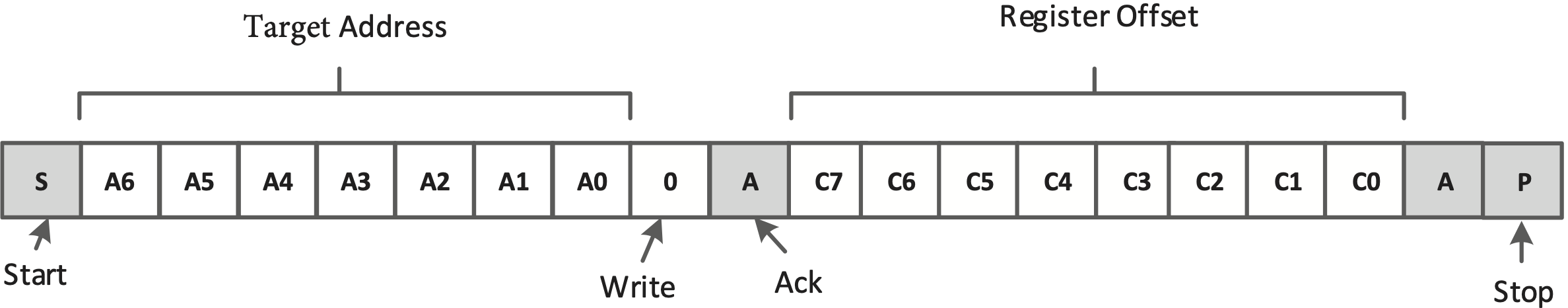

Figure 8-8 I2C Write Without Data

Figure 8-8 I2C Write Without DataUse this procedure to set a starting sub-address for I2C reads (refer to Figure 8-8).

- The host initiates a write operation by generating a start condition (S), followed by the TUSB2E221 7-bit address and a zero-value “W/R” bit to indicate a write cycle.

- The TUSB2E221 acknowledges the address cycle.

- The host presents the register offset within the TUSB2E221 to be written, consisting of one byte of data, MSB-first.

- The TUSB2E221 acknowledges the register offset cycle.

- The host terminates the write operation by generating a stop condition (P).

Figure 8-9 I2C Timing Diagram

Figure 8-9 I2C Timing Diagram