JAJSTR1D April 1994 – March 2024

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Device Functional Modes

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|8

- P|8

サーマルパッド・メカニカル・データ

発注情報

3 概要

uA9638 は、ANSI 標準 EIA/TIA-422-B を満たすように設計されたデュアル高速差動ライン ドライバです。入力は TTL および CMOS 互換であり、入力クランプ ダイオードを備えています。伝搬遅延時間を最小化するため、ショットキー ダイオードでクランプされたトランジスタを使用しています。このデバイスは 5V 単一電源で動作し、8 ピン パッケージで供給されます。

uA9638 は、低インピーダンス負荷を高速で駆動するために必要な電流を出力します。通常、ツイストペア ケーブルおよび差動レシーバと組み合わせて使用することで、適切に設計されたシステムにおいて、最大 15Mbps 以上のベースバンド データ伝送を達成できます。通常、uA9637A デュアル ライン レシーバが、レシーバとして使用されます。同じピン構成でさらに高速なスイッチング速度が必要な場合、SN75ALS191 を参照してください。

uA9638 は、0℃~70℃で動作特性が規定されています。

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

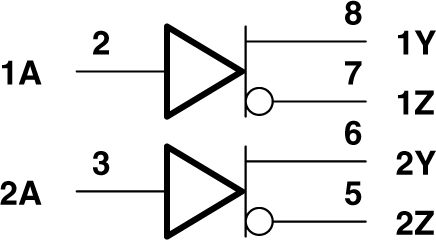

論理記号(1)

論理記号(1) ロジック図

ロジック図†. この記号は ANSI/IEEE 規格 91-1984 と IEC Publication 617-12 に準拠しています。