JAJSGJ2D October 2018 – November 2024 UCC21530

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 アプリケーションと実装

- 9 電源に関する推奨事項

- 10レイアウト

- 11デバイスおよびドキュメントのサポート

- 12改訂履歴

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DWK|14

サーマルパッド・メカニカル・データ

発注情報

8.2.3 アプリケーション曲線

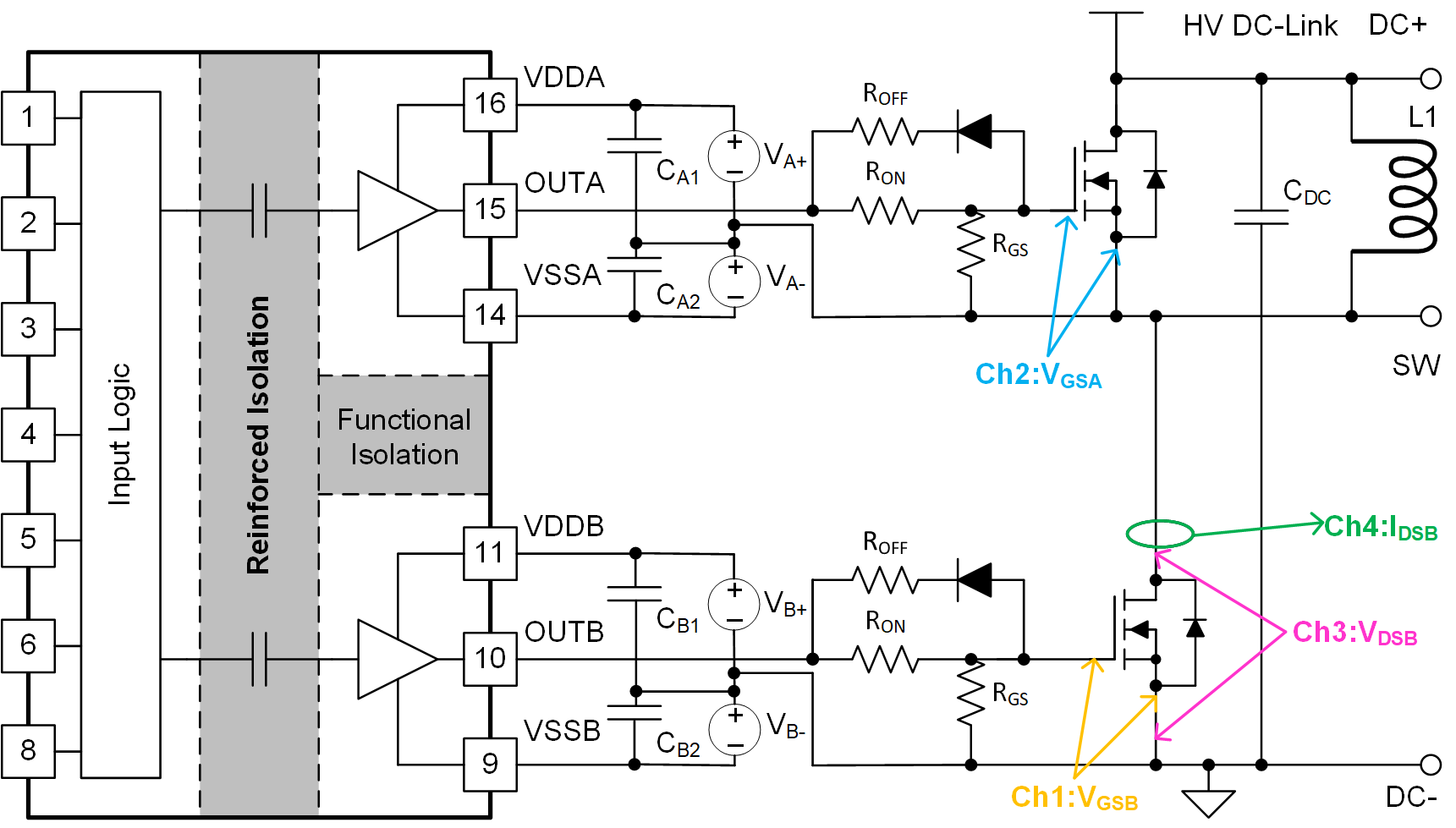

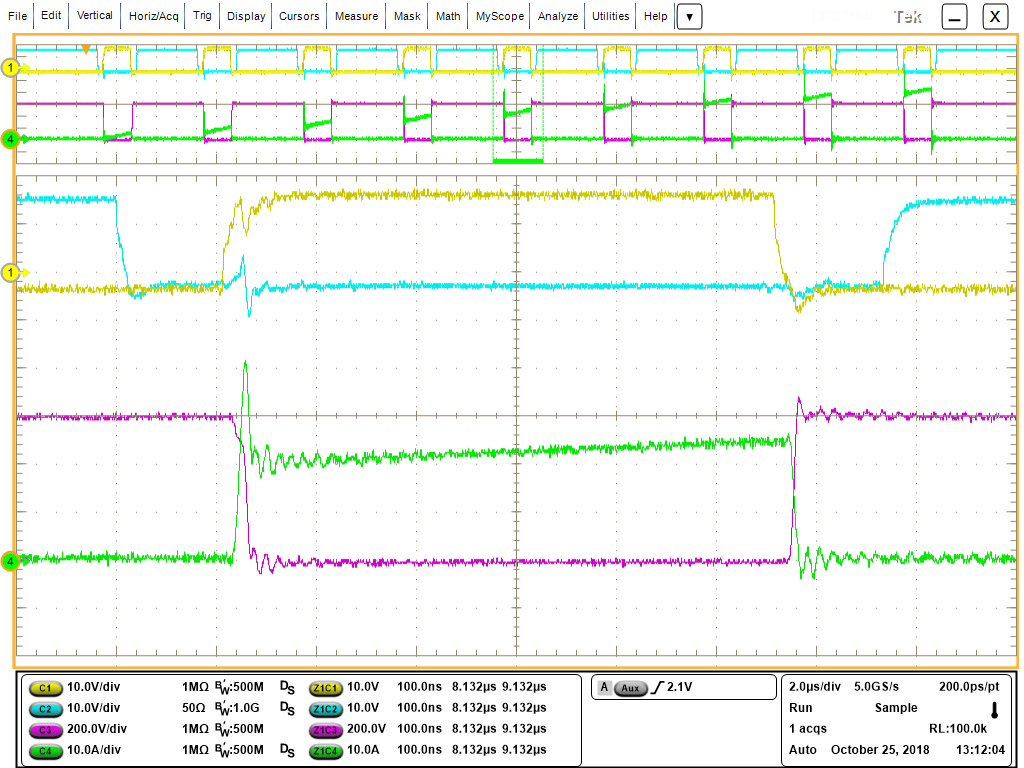

図 8-5 に、インダクタ負荷として L1 を使用する複数パルスのベンチ テスト回路を示します。また、ドライバと SiC MOSFET のスイッチング過渡をさまざまな負荷条件のもとで評価するため、制御パルスのグループが生成されます。テスト条件は次のとおりです。VDC-Link = 600V、VCC = 5V、VDD = 15V、VSS = -4V、fSW = 500kHz、RON = 5.1Ω、ROFF = 1.0Ω。約 20A の電流でのオン/オフ波形を、図 8-6 に示します。

チャネル 1 (黄):ローサイド MOSFET のゲートとソースの間の電圧信号。

チャネル 2 (青):ハイサイド MOSFET のゲートとソースの間の電圧信号。

チャネル 3 (ピンク):ローサイド MOSFET のドレインとソースの間の電圧信号。

チャネル 4 (緑):ローサイド MOSFET のドレインとソースの間の電流信号。

図 8-6 で、ハイサイドとローサイドのパワー トランジスタのゲート駆動信号のデッドタイムは 100ns で、どちらの信号も 500MHz 以上の帯域幅を持つプローブで測定されます。

図 8-5 SiC MOSFET スイッチングを使用したベンチ テスト回路

図 8-5 SiC MOSFET スイッチングを使用したベンチ テスト回路 図 8-6 SiC MOSFET のスイッチング波形

図 8-6 SiC MOSFET のスイッチング波形