JAJSIQ6D June 2020 – August 2024 UCC21540-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 デバイス比較表

- 5 ピン構成および機能

- 6 仕様

- 7 パラメータ測定情報

- 8 詳細説明

-

9 アプリケーションと実装

- 9.1 アプリケーション情報

- 9.2 代表的なアプリケーション

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13改訂履歴

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DWK|14

サーマルパッド・メカニカル・データ

発注情報

9.2.3 アプリケーション曲線

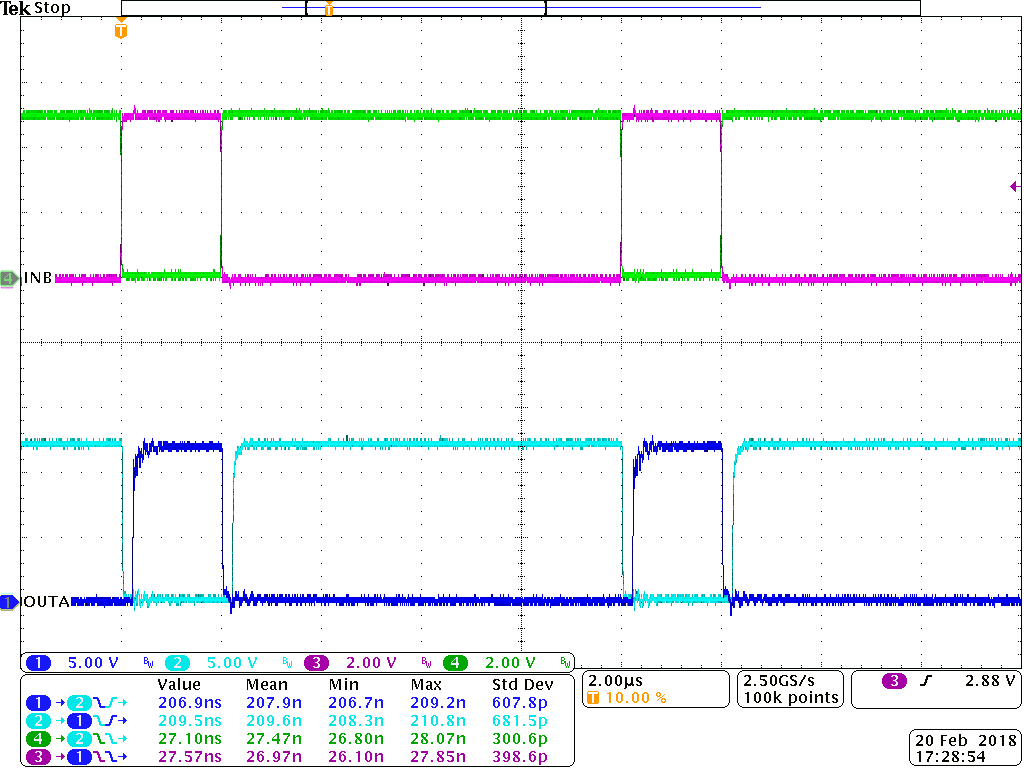

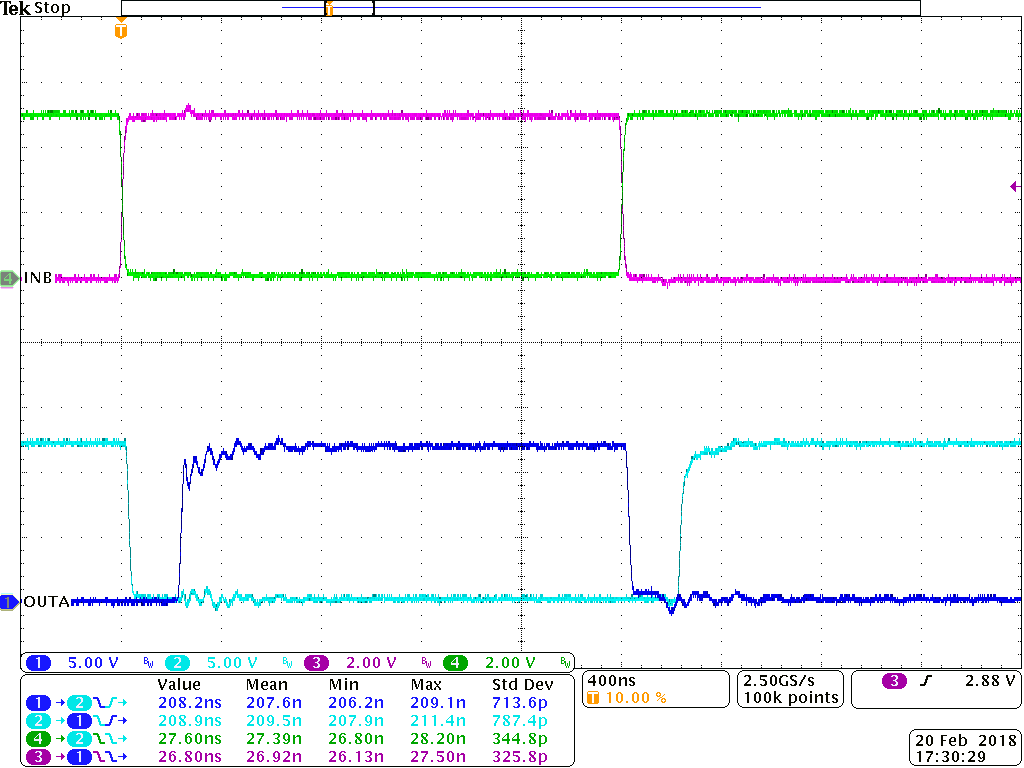

図 9-5 と図 9-6 に、図 9-1 に示す設計例の以下の条件におけるベンチ・テスト波形を示します。VCC = 5.0V、VDD = 12V、fSW = 100kHz、VDC-Link = 400V。

チャネル 1 (青):ハイサイド・パワー・トランジスタのゲート - ソース間の信号

チャネル 2 (シアン):ローサイド・パワー・トランジスタのゲート - ソース間の信号

チャネル 3 (ピンク):INA ピンの信号

チャネル 4 (緑)INB ピンの信号

図 9-5 で、INA と INB に 3.3V、20%/80% デューティ・サイクルの相補信号が印加されています。パワー・トランジスタのゲート駆動信号には 200ns のデッド・タイムが挿入されており、DC リンクには 400V の高電圧が印加されています (図 9-5 の測定部を参照)。高電圧が印加されている場合、帯域幅がより狭い差動プローブが使われるため、達成可能な測定精度が制限されることに注意します。

図 9-6 に、図 9-5 の波形の拡大図と、伝搬遅延とデッド・タイムの測定値を示します。出力波形はパワー・トランジスタのゲート・ピンとソース・ピンの間で測定され、ドライバの OUTA ピンと OUTB ピンからは直接測定されないことに注意します。